基于ARM和Ethernet的現場實時信號采集分析系統

1信號分析系統硬件框架

圖1 數采分析儀系統結構圖

數據采集分析儀系統結構圖見圖1,從功能上看,它由信號采集與處理、以太網數據通訊兩大部分組成。

1.1 數據采集與信號處理

為了增強系統的數據采集與信號處理能力,采用了ARM+DSP主從結構。ARM采用三星公司的S3C4510B作為主處理器,完成系統管理及網絡通訊。DSP采用TI公司的TMS320VC5416作為協處理器,完成信號處理、分析包括FFT、互譜、平均等信號處理任務及特征抽取任務。這樣的任務劃分有利于讓主從處理器都能充分發揮處理能力,從而使系統的數據采集與信號處理能力達到最大。其增強的外部存儲器接口,使得對外部數據的預處理更加方便,存儲器接口電路的設計也更靈活,因此在實時數據采集和信號處理系統中得到了應用。

1.2 以太網數據通訊

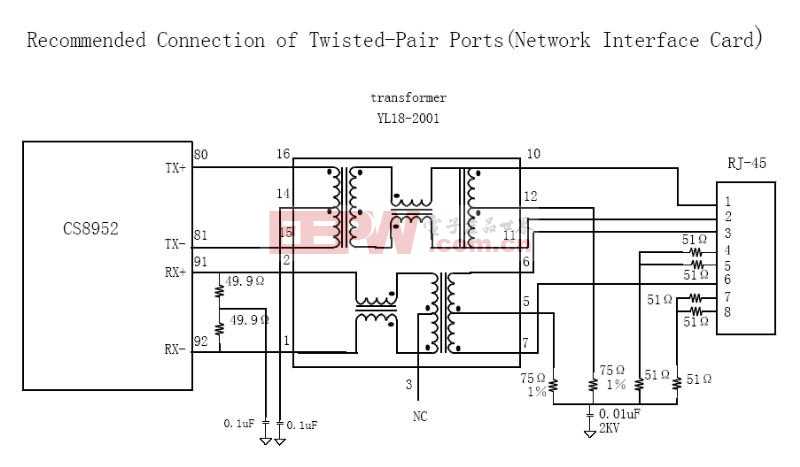

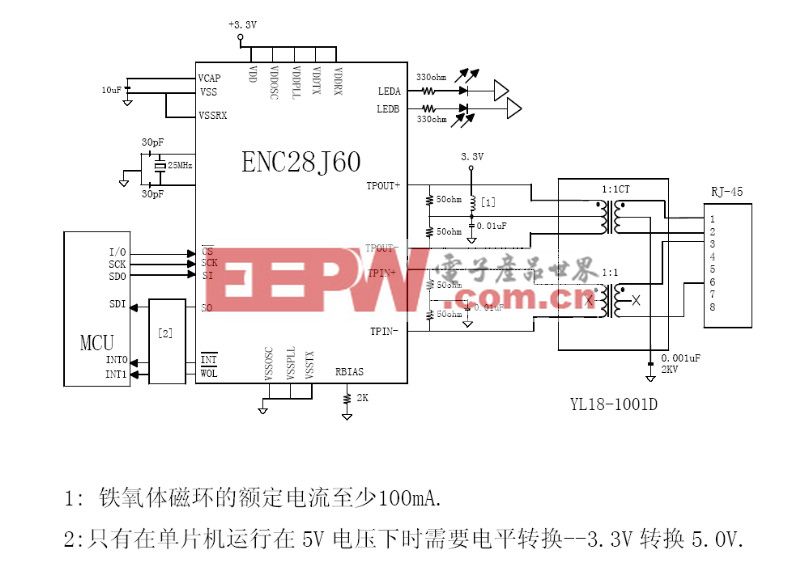

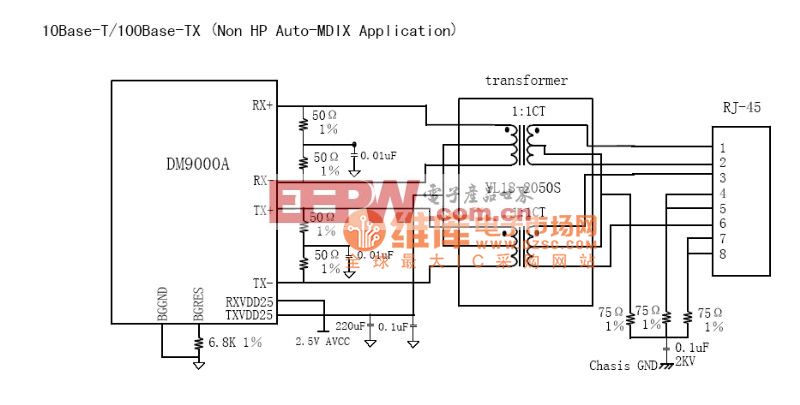

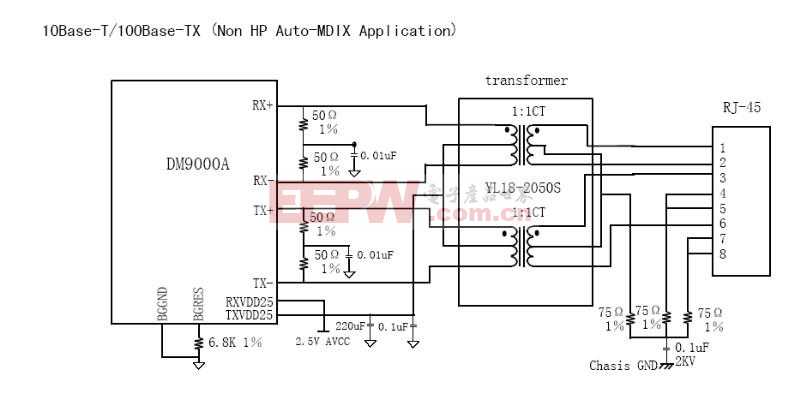

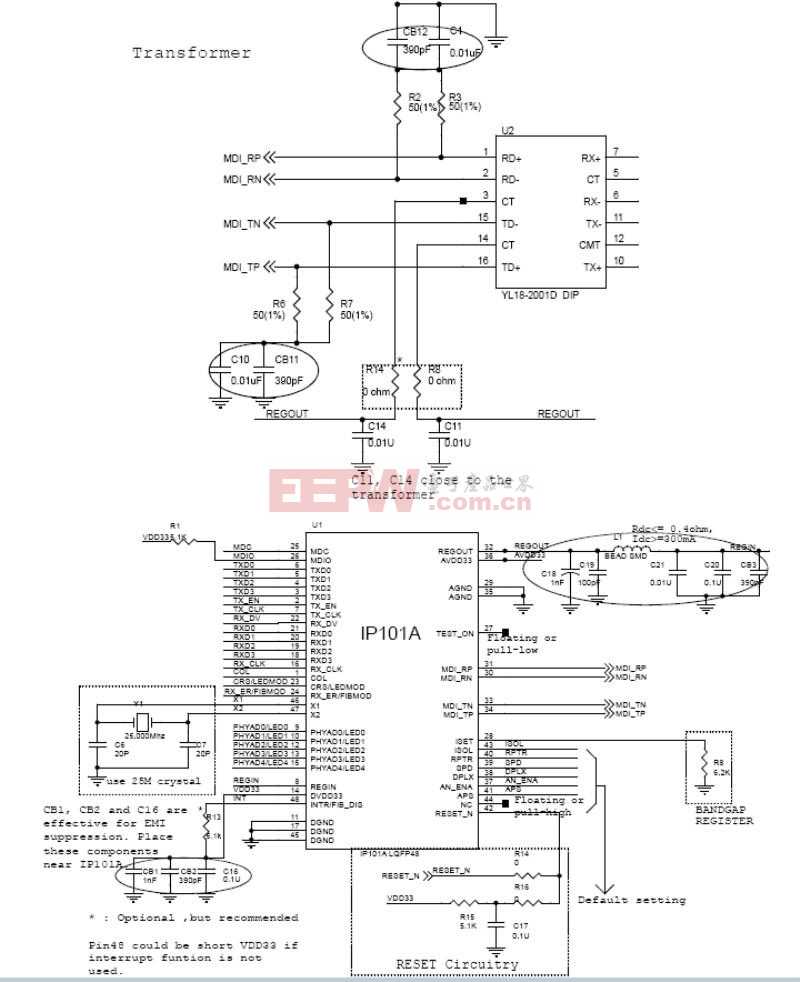

系統控制器向外提供1個10M/100M以太網口,通過寬帶可以接入Internet或局域網;S3C4510B內嵌一個可以以10M/100M的速率工作在半雙工或全雙工模式下的以太網控制器,其MAC層支持媒體獨立接口(MII)和帶緩沖的DMA接口(BDI)。MAC層由發送模塊、接收模塊、流控模塊、用于存儲網絡地址的匹配地址存儲器(CAM)以及一些命令寄存器、狀態寄存器、錯誤計數器寄存器構成。MII支持在25MHz時鐘下以100M速率的發送與接收操作,和在2.5MHz時鐘下以10M速率的發送與接收操作。特別適用于通訊和網絡產品。TCP/IP協議的使用將提高基于以太網的通訊軟件實現的可靠性來降低其復雜度。在主處理器內嵌的uClinux帶有一個完整的TCP/IP協議,同時它還支持許多其他網絡協議。uClinux對于嵌入式系統來說是一個網絡完備的操作系統。

1.3 主從模塊通訊接口設計

主從處理器之間應盡量加快通訊速度,并保持可靠性和實時性。uClinux需要讀取數據處理模塊中的RAM,所以最好是把數據處理模塊中的RAM作為uClinux的內存地址的一部分,采用HPI技術可以滿足此要求。用Altera公司的FPGA芯片EP1C6作為系統的邏輯控制單元及主從系統配置電路,完成TMS320C5416與ARM處理器相關控制連接。

從系統硬件采用TI公司的TMS320C5416作信號處理器,用Altera公司的FPGA芯片EP1C6作為系統的邏輯控制單元及主從系統配置電路,同時利用HPI技術,完成TMS320C5416與ARM處理器S3C4510B的數據交換。

C5416與S3C4510B接口簡單,DSP通過HPI8與主機設備相連時,除了8位HPI數據總線及控制信號線外,不需更多地附加其它邏輯電路,只需將C5416控制的引腳和S3C4510B的GPIO口引腳相連,這樣對C5416的控制就只需設置相應的GPIO口線即可。

在嵌入式系統設計中,用S3C4510B作為主控制器,用C5416進行數據采集運算處理,然后通過HPI8接口進行數據通信。試驗表明,用HPI接口技術在C5416和S3C4510B間實現通信滿足嵌入式系統的實時性要求。

評論