紅外動目標識別跟蹤系統的實現

2 輸入輸出緩沖FIFO

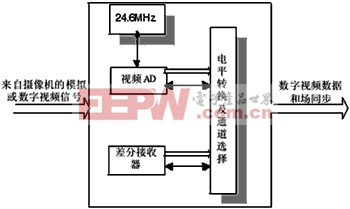

設置輸入輸出緩沖FIFO的目的是在高速器件和低速器件之間設置一個緩沖區,可以避免高速器件因等待低速器件的數據而使系統的效率降低。A/D芯片送出的數字信號的時鐘頻率約為12MHz(模擬通道時鐘12.51MHz,數字通道時鐘12MHz),而處理卡上DSP的總線頻率高達50MHz,兩者差異較大,所以采用輸入輸出緩沖FIFO是必要的。基于以上考慮,最終選用Cypress公司的CY7C4275。它的容量為32K×18,最大存取速度可達到l0ns。

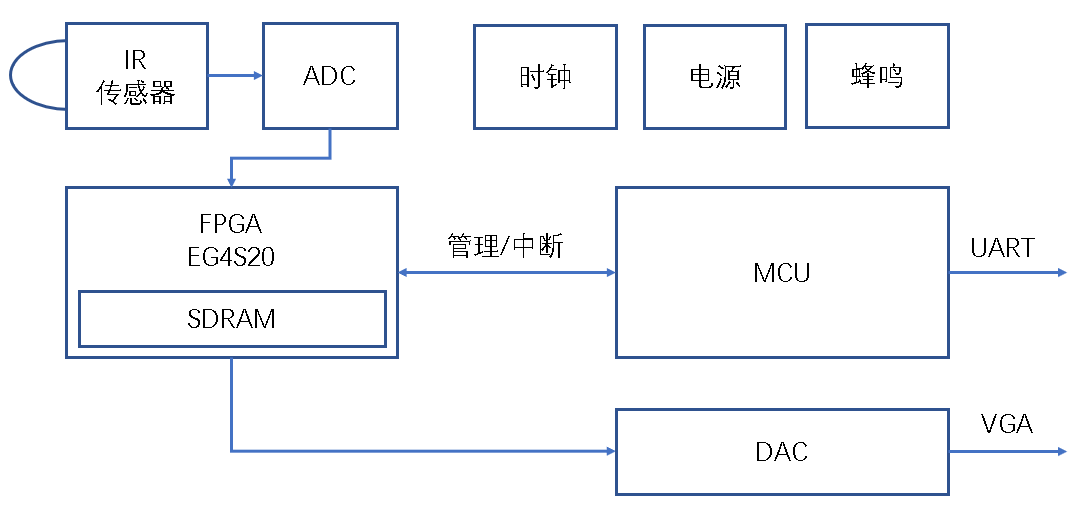

3 可編程控制器(FPGA)

在本系統中,FPGA控制了絕大部分單元,包括通道選擇/電平轉換芯片、輸入輸出 FIFO、SRAM、DSP、PCI接口電路等。利用FPGA芯片的系統內可編程(ISP)性能,完成所有DSP外圍芯片的控制邏輯;并在其中設置狀態寄存器、命令字寄存器和專用寄存器,完成與主機的實時通信,接收主機傳送的命令信息和向主機傳送所需要的狀態信息。

在本系統中,數字信道為14bit,模擬為8bit,需要由FPGA對信號進行第一次裝配(區別于DSP為了顯示而對圖像按FGB格式進行的第二次裝配),即將數字/模擬信號/數據均轉換為16bit的數據,然后將兩個16bit數據裝配成一個32bit的數據。

4數字圖像存儲器(SRAM)

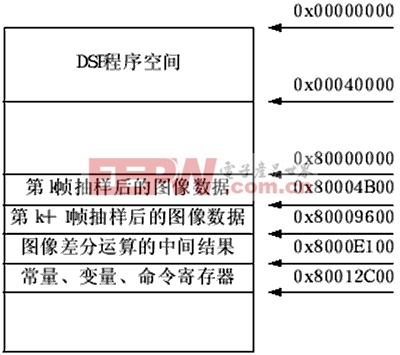

紅外動目標識別與跟蹤系統要完成對運動目標的識別與跟蹤。其實現算法必然涉及到對多幀(差分處理,至少兩幀)視頻圖像的處理。為了給實現算法提供較為充裕的存儲空間,我們選用的存儲器能容納6場視頻圖像。因此,最后選用的存儲器是Giga SemIConductor公司的兩片GS74116,其每片容量為256K×16bit,存取速度為15ns。考慮到我們視頻圖像每場的數據量為76800像素,兩片512K的SRAM可以存下至少6張視頻圖像。在本系統中,我們設置了4幀圖像存儲空間,其余空間用于存放目標小圖、DSP裝配數據等,數據空間具體地址分配如圖4所示。

圖4 SRAM數據空間分配

5 數字圖像處理模塊(DSP)

DSP采用TI公司的TMS320C6202芯片。我們采用隔點、隔行的亞抽樣。抽樣后,每幀圖像大小約為20KB,總計約需80KB的數據空間,TMS320C6202的片內數據空間足夠所需。我們對DSP芯片的內部空間分配如圖5所示。

圖5 DSP內部空間分配

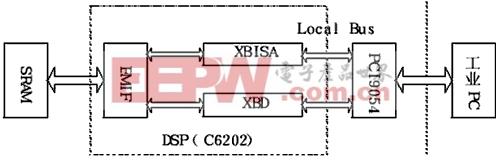

6 PCI接口電路

由于本系統與PC的接口是PCI接口。為了避免受困于PCI接口繁雜的數據傳送協議,充分發揮PCI總線的數據傳送能力,PCI接口電路采用PCI9054芯片。它是PCI總線專用接口芯片,具有數據傳送快、數據傳送簡單等優點。在33MHz的PCI總線工作頻率下,它的最大數據吞吐能力為132MB/s。

PCI9054與DSP的數據交換或通信是通過DSP芯片內部的兩個寄存器實現的,即地址寄存器XBISA;數據寄存器XBD。對PCI9054及DSP芯片而言,它們互相并不能直接訪問對方的資源,數據交換必須由這兩個寄存器中繼,如圖6所示。

圖6 PCI9054與DSP連接圖

系統軟件設計

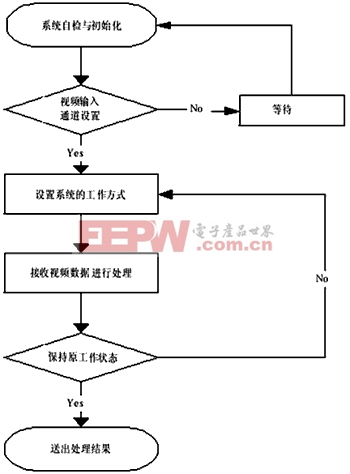

首先進行系統上電自檢,查看系統各部分是否進入正常工作狀態,并將檢測結果送往主機。然后對整機系統進行初始化工作,檢測命令字寄存器確定圖像的輸入方式和系統的工作方式,若主機未指定,則進入等待狀態,直到操作員指定系統的工作方式為止,系統進入正常工作。系統軟件流程圖如圖7所示。

評論