常用EDA設計與仿真軟件介紹

3、IC設計軟件

IC設計工具很多,其中按市場所占份額排行為Cadence、Mentor Graphics和Synopsys。這三家都是ASIC設計領域相當有名的軟件供應商。其它公司的軟件相對來說使用者較少。中國華大公司也提供ASIC設計軟件(熊貓2000);另外近來出名的Avanti公司,是原來在Cadence的幾個華人工程師創立的,他們的設計工具可以全面和Cadence公司的工具相抗衡,非常適用于深亞微米的IC設計。下出按用途對IC設計軟件作一些介紹。

(1)設計輸入工具

這是任何一種EDA軟件必須具備的基本功能。像Cadence的Composer,Viewlogic的Viewdraw,硬件描述語言VHDL、Verilog HDL是主要設計語言,許多設計輸 入工具都支持HDL。另外像Active—HDL和其它的設計輸入方法,包括原理和狀態機輸入方法,設計FPGA/CPLD的工具大都可作為IC設計的輸入手段,如Xilinx、Altera等公司提供的開發工具,Modelsim FPGA等。

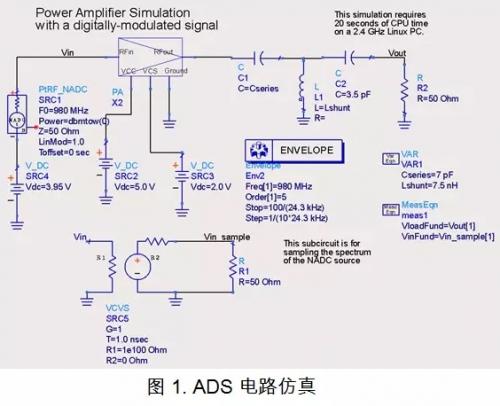

(2)設計仿真工作

我們使用EDA工具的一個最大好處是可以驗證設計是否正確,幾乎每個公司的EDA 產品都有仿真工具。Verilog—XL、NC—Verilog用于Verilog仿真,Leapfrog用于VHDL仿真,Analog Artist用于模擬電路仿真。Viewlogic的仿真器有:Viewsim門級電路仿真器,SpeedwaveVHDL仿真器,VCS—Verilog仿真器。Mentor Graphics有其子公司Model Tech 出品的VHDL和Verilog雙仿真器:Model Sim。Cadence、Synopsys用的是VSS(VHDL仿真器)。現在的趨勢是各大EDA公司都逐漸用HDL仿真器作為電路驗證的工具。

(3)綜合工具

綜合工具可以把HDL變成門級網表。這方面Synopsys工具占有較大的優勢,它的Design Compile是作綜合的工業標準,它還有另外一個產品叫Behavior Compiler,可以提供更高級的綜合。另外最近美國又出了一家軟件叫Ambit,說是比Synopsys的軟件更有效,可以綜合50萬門的電路,速度更快。今年初Ambit被Cadence公司收購,為此Cadence放棄了它原來的綜合軟件Synergy。隨著FPGA設計的規模越來越大,各EDA公司又開發了用于FPGA設計的綜合軟件,比較有名的有:Synopsys的FPGA Express,Cadence的Synplity,Mentor的Leonardo,這三家的FPGA綜合軟件占了市場的絕大部分。

(4)布局和布線

在IC設計的布局布線工具中,Cadence軟件是比較強的,它有很多產品,用于標準單元、門陣列已可實現交互布線。最有名的是Cadence Spectra,它原來是用于PCB布線的,后來Cadence把它用來作IC的布線。其主要工具有:Cell3,Silicon Ensemble—標準單元布線器;Gate Ensemble—門陣列布線器;Design Planner—布局工具。其它各EDA軟件開發公司也提供各自的布局布線工具。

(5)物理驗證工具

物理驗證工具包括版圖設計工具、版圖驗證工具、版圖提取工具等等。這方面Cadence也是很強的,其Dracula、Virtuso、Vampire等物理工具有很多的使用者。

(6)模擬電路仿真器

前面講的仿真器主要是針對數字電路的,對于模擬電路的仿真工具,普遍使用SPICE,這是唯一的選擇。只不過是

c++相關文章:c++教程

評論