DSP+FPGA的機載總線接口板研究(二)

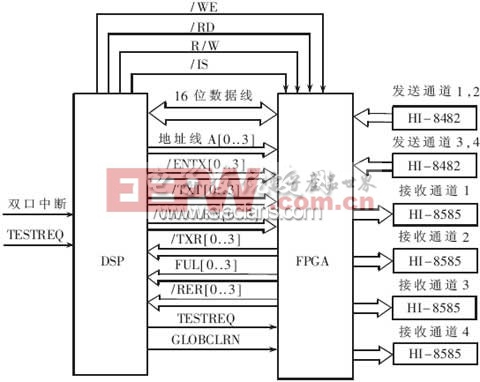

圖6 DSP與FPGA的連接示意圖

DSP提供I/O操作信號/IS、讀寫選定信號R/W、讀使能信號/RD、寫使能信號/WE以及地址線低四位A0、A1、A2、A3。通過這些控制邏輯信號可區分四路通道及每路通道的高低字。

DSP和FPGA提供的其它輔助的控制和狀態信號還包括:四路發送使能信號/ENTX[03],低電平有效;四路發送停止信號/TXT[03],低電平有效;接收數據到達信號/RER[03],用于告知DSP準備接收某一路通道已經到達的數據;發送數據準備好信號/TXR[03]信號,用于告知各個發送通道中是否還有未發出的數據暫存在FIFO里,低電平表示沒有數據;發送通道FIFO滿信號FUL[03],高電平有效;GLOBCLRN信號,用于FPGA初始化時對其內部進行全局清零;TESTREQ信號,用于對整個系統的自檢。

整個電路板是通過雙口RAM與外設主機進行通信的,雙口RAM負責暫存外設要發送的數據和暫存FPGA處理過的數據。可把它大致分為8個區,每一個區負責存放四路接收通道和四路發送通道中的一路數據及控制字。利用雙口RAM左右兩中斷的信箱可指揮接口板進行相應的操作。4 軟件設計

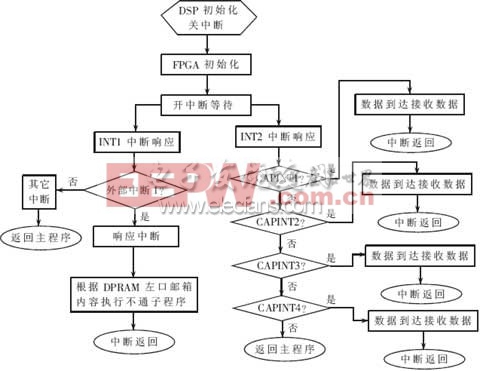

軟件的設計主要是DSP編程,DSP程序的主要任務就是初始化、管理DSP外圍電路、控制FPGA的收發數據以及與外設交互。DSP的主程序流程圖如圖7所示。

圖7 DSP主程序流程圖

整個接口電路板調試通過后,經過測試可以同時接收和發送四路ARINC429信號。這就解決了以往接口電路板通道數太少的瓶頸。

本系統利用FPGA密度高、結構靈活、設計時間短和可編程的優點,實現了對某路ARINC429信號的獨立處理,實現了對FPGA的控制管理及與外設的通信。

評論