DSP+FPGA的機載總線接口板研究(二)

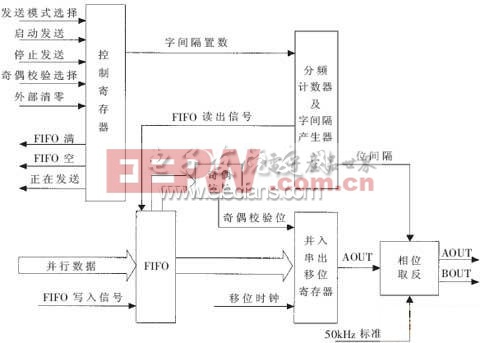

圖4 發送模塊結構框圖

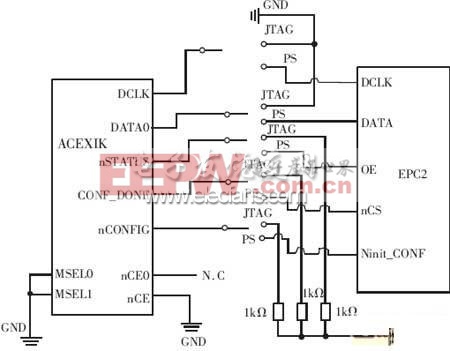

FPGA內部結構是基于SRAM的,因此需要一片配置芯片固化內部邏輯。為了便于調試,采用JTAG模式和被動串行模式(PS)兩種配置模式,調試時使用JTAG模式直接將邏輯寫入FPGA內部,調試好后再用PS模式將程序寫入配置芯片。通過對FPGA和配置芯片上的引腳進行跳線,可選擇不同的配置方式。跳線電路如圖5所示。

圖5 FPGA配置跳線設置

FPGA作為DSP的一個I/O外設,必然要對它的寄存器地址統一編址。在此將FPGA編址在DSP的I/O空間。由于FPGA的接收通道和發送通道是共用DSP的16位數據線的,故接收通道和發送通道的數據寄存器可以占用一個地址。表1是FPGA各通道寄存器分配的地址。

表1 FPGA內部各通道寄存器地址

3.3 DSP與FPGA及外部設備的通信

DSP(digital signal processor)是一種獨特的微處理器,是以數字信號來處理大量信息的器件。其工作原理是接收模擬信號,轉換為0或1的數字信號。再對數字信號進行修改、刪除、強化,并在其他系統芯片中把數字數據解譯回模擬數據或實際環境格式。它不僅具有可編程性,而且其實時運行速度可達每秒數以千萬條復雜指令程序,遠遠超過通用微處理器,是數字化電子世界中日益重要的電腦芯片。它的強大數據處理能力和高運行速度,是最值得稱道的兩大特色。

評論