采用緊湊式SIP的QFN封裝

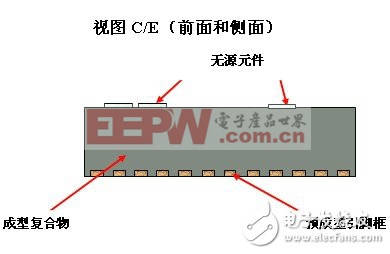

圖 6 “采用緊湊式 SIP 的 QFN 封裝”的不同視圖【視圖C/E(前面和側面)】

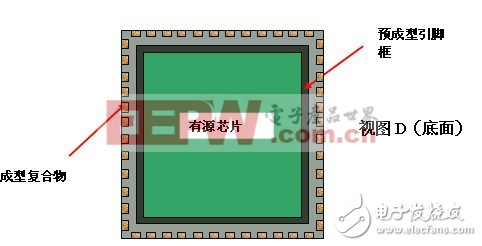

圖 7 “采用緊湊式 SIP 的 QFN 封裝”的不同視圖【視圖D(底面)】

優點:

封裝設計理念

在 QFN 中集成 SIP 是全新的封裝理念,具有緊湊、集成度高的特點(可集成更多的無源元件和芯片)。此設計可在內部集成具有不同功能的有源元件和無源元件,降低成本和縮短上市時間,成為最受青睞的封裝技術之一。此外,該封裝設計可更換不同的無源元件或芯片,從而實現不同的 BOM 組合,有助于封裝產品的升級。

產品性能和應用

與傳統的需要采用印刷電路板的 SIP 封裝相比。“采用緊湊式 SIP 的 QFN 封裝”設計采用了堆疊概念,可使芯片 I/O 接線、無源元件、有源芯片等的距離達到最小。此設計可直接改善開關頻率、信號,且有助于改善產品性能/效率。例如:DrMOS 應用 à 無源元件應盡可能地靠近 HS 芯片的漏極和 LS 芯片的源極,如此才能實現更高的 DC/DC 轉換器效率。

突破封裝/產品的靈活性和可擴展性的限制

當前市場中的 SIP :在成型封裝中固定和封裝的無源元件、功能性芯片和 CSP 產品 à 靈活性差,在集成厚度較大的元件時需要采用新封裝尺寸。對于“采用緊湊式 SIP 的 QFN 封裝”設計而言:可采用多種厚度的芯片、CSP 產品、無源元件及其他功能芯片,不受限于總封裝厚度。可根據客戶應用或需求,以“拾取放置”(pick place) 方式更換無源元件、CSP 產品及其他功能芯片。由于采用暴露元件/“開放式”封裝理念,對于芯片、CSP 產品、無源元件或其他功能芯片無嚴格厚度限制。開發工作量少,上市時間短,封裝靈活性高。

工藝簡化

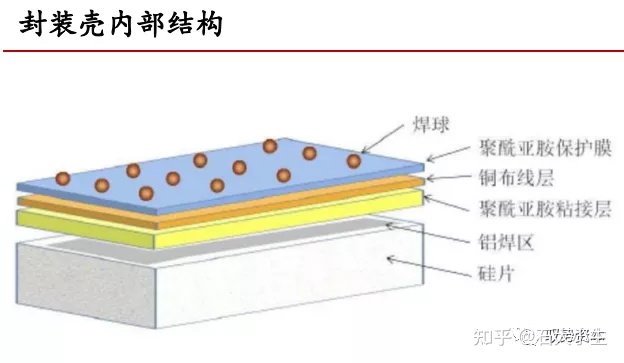

由于采用的是倒裝芯片設計,封裝時無需采用焊線和成型工藝。總體而言,這將極大地簡化整體工藝。

可靠性高

由于采用了預成型引腳框,且其為“開放式”,因此無需擔心成型復合物和無源元件/硅芯片表面之間的 CTE (熱膨脹系數)不匹配問題。無源元件和引腳框之間的間隙極小,不存在封裝氣孔的問題。無源元件與引腳框之間(如 I/O 區域)的細小間隙通常會導致形成微小氣孔。在壓力測試過程中,孔內的空氣可能會導致“爆米花”效應。

熱性能增強

對于高發熱量芯片應用,可在有源芯片的背面涂覆額外的高性能導熱膏,從而增強熱性能。熱量傳導路徑為:有源芯片 à 高性能導熱膏 à 印刷電路板

以下說明“采用緊湊式 SIP 的 QFN

評論