PLA及其應用

在使用ROM時,由于它的地址譯碼器是固定的,因此不能對函數進行化簡,從而多占了ROM芯片的面積。為了解決這個問題,我們就使用可以對函數進行化簡的器件——PLA

PLA

PLA是能夠編程的邏輯器件。它能夠對邏輯"與"、"或"陣列進行編程,利用PLA,可以很方便的實現組合邏輯和時序邏輯。

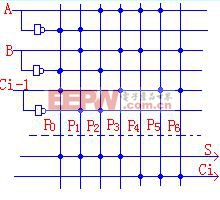

例:1 用PLA實現一位二進制全加器

全加器的最簡邏輯表達式為(參見第四章第三節):

S=ABCi-1+ABCi-1+ABCi-1+ABCi-1

Ci=AB+ACi-1+BCi-1

該式中共有七個乘積項,它們是:

P0=ABCi-1 P1=ABCi-1 P2=ABCi-1 P3=ABCi-1

P4=AB P5=ACi-1 P6=BCi-1

根據上述,可得出PLA全加器的陣列結構圖為:如圖(1)所示

由此可見:PLA相當于"與""或"陣列均可編程的ROM.

評論