以太網PHY、MAC及其通信接口入門

本文主要介紹以太網的 MAC 和 PHY,以及之間的 MII(Media Independent Interface ,媒體獨立接口)和 MII 的各種衍生版本——GMII、SGMII、RMII、RGMII等。

本文引用地址:http://www.j9360.com/article/202504/469606.htm簡介

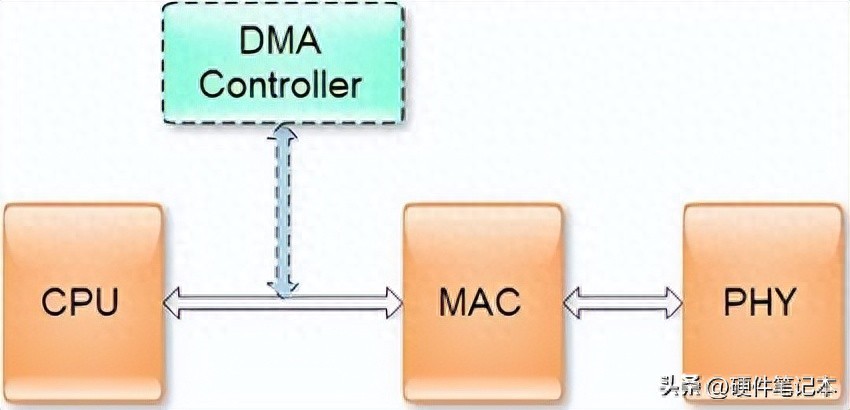

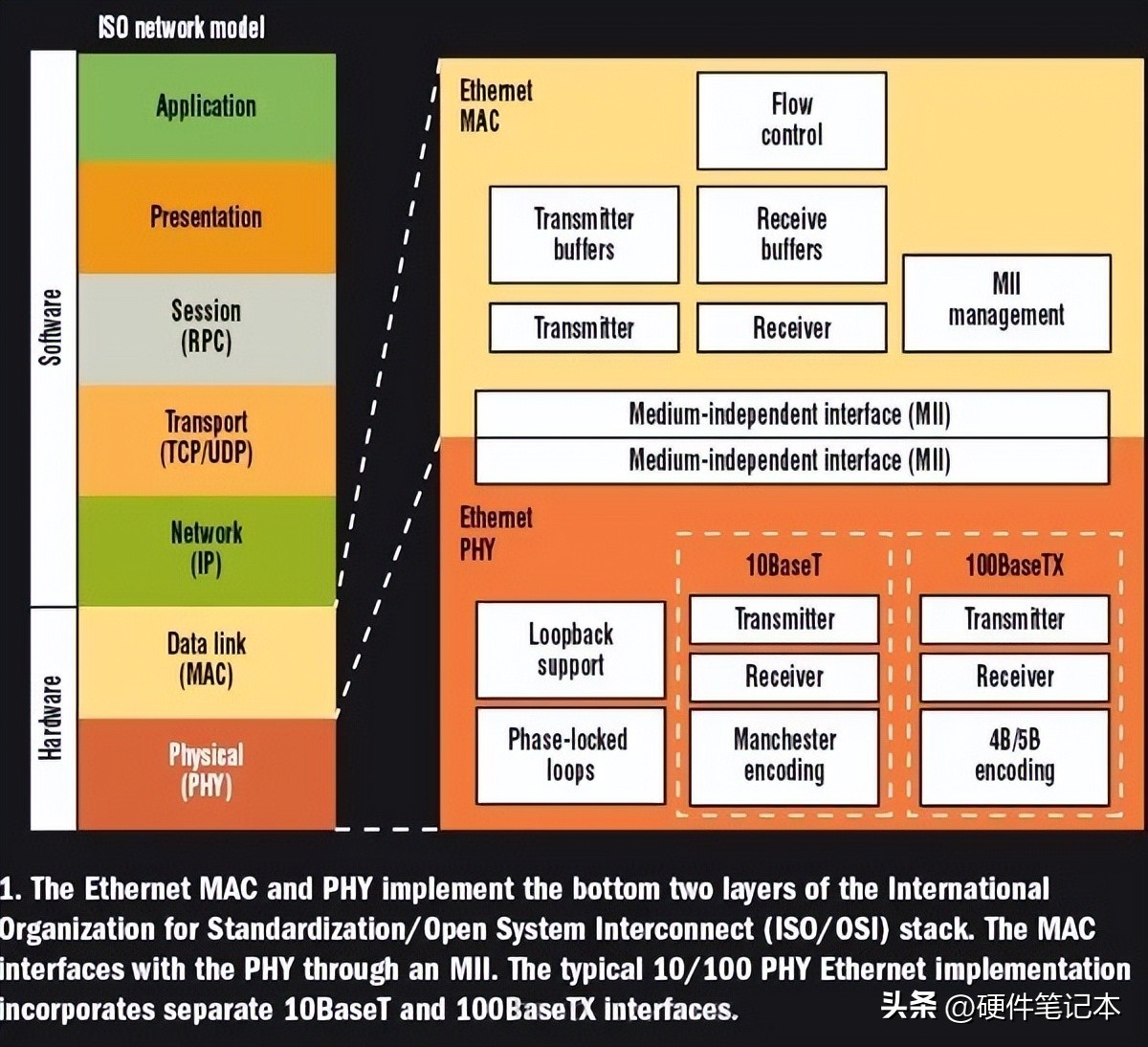

從硬件的角度看,以太網接口電路主要由MAC(Media Access Control)控制器和物理層接口PHY(Physical Layer,PHY)兩大部分構成。如下圖所示:

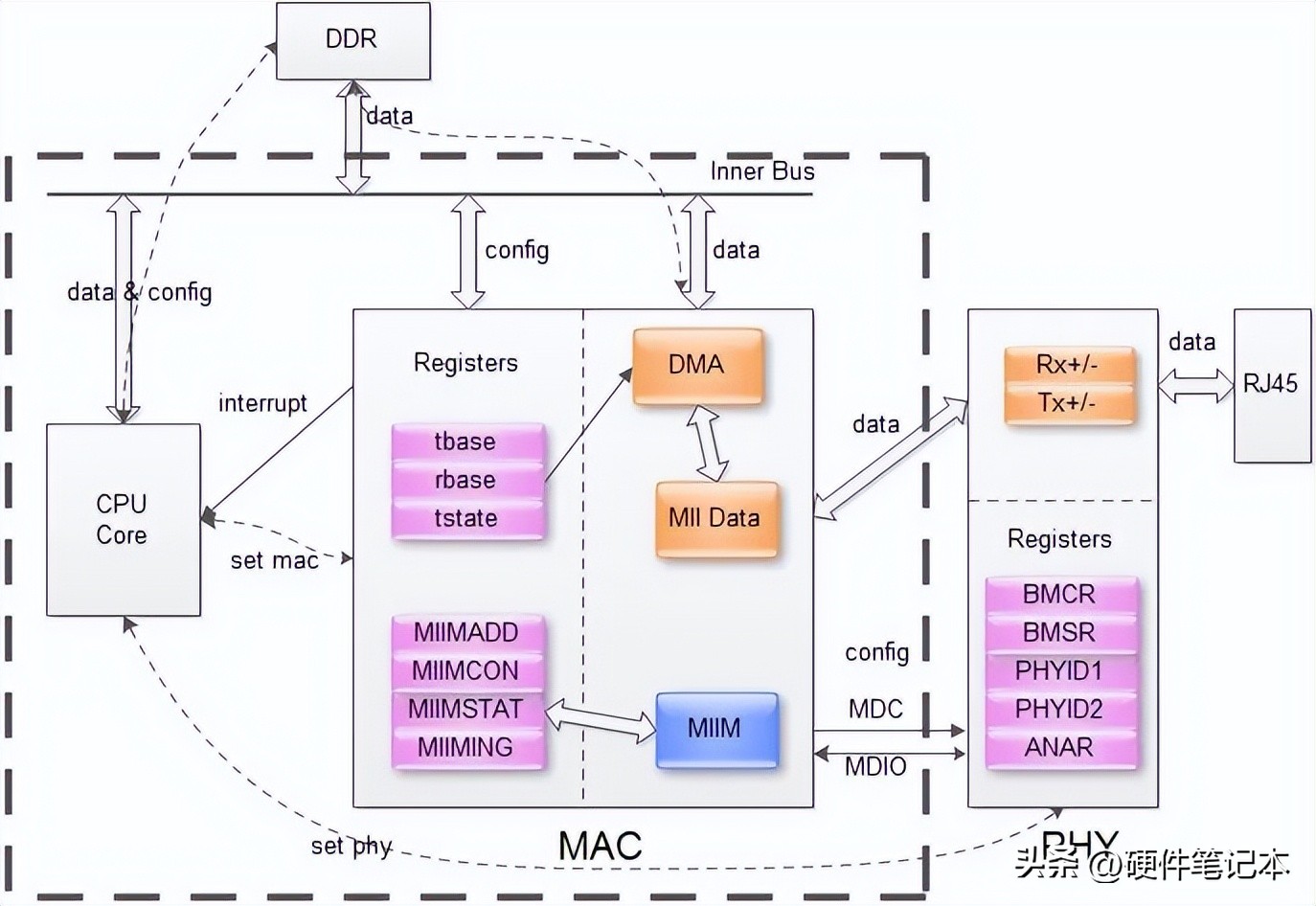

DMA控制器通常屬于CPU的一部分,用虛線放在這里是為了表示DMA控制器可能會參與到網口數據傳輸中。但是,在實際的設計中,以上三部分并不一定獨立分開的。由于,PHY整合了大量模擬硬件,而MAC是典型的全數字器件。

考慮到芯片面積及模擬/數字混合架構的原因,通常,將MAC集成進微控制器而將PHY留在片外。更靈活、密度更高的芯片技術已經可以實現MAC和PHY的單芯片整合。

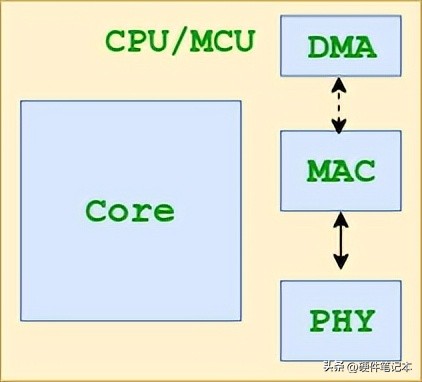

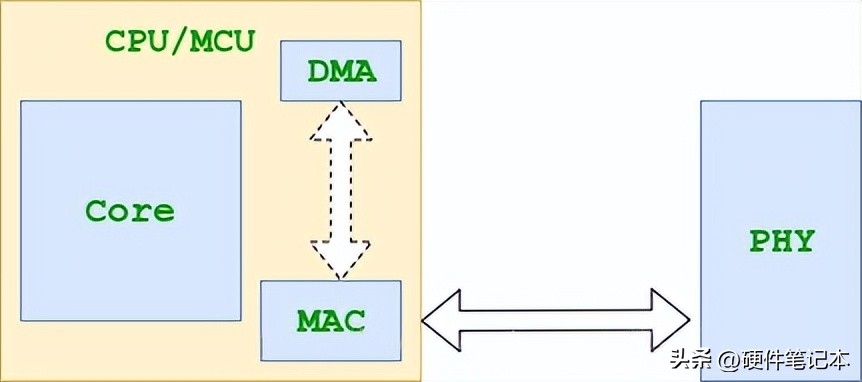

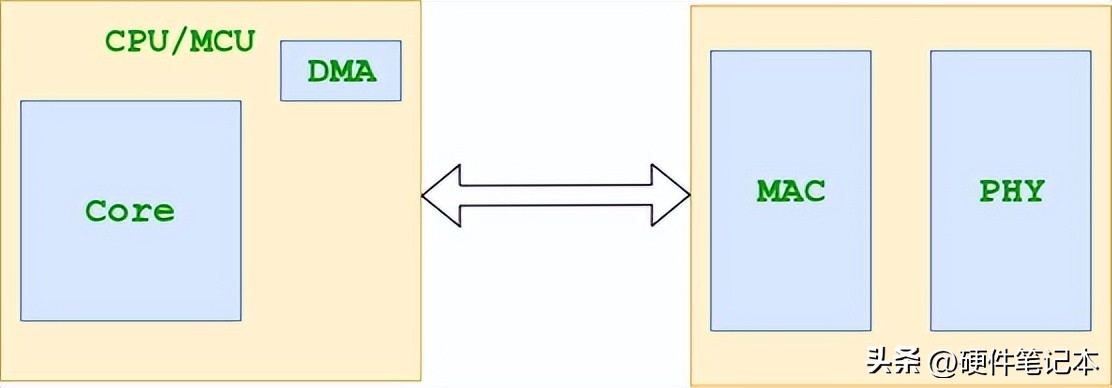

可分為下列幾種類型:

CPU集成MAC與PHY。目前來說并不多見

CPU集成MAC,PHY采用獨立芯片。比較常見

CPU不集成MAC與PHY,MAC與PHY采用集成芯片。比較常見

MAC及PHY工作在OSI七層模型的數據鏈路層和物理層。具體如下:

什么是MAC

MAC(Media Access Control)即媒體訪問控制子層協議。

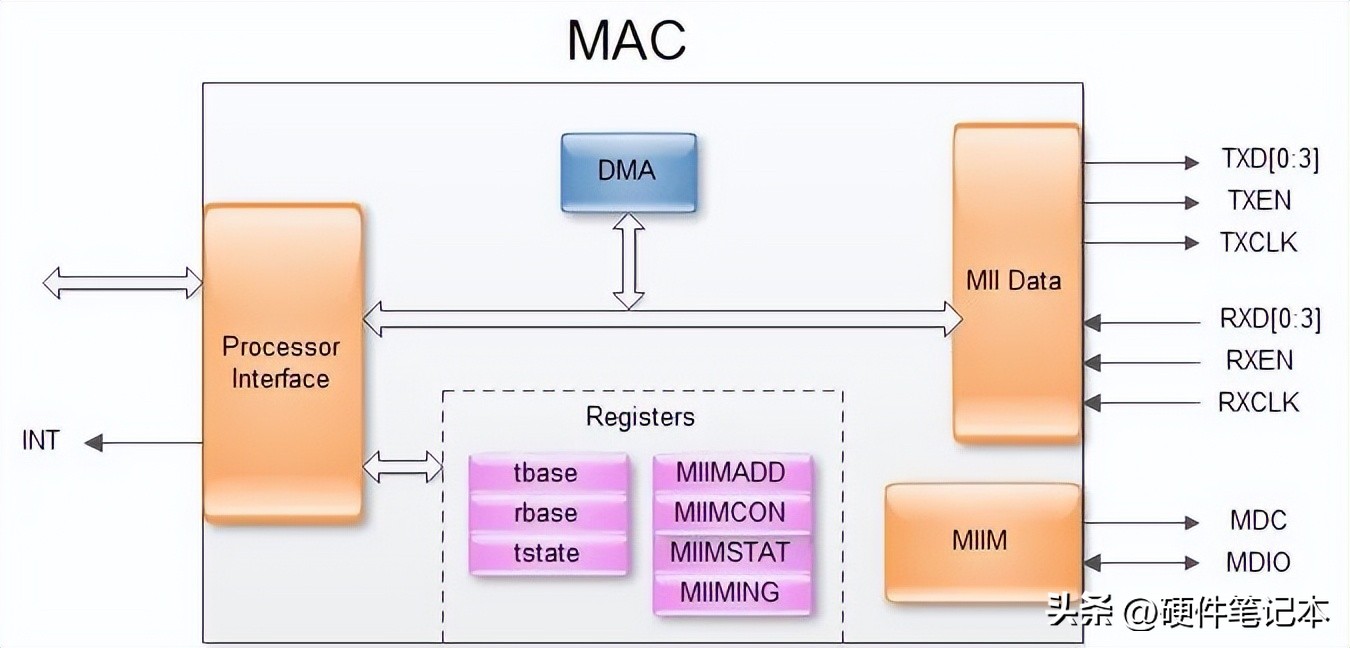

該部分有兩個概念:MAC可以是一個硬件控制器 及 MAC通信以協議。該協議位于OSI七層協議中數據鏈路層的下半部分,主要負責控制與連接物理層的物理介質。MAC硬件大約就是下面的樣子了:

在發送數據的時候,MAC協議可以事先判斷是否可以發送數據,如果可以發送將給數據加上一些控制信息,最終將數據以及控制信息以規定的格式發送到物理層。

在接收數據的時候,MAC協議首先判斷輸入的信息并是否發生傳輸錯誤,如果沒有錯誤,則去掉控制信息發送至LLC(邏輯鏈路控制)層。該層協議是以太網MAC由IEEE-802. 3以太網標準定義。

以太網數據鏈路層其實包含MAC(介質訪問控制)子層和LLC(邏輯鏈路控制)子層。一塊以太網卡MAC芯片的作用不但要實現MAC子層和LLC子層的功能,還要提供符合規范的PCI界面以實現和主機的數據交換。

MAC從PCI總線收到IP數據包(或者其他網絡層協議的數據包)后,將之拆分并重新打包成最大1518Byte、最小64Byte的幀。

這個幀里面包括了目標MAC地址、自己的源MAC地址和數據包里面的協議類型(比如IP數據包的類型用80表示,最后還有一個DWORD(4Byte)的CRC碼。

可是目標的MAC地址是哪里來的呢?

這牽扯到一個ARP協議(介乎于網絡層和數據鏈路層的一個協議)。第一次傳送某個目的IP地址的數據的時候,先會發出一個ARP包,其MAC的目標地址是廣播地址,里面說到:“誰是xxx.xxx.xxx.xxx這個IP地址的主人?”因為是廣播包,所有這個局域網的主機都收到了這個ARP請求。

收到請求的主機將這個IP地址和自己的相比較,如果不相同就不予理會,如果相同就發出ARP響應包。

這個IP地址的主機收到這個ARP請求包后回復的ARP響應里說到:“我是這個IP地址的主人”。這個包里面就包括了他的MAC地址。以后的給這個IP地址的幀的目標MAC地址就被確定了。(其它的協議如IPX/SPX也有相應的協議完成這些操作)。

IP地址和MAC地址之間的關聯關系保存在主機系統里面,叫做ARP表。由驅動程序和操作系統完成。

以太網MAC芯片的一端接計算機PCI總線,另外一端就接到PHY芯片上,它們之間是通過MII接口鏈接的。一個MAC的結構圖如下圖所示:

什么是PHY

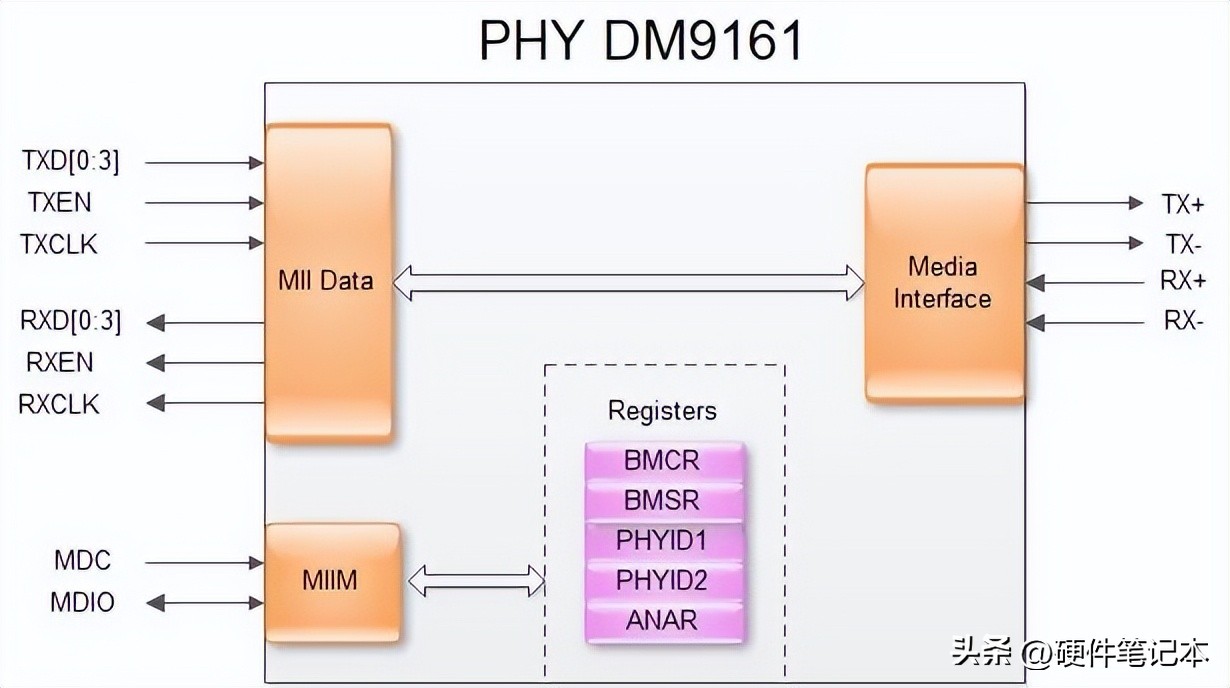

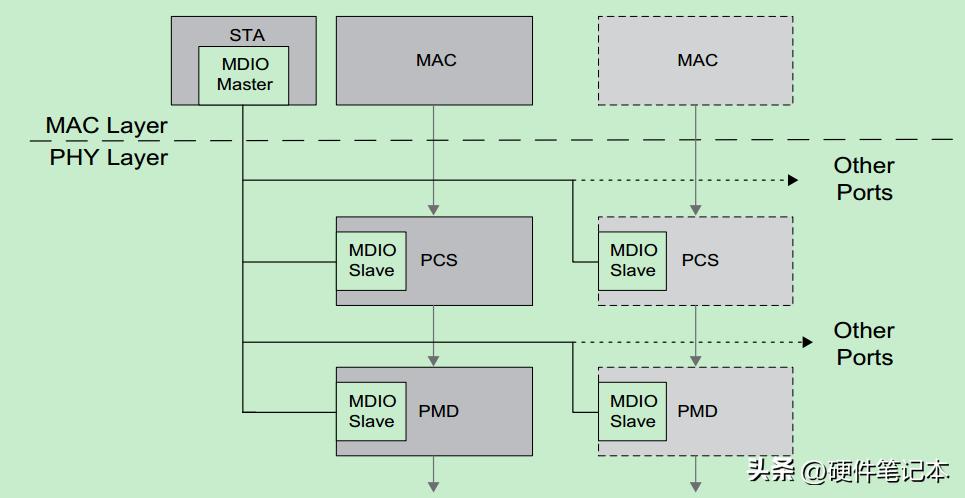

PHY((Physical Layer,PHY))是IEEE802.3中定義的一個標準模塊,STA(station management entity,管理實體,一般為MAC或CPU)通過SMI(Serial Manage Interface)對PHY的行為、狀態進行管理和控制,而具體管理和控制動作是通過讀寫PHY內部的寄存器實現的。一個PHY的基本結構如下圖:

PHY是物理接口收發器,它實現OSI模型的物理層。

IEEE-802.3標準定義了以太網PHY。包括MII/GMII(介質獨立接口)子層、PCS(物理編碼子層)、PMA(物理介質附加)子層、PMD(物理介質相關)子層、MDI子層。它符合IEEE-802.3k中用于10BaseT(第14條)和100BaseTX(第24條和第25條)的規范。

注:PHY寄存器在IEEE802.3標準的 22.2.4 Management functions 節有介紹,但不涉及所有的寄存器,個別寄存器需要到其它章節中看,當然,文檔里面也提到該在哪里找到哪個寄存器。

什么是MII

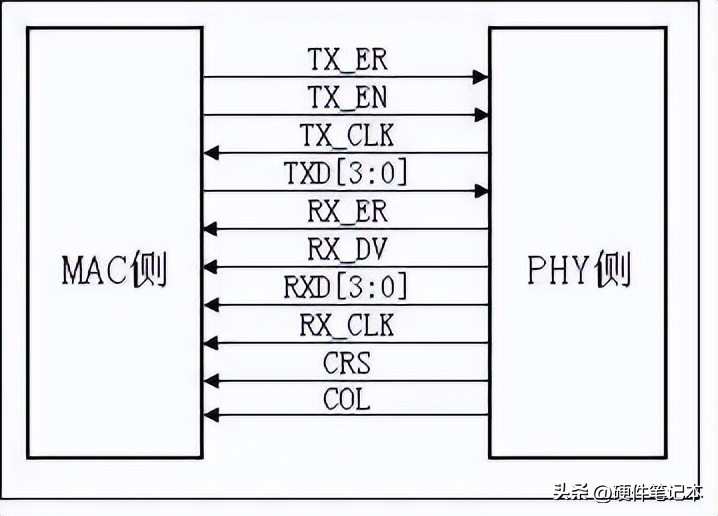

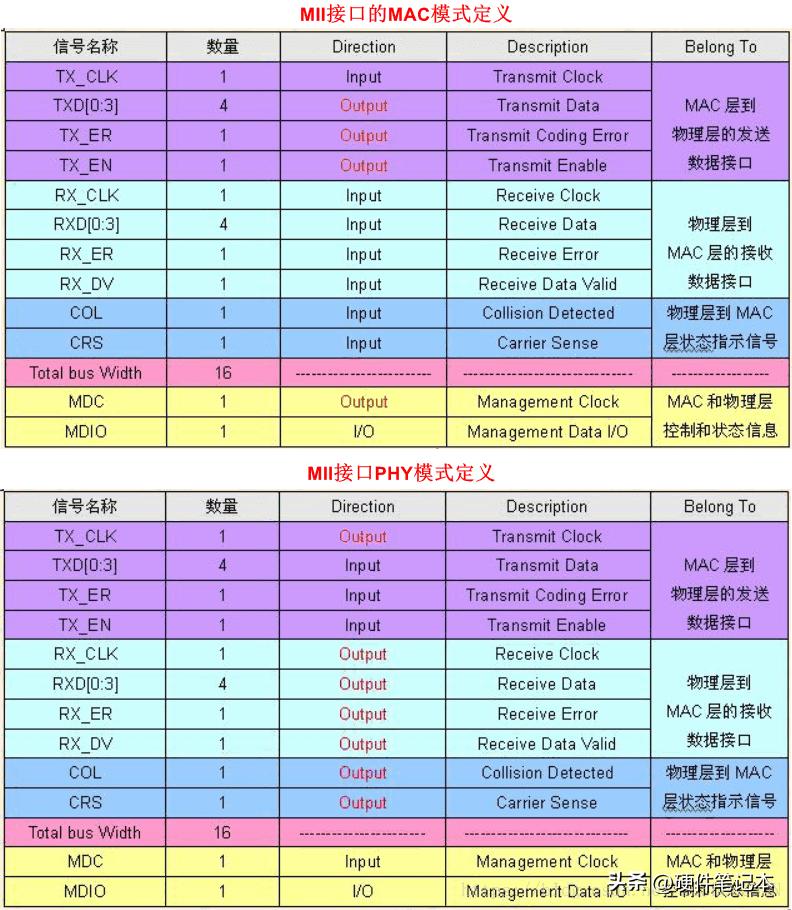

MII(Media Independent Interface)即媒體獨立接口,MII 接口是 MAC 與 PHY 連接的標準接口。它是 IEEE-802.3 定義的以太網行業標準。MII 接口提供了 MAC 與 PHY 之間、PHY 與 STA(Station Management)之間的互聯技術,該接口支持 10Mb/s 與 100Mb/s 的數據傳輸速率,數據傳輸的位寬為 4 位。MII 接口如下圖所示:

MII接口主要包括四個部分。一是從MAC層到PHY層的發送數據接口,二是從PHY層到MAC層的接收數據接口,三是從PHY層到MAC層的狀態指示信號,四是MAC層和PHY層之間傳送控制和狀態信息的MDIO接口。

MII 包括一個數據接口,以及一個 MAC 和 PHY 之間的管理接口:

TX_CLK(transmit clock):TX_CLK (Transmit Clock) 是一個連續的時鐘信號(即系統啟動,該信號就一直存在),它是 TX_EN、TXD、TX_ER(信號方向為從 RS 到 PHY)的參考時鐘,TX_CLK 由 PHY 驅動 TX_CLK 的時鐘頻率是數據傳輸速率的 25%,偏差 ±100ppm。例如,100Mb/s 模式下,TX_CLK 時鐘頻率為 25MHz,占空比在 35% 至 65% 之間。

TXD<3:0>(transmit data):TXD 由 RS 驅動,同步于 TX_CLK,在 TX_CLK 的時鐘周期內,并且TX_EN 有效,TXD 上的數據被 PHY 接收,否則 TXD 的數據對 PHY 沒有任何影響。

TX_ER(transmit coding error):TX_ER 同步于 TX_CLK,在數據傳輸過程中,如果 TX_ER 有效超過一個時鐘周期,并且此時TX_EN 是有效的,則數據通道中傳輸的數據是無效的,沒用的。注:當 TX_ER 有效并不影響工作在 10Mb/s 的 PHY 或者 TX_EN 無效時的數據傳輸。在 MII 接口的連線中,如果 TX_ER 信號線沒有用到,必須將它下拉接地。

TX_EN:發送使能。TX_EN 由 Reconciliation 子層根據 TX_CLK 上升沿同步進行轉換。

RX_CLK:它與 TX_CLK 具有相同的要求,所不同的是它是 RX_DV、RXD、RX_ER(信號方向是從 PHY 到 RS)的參考時鐘。RX_CLK 同樣是由 PHY 驅動,PHY 可能從接收到的數據中提取時鐘 RX_CLK,也有可能從一個名義上的參考時鐘(e.g., the TX_CLK reference)來驅動RX_CLK。

RXD<3:0>(receive data):RXD由RS驅動,同步于 RX_CLK,在 RX_CLK 的時鐘周期內,并且 RX_DV 有效,RXD 上的數據被RS 接收,否則 RXD 的數據對 RS 沒有任何影響。

RX_ER(receive error):RX_ER 同步于 RX_CLK,其在 RX 通道中的作用類似于 TX_ER 對于 TX 通道數據傳輸的影響。

RX_DV(Receive Data Valid):RXD_DV 同步于 RX_CLK,被 PHY 驅動,它的作用如同于發送通道中的 TX_EN,不同的是在時序上稍有一點差別:為了讓數據能夠成功被RS接收,要求RXD_DV有效的時間必須覆蓋整個 FRAME 的過程,即starting no later than the Start Frame Delimiter (SFD) and excluding any End-of-Frame delimiter。MII以4位半字節方式傳送數據雙向傳輸,時鐘速率25MHz。其工作速率可達100Mb/s。

COL(collision detected):COL 不需要同步于參考時鐘。

CRS(carrier sense):CRS 不需要同步于參考時鐘,只要通道存在發送或者接收過程,CRS 就需要有效。

MDC:由站管理實體向 PHY 提供,作為在 MDIO 信號上傳送信息的定時參考。MDC 是一種非周期性的信號,沒有最高或最低時間。無論 TX_CLK 和 RX_CLK 的標稱周期如何,MDC 的最小高低時間應為 160 ns,MDC 的最小周期為 400 ns。

MDIO:是 PHY 和 STA 之間的雙向信號。它用于在 PHY 和 STA 之間傳輸控制信息和狀態。控制信息由 STA 同步地針對 MDC 驅動并且由 PHY 同步地采樣。狀態信息由 PHY 針對 MDC 同步驅動并由 STA 同步采樣。

PHY 里面的部分寄存器是 IEEE 定義的,這樣PHY把自己的目前的狀態反映到寄存器里面。

MAC 通過 SMI 總線不斷的讀取PHY 的狀態寄存器以得知目前 PHY 的狀態。例如連接速度、雙工的能力等。

當然也可以通過 SMI 設置 PHY的寄存器達到控制的目的。例如流控的打開關閉、自協商模式還是強制模式等。

不論是物理連接的MII總線和 SMI 總線,還是 PHY 的狀態寄存器和控制寄存器都是由IEEE的規范的。因此不同公司的 MAC 和 PHY 一樣可以協調工作。當然為了配合不同公司的 PHY 的自己特有的一些功能,驅動需要做相應的修改。

MII 支持 10Mbps 和 100Mbps 的操作,一個接口由 14 根線組成,它的支持還是比較靈活的。但是有一個缺點是因為它一個端口用的信號線太多,如果一個 8 端口的交換機要用到 112 根線,16 端口就要用到 224 根線,到 32 端口的話就要用到 448 根線。

一般按照這個接口做交換機是不太現實的。所以現代的交換機的制作都會用到其它的一些從 MII 簡化出來的標準,比如 RMII、SMII、GMII等。

什么是RMII

簡化媒體獨立接口是標準的以太網接口之一,比 MII 有更少的 I/O 傳輸。RMII 口是用兩根線來傳輸數據的,MII 口是用 4 根線來傳輸數據的,GMII 是用 8 根線來傳輸數據的。

MII/RMII 只是一種接口,對于10Mbps 線速,MII 的時鐘速率是 2.5MHz 就可以了,RMII 則需要 5MHz;對于 100Mbps 線速,MII 需要的時鐘速率是 25MHz,RMII 則是 50MHz。

MII/RMII 用于傳輸以太網包,在 MII/RMII 接口是 4/2bit 的,在以太網的PHY里需要做串并轉換,編解碼等才能在雙絞線和光纖上進行傳輸,其幀格式遵循IEEE 802.3(10M)/IEEE 802.3u(100M)/IEEE 802.1q(VLAN)。

以太網幀的格式為:前導符 + 開始位 + 目的 mac 地址 + 源 mac 地址 + 類型/長度 + 數據 + padding(optional) + 32bitCRC。如果有 vlan,則要在類型/長度后面加上 2 個字節的 vlan tag,其中 12bit 來表示vlan id,另外,4bit 表示數據的優先級!

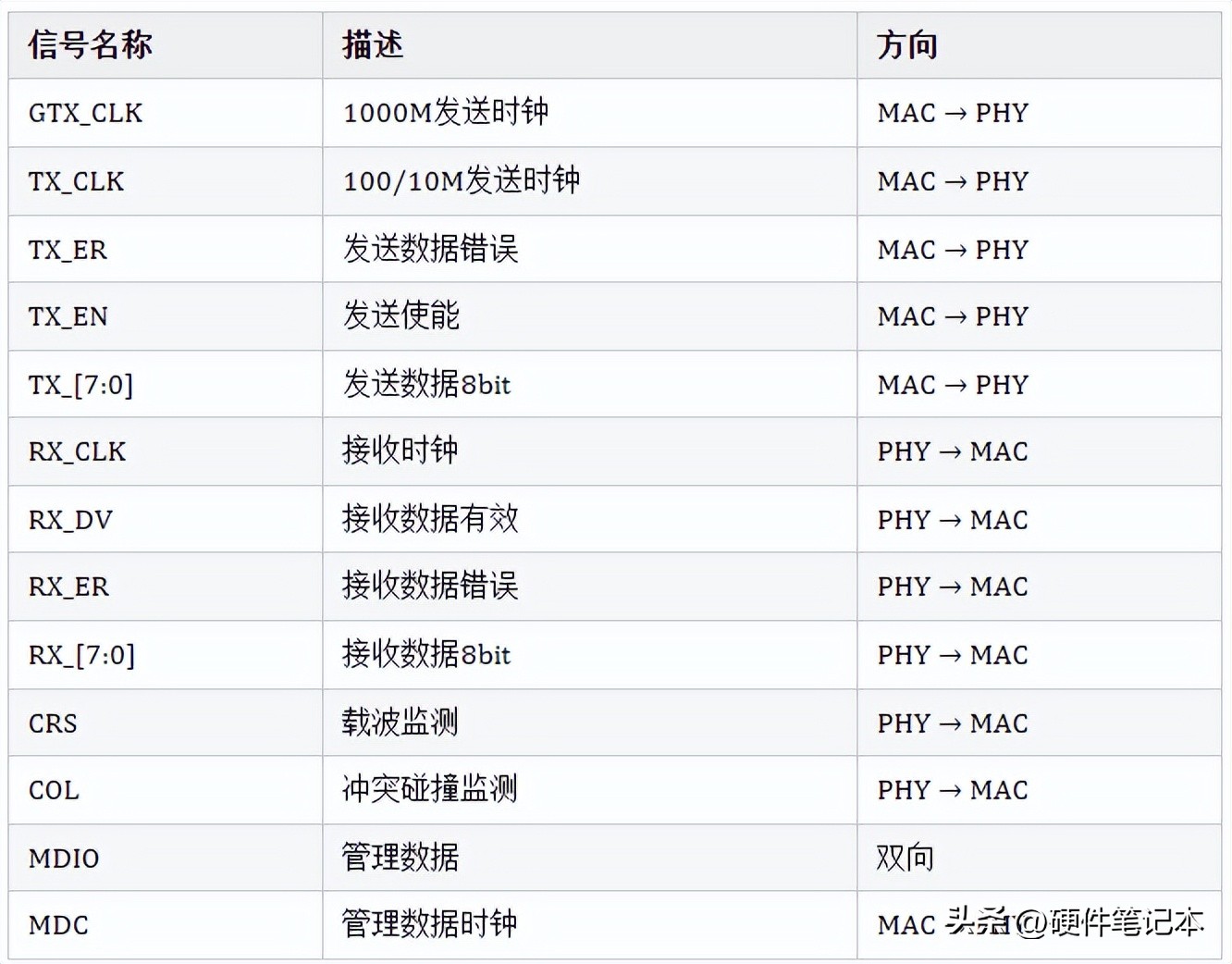

什么是GMII

GMII是千兆網的MII接口,這個也有相應的RGMII接口,表示簡化了的GMII接口。GMII 采用 8 位接口數據,工作時鐘125MHz,因此傳輸速率可達 1000Mbps。

同時兼容 MII 所規定的10/100 Mbps工作方式。GMII 接口數據結構符合IEEE以太網標準,該接口定義見 IEEE 802.3-2000。

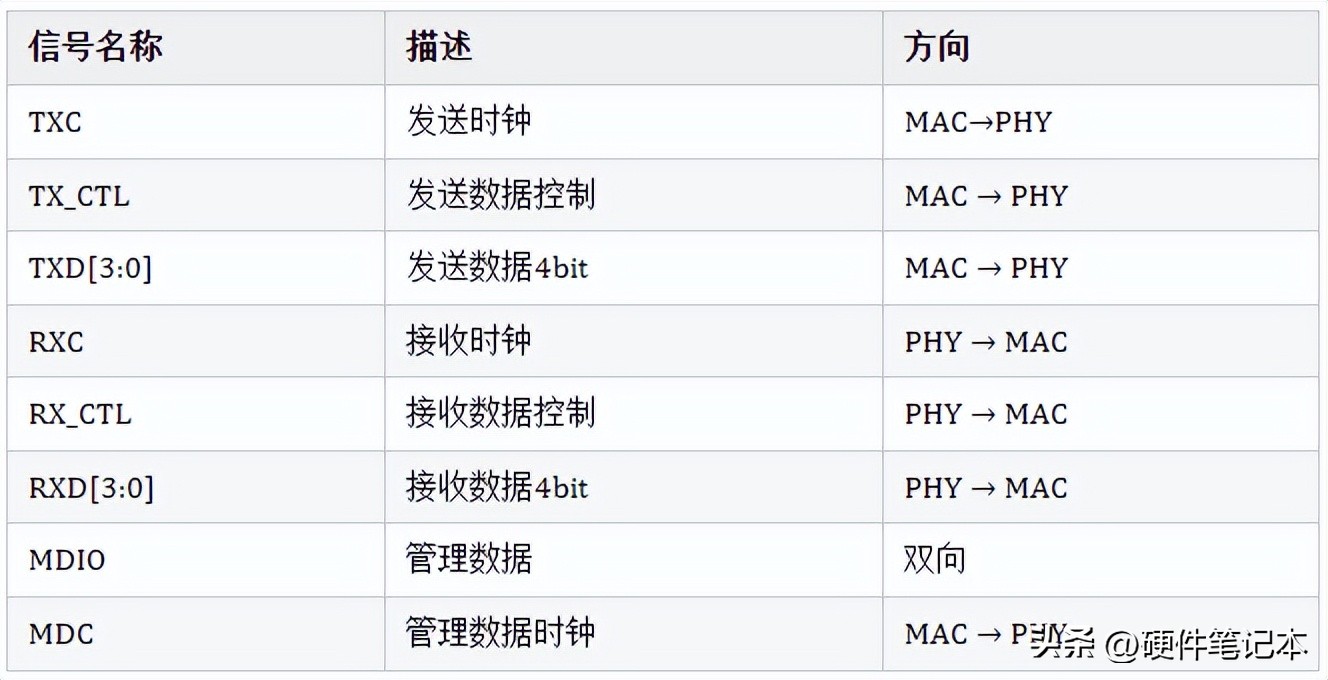

什么是RGMII

RGMII(Reduced Gigabit Media Independant Interface),精簡GMII接口。相對于GMII相比,RGMII具有如下特征:

發送/接收數據線由8條改為4條

TX_ER和TX_EN復用,通過TX_CTL傳送

RX_ER與RX_DV復用,通過RX_CTL傳送

1 Gbit/s速率下,時鐘頻率為125MHz

100 Mbit/s速率下,時鐘頻率為25MHz

10 Mbit/s速率下,時鐘頻率為2.5MHz

信號定義如下:

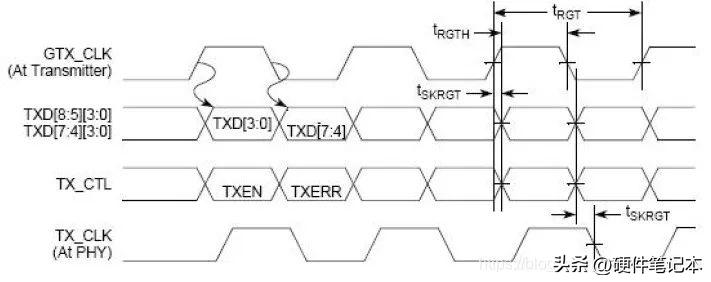

雖然RGMII信號線減半,但TXC/RXC時鐘仍為125Mhz,為了達到1000Mbit的傳輸速率,TXD/RXD信號線在時鐘上升沿發送接收GMII接口中的TXD[3:0]/RXD[3:0],在時鐘下降沿發送接收TXD[7:4]/RXD[7:4],并且信號TX_CTL反應了TX_EN和TX_ER狀態,即在TXC上升沿發送TX_EN,下降沿發送TX_ER,同樣的道理試用于RX_CTL,下圖為發送接收的時序:

什么是SMI

SMI:串行管理接口(Serial Management Interface),通常直接被稱為MDIO接口(Management Data Input/Output Interface)。

MDIO最早在IEEE 802.3的第22卷定義,后來在第45卷又定義了增強版本的MDIO,其主要被應用于以太網的MAC和PHY層之間,用于MAC層器件通過讀寫寄存器來實現對PHY層器件的操作與管理。

MDIO主機(即產生MDC時鐘的設備)通常被稱為STA(Station Management Entity),而MDIO從機通常被稱為MMD(MDIO Management Device)。通常STA都是MAC層器件的一部分,而MMD則是PHY層器件的一部分。

MDIO接口包括兩條線,MDIO和MDC,其中MDIO是雙向數據線,而MDC是由STA驅動的時鐘線。MDC時鐘的最高速率一般為2.5MHz,MDC也可以是非固定頻率,甚至可以是非周期的。

MDIO接口只是會在MDC時鐘的上升沿進行采樣,而并不在意MDC時鐘的頻率(類似于I2C接口)。如下圖所示。

QA

網卡的MAC和PHY間的關系?

網卡工作在osi的最后兩層,物理層和數據鏈路層,物理層定義了數據傳送與接收所需要的電與光信號、線路狀態、時鐘基準、數據編碼和電路等,并向數據鏈路層設備提供標準接口.物理層的芯片稱之為PHY.

數據鏈路層則提供尋址機構、數據幀的構建、數據差錯檢查、傳送控制、向網絡層提供標準的數據接口等功能.以太網卡中數據鏈路層的芯片稱之為MAC控制器.

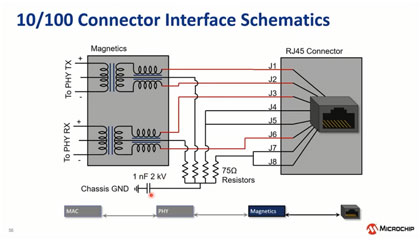

很多網卡的這兩個部分是做到一起的.他們之間的關系是pci總線接mac總線,mac接phy,phy接網線(當然也不是直接接上的,還有一個變壓裝置).

PHY和MAC之間如何進行溝通

通過IEEE定義的標準的MII/GigaMII(Media Independed Interfade,介質獨立界面)界面連接MAC和PHY。這個界面是IEEE定義的。MII界面傳遞了網絡的所有數據和數據的控制。

而MAC對PHY的工作狀態的確定和對PHY的控制則是使用SMI(Serial Management Interface)界面通過讀寫PHY的寄存器來完成的。

PHY里面的部分寄存器也是IEEE定義的,這樣PHY把自己的目前的狀態反映到寄存器里面,MAC通過SMI總線不斷的讀取PHY的狀態寄存器以得知目前PHY的狀態,例如連接速度,雙工的能力等。

當然也可以通過SMI設置PHY的寄存器達到控制的目的,例如流控的打開關閉,自協商模式還是強制模式等。

我們看到了,不論是物理連接的MII界面和SMI總線還是PHY的狀態寄存器和控制寄存器都是有IEEE的規范的,因此不同公司的MAC和PHY一樣可以協調工作。當然為了配合不同公司的PHY的自己特有的一些功能,驅動需要做相應的修改。

評論