晶圓級芯片迎來重磅玩家,未來可期

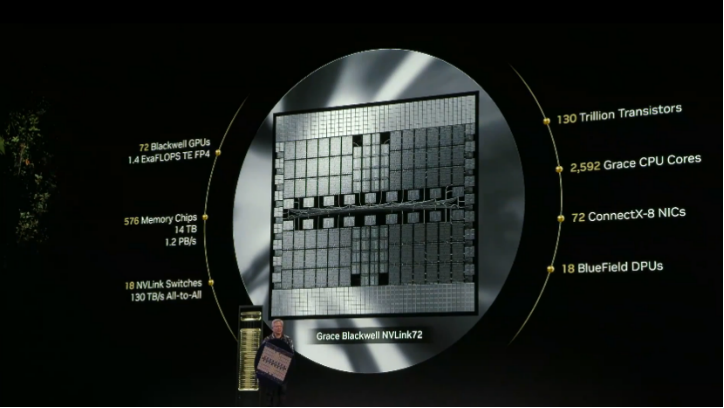

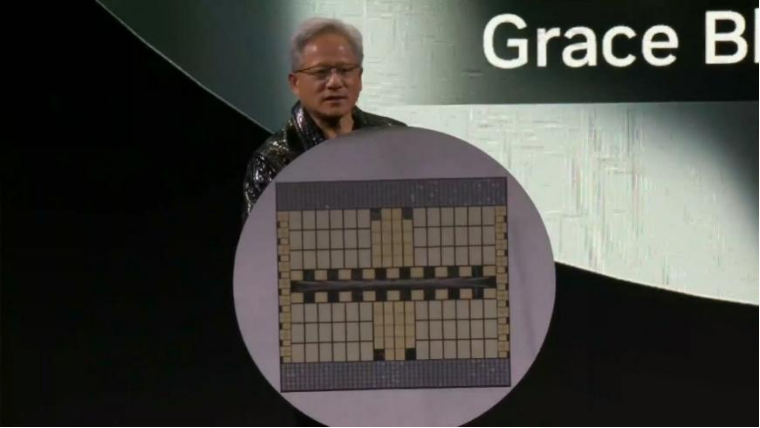

在剛剛結束的國際消費類電子產品展覽會(CES2025)上,英偉達 CEO 黃仁勛的主題演講引發了技術界的熱議,其展示了晶圓級芯片概念 Grace Blackwell NVLink72,并號稱是世界上最大的芯片。

本文引用地址:http://www.j9360.com/article/202501/466468.htm黃仁勛在演講中稱,英偉達擁有多種計算網絡系統,例如 NVLink 36 和 NVLink 72,能夠滿足全球幾乎所有數據中心的需求,目前在約 45 家工廠生產。公司的目標是創建一個名為 Grace Blackwell NVLink72 的巨型芯片,該芯片將使用 72 個 Blackwell GPU,性能超越世界上最快的超級計算機。

圖源:NVIDIA 官網

Grace Blackwell NVLink72 具備將 1.5 噸重,2 英里長銅纜鏈接的 NVL72 濃縮于晶圓上的潛力,以進一步提升內存帶寬和芯片間互聯傳輸速度。

值得注意的是,這款巨型芯片是一塊晶圓級別大小的芯片,相當于 36 張 GB200 組合在一起,總共可提供 1.4EFLOPS 算力,實現 1.2PB/s 的帶寬吞吐。那么英偉達此次推出的晶圓級芯片采取的是一種什么樣的技術呢?為什么如此強大?

什么是晶圓級芯片?

在全球大模型火熱與摩爾定律變緩的雙重背景下,傳統芯片制造工藝逐漸接近物理極限,嚴重制約了算力的提升空間。面對這一挑戰,開發晶圓級芯片成為了一個備受關注的解決方案。

顧名思義,晶圓級芯片通過制造一塊不進行切割的晶圓級互連基板,再將設計好的常規裸片在晶圓基板上進行集成與封裝,從而獲得一整塊巨大的芯片。對比傳統芯片構成的計算集群,晶圓級計算系統通過先進集成技術獲得了芯片級的互連能力。由于舍棄了原本的芯片切割、封裝、互連、電纜及光纜連接等步驟,利用晶圓級的技術物理實現,充分發揮了晶圓大規模、高密度和低損耗的特點。

晶圓級芯片通過構建整片晶圓規模的大規模集成電路,打破了傳統芯片設計中由光刻口徑施加的面積墻限制,對比等效的算力集群,能夠顯著提高系統集成度,減少互連延遲和功耗。相比于傳統的芯片,未經切割的晶圓上電路單元可以更緊密地排列,形成帶寬更高、延時更短的互連結構,大幅加速數據傳輸。晶圓級芯片可以說是目前為止算力節點集成密度最高的一種形態。據測算,其單機柜算力密度能夠達到現有 GPU 方案的 200 倍以上。

那么晶圓級芯片和常規芯片的生產流程有哪些區別呢?

在常規芯片生產流程中,一個晶圓在光刻后被切割成許多小裸片(Die)并單獨進行封裝,每片裸片都單獨封裝為一顆完整的芯片。而晶圓級芯片則是通過制造一塊不進行切割的晶圓級互連基板,再將設計好的常規裸片在晶圓基板上進行集成與封裝,從而獲得一整塊巨大的芯片。對比傳統芯片構成的計算集群,晶圓級計算系統通過先進集成技術獲得了芯片級的互連能力。在晶圓級芯片中,晶圓與附帶組件(例如電源模組和冷卻模組)組成一個完整的系統,而不僅僅是單個芯片。

去年臺積電公布了其晶圓級計算(集成)技術的突破性進展和量產計劃。目前預計 SoW(System on Wafer,即晶圓上系統)會極大改變計算系統的發展進程,為大模型和未來的超級計算更大的算力支撐和擴展能力。SoW 的量產預告也意味著工業界已經在緊鑼密鼓的籌備超越傳統 GPGPU 架構的新計算范式。

在晶圓上系統集成工藝的研發取得突破性進展后,臺積電確信,晶圓級設計的使用率不僅會大幅提升,而且人工智能和 HPC 等大趨勢將需要更復雜的解決方案:垂直堆疊的晶圓系統設計。

英偉達押注!AI 計算正向 SoW 發展

國際上對晶圓上系統的研究起步比較早,2020 年,臺積電發布的 InFO_SoW 技術成功應用于特斯拉的 Dojo 系統。2022 年,ASE、AMD、Intel、微軟、高通、三星、臺積電等十大行業巨頭宣布成立行業聯盟,并制定發布了通用小芯粒互連通道標準規范 UCIe。

晶圓級設計通過直接在整片硅晶圓上構建處理器,實現了前所未有的核心間通信速度、性能密度以及能效,然而,其復雜度與成本也相應增加,限制了廣泛應用。受限于技術水平,目前只有 Cerebras、特斯拉和英偉達開發了晶圓級芯片。

Cerebras

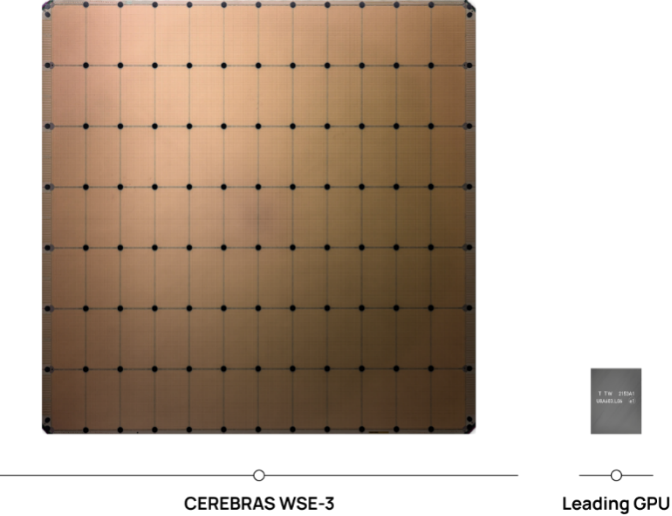

Cerebras 成立于 2016 年,是一家位于美國硅谷的 AI 芯片制造商。其聯合創始人及首席執行官是安德魯·費爾德曼。2019 年,Cerebras 就發布了第一代 WSE(Wafer Scale Engine)芯片。至今該公司已經推出第三代晶圓級芯片。

2024 年 3 月 14 日,美國加州半導體公司 Cerebras Systems 宣布第三代晶圓級 AI 加速芯片「WSE-3」正式面世。這款被業內譽為「規格參數瘋狂」的芯片不僅在功耗和價格方面保持了穩定的優勢,更是將性能推向了一個新的高度。

圖源:Cerebras 官網

圖源:Cerebras 官網

Cerebras 公司的技術路線是通過修改芯片光刻流程實現的。晶圓光刻過程中在計算 Die 之間加入連接線,讓 Die 與 Die 互連進而形成整個晶圓級芯片。

WSE-3 在工藝上采用了臺積電 5nm 工藝,晶體管數量達到了驚人的 4 萬億個,AI 核心數量也進一步增加至 90 萬個。緩存容量更是提升到了 44GB,為用戶提供了更加廣闊的數據處理空間。在外部搭配內存方面,用戶還可以靈活選擇 1.5TB、12TB、甚至高達 1200TB 的內存容量,以滿足不同規模的應用需求。盡管在核心數量和緩存容量的增加幅度上并不突出,但 WSE-3 的性能表現卻實現了質的飛躍。其峰值 AI 算力高達 125PFlops,相當于每秒能夠完成 12.5 億億次的浮點計算。WSE-3 在短短的一天內就能夠完成 Llama 700 億參數的訓練任務。

特斯拉

特斯拉在 2021 年一場名為「AI Day」的活動上,推出了名為「Dojo」的超級計算機,其功能不僅可以處理海量的視頻數據,也可以為特斯拉 Autopilot、全自動駕駛系統(FSD)以及人形機器人 Optimus 提供算力支持。

而 Dojo 超級計算機系統的核心部件就是 D1 芯片,這是一款采用臺積電 7 納米工藝打造的高性能芯片,集成了 500 億晶體管,其內部集成了一個處理器核心、一個高帶寬內存、一個高速互連器以及高速緩存,其峰值算力為 362TFL。

值得注意的是,Tesla Dojo 的晶圓級處理器采用了 Chiplet 路線在晶圓尺寸的基板上集成了 25 顆專有的 D1 芯片。這款晶圓級處理器也是基于臺積電 InFO-SoW 技術量產的首款解決方案,與系統級封裝 (SiP) 相比,具有低延遲高帶寬、高性能、高帶寬密度、供電電阻也更低。

特斯拉在一個訓練模塊中集成了 25 顆 D1 芯片,讓特斯拉的訓練模塊峰值算力達到了 9PFLOPS,帶寬為 900GB/s。然后 10 個訓練模塊又繼續組合成一個算力為 900 PFLOPS,帶寬 90TB/s 的系統托盤,并配以相對應的供電冷卻聯網系統,這個東西被官方稱為 ExaPOD 集群。在經過了一系列的「堆料」操作后,特斯拉就得到了這個由 3000 顆 D1 芯片組成的 Dojo 超級計算機。

英偉達

在近期的 CES 上,英偉達推出了其歷史上造過的最大芯片 Grace Blackwell NVLink 72。該芯片主要用于 GB200 NVL72(NVIDIA 于 2024 年 3 月 GTC 大會上發布的一套多節點液冷機架級擴展系統,適用于高度計算密集型的工作負載)中。

圖源:NVIDIA 官網

圖源:NVIDIA 官網

GB200 NVL72 在一個機柜中,封裝了 36 個 Grace CPU 和 72 個 Blackwell GPU,AI 算力高達 1.44 EFLOPS。而此前特斯拉自研的 Dojo 將 5 x 5 的 D1 芯片封裝成訓練塊,再將多個訓練塊封成一個機柜,這個機柜叫 ExaPod。

英偉達的 Grace Blackwell NVLink 72 對特斯拉的自研芯片構成了巨大挑戰。根據特斯拉方面的計劃,他們本來打算在 2023 年財年生產 4~5 萬顆 D1 芯片,逐步替換掉英偉達的算力芯片,其首個 ExaPOD 也在 2023 年 7 月投入了運營。

但此后馬斯克突然表示,自研芯片,毫無必要,他說:「如果英偉達能夠給我們足夠的 GPU,也許我們就不需要 Dojo,但他們無法滿足我們的需求。」一向癡迷于技術創新的馬斯克之所以會說這樣的話,無非就是他們的自研芯片無法滿足需求。

隨著臺積電工藝的成熟,AI 計算正向 SoW 發展,未來會有越來越多企業加入戰局。

軟件定義晶上系統(SDSoW)受關注

現階段,晶上系統(SoW)正以其獨特的魅力引領著全球集成電路產業的變革。早在 2019 年,鄔江興院士團隊就憑借極具前瞻性的眼光原創提出軟件定義晶上系統(Software Defined System on Wafer,簡稱 SDSoW)概念。SDSoW 是直接用完整的晶圓基板來做系統內部各模塊的互連底座,通過在晶圓上采用先進集成技術將計算、存儲、互連、I/O 等各種芯粒組裝實現完整的系統,提供更大范圍的資源可配置性,同時系統內各模塊之間以及各模塊本身的連接支持軟件定義。它打破現有集成電路的設計方法、計算范式、實現材料、集成方式等邊界條件,相比基于 PCB 的芯片焊裝成組件堆疊出更大系統的工程實現模式,SDSoW 系統的帶寬、延遲、功耗均可獲得大幅增益,整體系統性能可提升 3~5 個數量級。

SDSoW 技術是應對芯片傳統工藝微縮難以為繼、摩爾定律逐漸失效的新出路,通過晶上拼裝集成和軟件定義體系結構,不僅可以滿足系統技術創新對于領域專用多樣化、異質集成功能等方面的需求,而且還擺脫了單一工藝節點維度對提升芯片性能的束縛,通過芯粒的晶圓級組裝,可以快速、經濟地研制出能夠滿足未來需求的晶圓級芯片及系統。SDSoW 將帶動集成電路技術從 SoC 進入 SoW 時代, 極大地弱化我國集成電路對先進工藝進步的強依賴性,助力我國奪取美國霸權下的集成電路自主發展權。

為加快培育我國晶上系統產業生態體系,軟件定義晶上系統技術與產業聯盟(簡稱晶上聯盟)積極開展生態服務平臺建設,已取得一系列突出成果。2024 年 6 月,在第七屆晶上系統生態大會(SDSoW2024)上成立了天津市晶上集成電路產業發展中心以及晶上聯盟專家委員會,以指導、推動國內晶上系統技術的發展。同時,大會還發布了《晶上系統硬件制造通用工程技術規范》和《軟件定義晶上系統互連接口標準(草案)》,為晶上系統的設計和制造提供了明確的指導和規范。據了解,2025 年第八屆晶上大會還將會有更多生態成果重磅發布。

評論