首發推遲?臺積電2nm真的用不起

蘋果原本計劃在今年推出的iPhone 17 Pro和iPhone 17 Pro Max兩款機型上搭載臺積電2nm處理器芯片,現如今可能會將時間推遲12個月至2026年。因此,將于今年下半年發布的iPhone 17系列中或將采用3nm的臺積電N3P工藝,而非2nm制程。

本文引用地址:http://www.j9360.com/article/202501/465987.htm

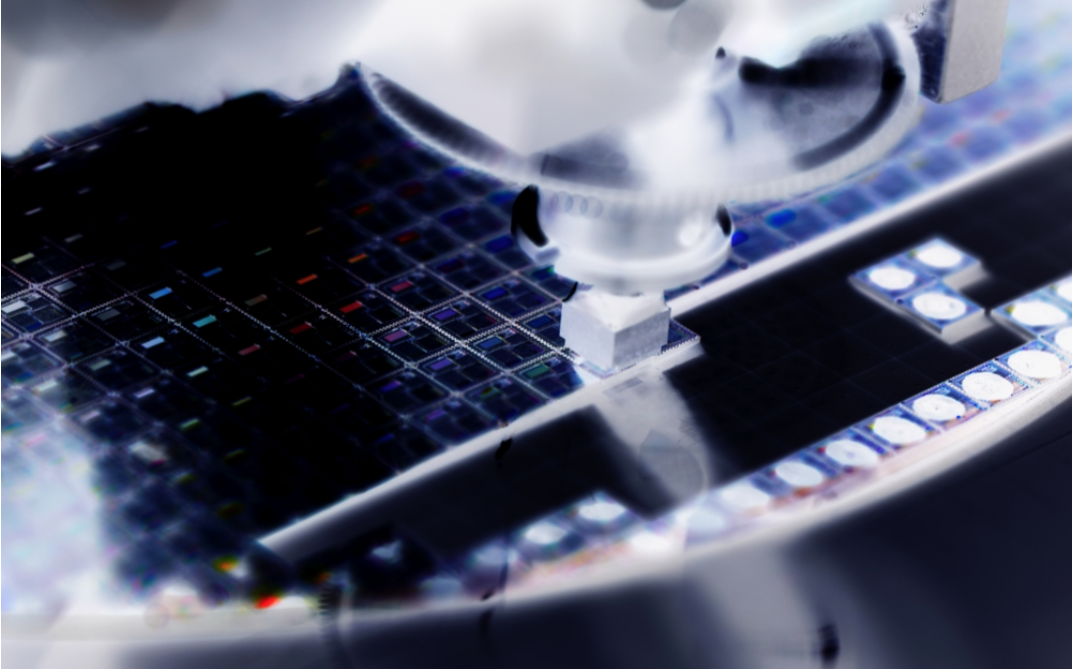

目前,臺積電已在新竹寶山工廠開始了2nm工藝的試產工作(每月5000片晶圓的小規模生產),初期良率是60%,這意味著有將近40%的晶圓無法使用,每片晶圓的代工報價可能高達3萬美元。

第一座工廠計劃位于新竹縣寶山附近,毗鄰其專門為開發N2技術及其后續技術而建的R1研發中心,預計將于2025年下半年開始大批量生產(HVM)2nm芯片;第二座能夠生產N2芯片的制造廠將位于高雄科學園區,該園區是高雄附近南臺灣科學園區的一部分,HVM啟動時間預計稍晚一些,可能在2026年左右。此外,臺積電正在努力獲得批準,在臺中科學園區建造另一座具有N2能力的工廠。

2016年,制程技術演進至10nm后,報價增幅顯著,達到6000美元;進入7nm、5nm制程世代后,報價破萬;相比于2nm,目前3nm晶圓的價格大約在1.85-2萬美元/片之間。

以iPhone 18 Pro系列首發搭載的A20 Pro處理器為例,這顆首個利用臺積電2nm工藝制程的芯片,價格將由目前的50美元上漲至85美元,漲幅高達70%。由于先進制程報價居高不下,芯片廠商成本高企,勢必將成本壓力轉嫁給下游客戶或終端消費者。

2024年,高端智能手機集體用上了基于3nm工藝的旗艦芯片:驍龍8至尊版、天璣9400、A18系列都采用了臺積電3nm工藝。相比4nm工藝,3nm工藝的代工費貴了不少,加上內存儲存等核心元器件的漲價,讓驍龍8至尊版/天璣9400旗艦機的價格普遍上漲。以小米為例,小米15的起售價,比上代就上漲了500元。

而2nm將如期在2025年進入量產,其量產曲線預計與3nm相似。臺積電正全力提升產能,通過設施投資,預計到2026年臺積電2nm制程產能將擴大至8萬片晶圓。據報道,臺積電已調整了對客戶的2025年代工報價,以緩解海外設施高昂運營成本和2nm部署成本造成的毛利率損失的影響。

不可否認的是,高工藝的芯片確實帶來了更高的性能和更低的功耗,但隨之而來的高昂價格也讓許多客戶望而卻步。而臺積電之所以這么報價,當然是因為:沒有對手。

臺積電2nm工藝性能優秀

晶體管的密度越大,就必然需要溝道長度越來越小,而隨著溝道長度的縮短,溝道管中的源極和漏極的距離也會越來越短。因此柵極很難再保證對溝道的控制能力,也意味著柵極電壓夾斷溝道的難度變大,即產生短溝道效應,從而出現嚴重的電流泄露。

為了解決這個問題,華人科學家胡正明在1999年提出了「鰭式場效應晶體管(FinFET)架構」。在這個結構中,柵門被設計成了類似魚鰭狀的3D結構,能夠讓晶體管溝道長度減少的同時,大幅減少電流泄露的問題。

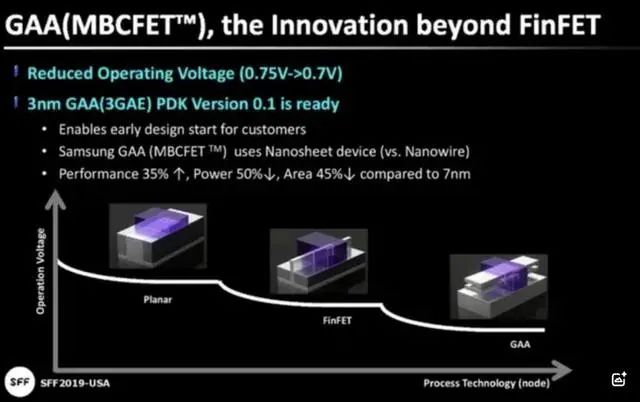

FinFET架構的出現,讓摩爾定律被續命將近20年,但自芯片代工行業進入先進制程后,該架構也開始逐漸失效,2nm的節點就被普遍認為是“決戰節點” —— 全環繞柵極(GAA)納米片晶體管被提出。與FinFET相比,GAA架構相當于將柵極的鰭片旋轉90°,然后再在垂直方向上分成了多條鰭片,來增加其與溝道的接觸面積。

這條技術路線得到了業內的廣泛認可,但卻讓代工難度呈指數級上升。實際上,GAA技術在三星的3nm制程中就被搶先采用,但由于開發難度過大且時間緊迫,其3nm試生產的良率不足20%,根本無法滿足量產需求,甚至無法自給自足。蘋果、高通、聯發科、英偉達等科技巨頭都將3nm芯片的訂單交給了臺積電,臺積電幾乎包攬了全球的3nm芯片產能。

相比于三星的“一步到位”,臺積電則選擇在2nm工藝中首次引入GAA架構。此前在IEDM 2024大會上,臺積電披露了N2工藝的關鍵技術細節和性能指標:對比3nm,晶體管密度增加15%,同等功耗下性能提升15%,同等性能下功耗降低24-35%。這一提升得益于GAA技術更低的閾值電壓,從而降低了漏電功耗。

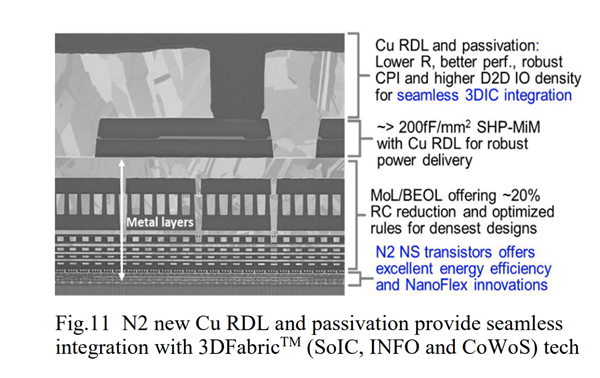

對比傳統的FinFET晶體管:臺積電N2工藝可以在0.5-0.6V的低電壓下,獲得顯著的能效提升,可以將頻率提升大約20%,待機功耗降低大約75%;還應用了全新的MOL中段工藝、BEOL后段工藝,電阻降低20%,能效更高;針對高性能計算應用,臺積電2nm還引入了超高性能的SHP-MiM電容,容量大約每平方毫米200fF,可以獲得更高的運行頻率。

按照臺積電的說法,28nm工藝以來,歷經六代工藝改進,N2工藝單位面積的能效比已經提升了超過140倍。

同時,臺積電還在研發N2P(N2增強版本),計劃2025年完成資格認證階段,2026年下半年量產。與原始N2相比,N2P功耗降低5%-10%(在相同頻率和晶體管數量下)或性能提高5%-10%(在相同功率和晶體管數量下),并完全兼容N2。在歐洲開放創新平臺論壇上臺積電宣布,Cadence和Synopsys的所有主要工具以及西門子EDA和Ansys的仿真和電遷移工具,都已為臺積電的N2P制造工藝做好準備。

整個N2系列將增加臺積電的全新NanoFlex功能,該功能允許芯片設計人員混合和匹配來自不同庫的單元,可以優化溝道寬度以提高性能和功率,然后構建短單元(以提高面積和功率效率)或高單元(以提高15%的性能)。

另外,還預計臺積電將在2026年下半年開始量產A16制程(即1.6nm),A16工藝將結合臺積電的超級電軌架構,即背部供電技術。與N2P工藝相比,A16在相同工作電壓下速度快了8%-10%,或在相同速度下功耗降低15%-20%,同時密度提高至原來的1.1倍。

值得注意的是,因為臺積電2nm的報價太高,高通已經在考慮使用三星2nm的工藝。相關報道稱,高通在測試三星的2nm工藝,不過尚未敲定高通是否會將訂單交給三星。畢竟在驍龍8+Gen1表現不俗之后,高通的驍龍8Gen2、驍龍8Gen3、驍龍8至尊版等旗艦芯片,都是由臺積電代工。而且在驍龍8至尊版轉向自研CPU架構后,CPU超大核主頻達到了驚人的4.32GHz,功耗要求極高,現在確實是只有臺積電才能做到。

AI應用的爆發式增長,讓各大芯片廠商紛紛爭搶臺積電3nm的產能,臺積電用十個月完成了2023年全年業績。而且不難推測,所有3nm的客戶都會在后續采用2nm制程。在這樣的背景下,臺積電董事長兼首席執行官魏哲家曾自信地表示,2nm工藝的需求空前高漲,目前2nm的規劃產能已經超過3nm。

臺積電N2還有對手嗎?

2nm芯片的價格如此高昂,一方面是因為各個環節的成本都在上升,另一方面也是因為臺積電在芯片代工行業中,已經形成了事實上的壟斷。僅在今年,臺積電便兩次提高其代工費用,不僅是對3nm工藝制程,甚至5nm工藝制程的價格亦被提高4%-10%。

由于半導體設計企業在3nm以下的先進工藝中對臺積電的依賴程度不斷加深,而臺積電產能不足、價格上漲,半導體設計企業對代工廠商多元化的意愿也在不斷增強。那么在進入2nm工藝時代后,行業內還有能掣肘臺積電的力量嗎?

臺積電的競爭對手三星正在全力提升2nm制程良率,并推動現有客戶日本PFN等公司進行測試,以爭奪2nm制程市場。三星在3nm工藝制程上跌了個大跟頭后,立志要在2nm工藝制程上完成追趕。

此前業內就有傳聞稱,三星已經有暫停3nm工藝開發,全力“All in”2nm工藝的打算。業內人士透露,三星在其平澤P2和P3生產基地的4nm、5nm和7nm制程中,已有超過30%的代工生產線停產,并計劃在年底前將停產比例擴大至約50%。而3nm的情況更不樂觀,報道指出三星目前第一代的3nm制程工藝目前良率只有60%。

考慮到其位于華城的S3產線,在還未正式量產3nm晶圓前,就開始計劃將設備升級為2nm工藝的配套設備,這種說法可能并非空穴來風。但按照三星的規劃,其2nm產能至少要到2027年才能量產。

三星2nm工藝不僅要面對良品率較低的老問題,而且還要將性能功耗提升到客戶所期望的水平,這可能是承受了數萬億韓元虧損的三星代工業務的最后機會。三星代工翻車是從高通驍龍888芯片出現了過熱問題開始,這是由于當時三星的5nm工藝結合Arm的X1超大核心功耗過高導致的,因此從驍龍8+ Gen1開始,高通驍龍8系平臺轉投臺積電。如果驍龍平臺轉向三星2nm工藝制程,那么其功耗問題將會是業內關注的熱點。

另一邊的英特爾,雖然已經完成18A工藝(等效2nm)的試生產工作,但被曝良率過低,且公司正處于動蕩期,量產時間也是遙遙無期。臺積電過于有統治力的市場主導地位在2nm制程上仍會延續。從目前的進度來看,先進制程的主要競爭者在2nm上依舊不能望其項背。

評論