臺積電2nm制程設計平臺準備就緒,預計明年末開始量產

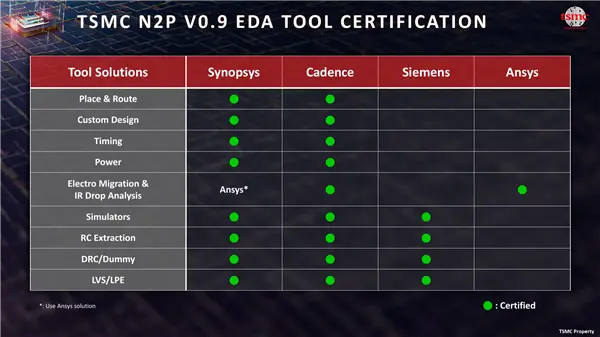

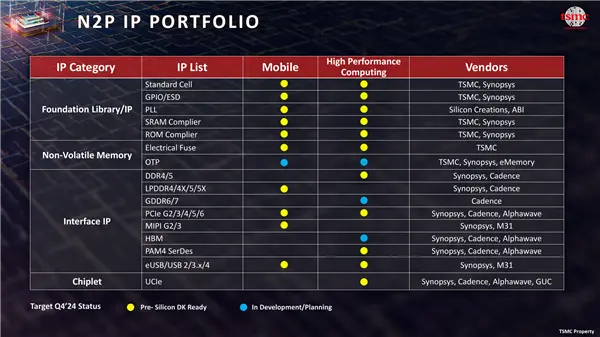

在歐洲開放創新平臺(OIP)論壇上,臺積電表示電子設計自動化(EDA)工具和第三方IP模塊已為性能增強型N2P/N2X制程技術做好準備。目前,Cadence和Synopsys的所有主要工具以及Siemens EDA和Ansys的仿真和電遷移工具,都已經通過N2P工藝開發套件(PDK)版本0.9的認證,該版本PDK被認為足夠成熟。

本文引用地址:http://www.j9360.com/article/202411/464925.htm這意味著各種芯片設計廠商現在可以基于臺積電第二代2nm制程節點開發芯片。據悉,臺積電計劃在2025年末開始大規模量產N2工藝,同時A16工藝計劃在2026年末開始投產。

臺積電N2系列工藝技術相較于其前代的主要增強之處在于納米片全柵極(GAA)晶體管和超高性能金屬-絕緣體-金屬(SHPMIM)電容 —— 納米片GAA晶體管的優勢是可以通過調整通道寬度來定制高性能或低泄漏操作,SHPMIM電容則可以增強電源穩定性并促進片上解耦。

與第一代N2工藝相比,N2P會有額外的改進:功耗降低5%-10%(在相同頻率和晶體管數量下)或性能提高5%-10%(在相同功耗和晶體管數量下);而N2X會擁有比N2和N2P更高的FMAX電壓,能夠為數據中心CPU、GPU和專用ASIC提供更好的性能。在IP層面,N2P和N2X兼容,因此打算使用N2X的公司無需重新開發為N2P設計的任何東西。

臺積電還成功縮小了2nm制程節點上的SRAM單元尺寸,將HD SRAM位單元尺寸縮小到約0.0175μm2(約減小了10%),大幅提升SRAM密度。這一改進對于提高處理大批量數據的能力至關重要,因為更大的緩存容量意味著更少的內存訪問,從而節省了性能和電力消耗。此外,臺積電還開發了RDL(低阻值重置導線層)、超高效能金屬層間(MiM)電容,以進一步提高性能。

后續的A16將結合臺積電的超級電軌(Super Power Rail)架構,也就是背部供電技術,這可以在正面釋放出更多的布局空間,提升邏輯密度和效能,適用于具有復雜訊號及密集供電網絡的高性能計算(HPC)產品。

臺積電指出目前主要客戶已完成2nm IP設計,并已經開始進行驗證。按照3nm節點由蘋果A系列首發登場來看,首先進行2nm流片驗證的很可能還是蘋果的A系列芯片。但是由于2nm制程最早也得于2025年量產,所以iPhone 17所搭載的芯片很可能還是由臺積電3nm打造,需要等到iPhone 18上我們才能看到2nm的芯片登場。

前段時間,臺積電董事長兼首席執行官魏哲家表示,客戶對于2nm的詢問多于3nm,看起來更受客戶的歡迎。為了應對市場對2nm工藝技術的強勁需求,臺積電持續對該制程節點進行投資,加快了2nm產線的建設,并進一步擴大了產能規劃。

臺積電高雄2nm新廠今天將舉行設備進機典禮,該廠是臺積電在高雄的首座12英寸廠,原計劃相關設備最快2025年Q3進機,現在整體進度較原計劃超前半年以上。目前,臺積電2nm布局主要是在新竹寶山、高雄新廠兩路并進,其中寶山一廠已在今年4月進機、6月使用英偉達cuLitho平臺結合AI加速風險試產流程,后續寶山二廠也會維持進度。

評論