0.1 納米時代,巨頭發力下一代晶體管 CFET

盡管摩爾定律的增速已顯著放緩,但工藝節點依然穩步向前,現已演進至 2nm 甚至 1nm 以下。而在最新的邏輯節點中,傳統器件架構已不具優勢,而互補場效應晶體管 (CFET) 則被看做「成大事者」,成為埃米時代(1 埃米等于 0.1 納米)的主流架構。那么 CFET 究竟有著怎樣的魅力?

本文引用地址:http://www.j9360.com/article/202407/460607.htm為什么需要 CFET?

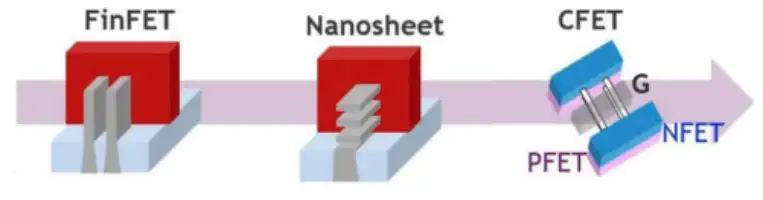

CFET,作為一種創新的 CMOS 工藝,以其晶體管垂直堆疊的獨特方式,突破了傳統平面工藝、FinFET(鰭式場效應晶體管)以及 GAAFET( 環繞式柵極技術晶體管)的平面局限。

至于為何 CFET 架構備受矚目?讓我們一窺 FinFET 與 GAAFET 在當前技術挑戰下所遭遇的瓶頸,便不難理解 CFET 為何值得深入研究。

先看 FinFET。

FinFET 是一種新的互補式金屬氧化物半導體晶體管,該項技術的發明人是加州大學伯克利分校的胡正明教授。

2011 年,英特爾率先將 FinFET 技術商業化,并應用于 22nm 制程,顯著提升性能與降低功耗。隨后,臺積電、三星等廠商跟進,FinFET 技術大放異彩。之后為了提高晶體管性能并進一步減小面積,FinFET 體系架構也進行了持續的改進。自 16/14nm 起,FinFET 成為主流選擇,推動半導體工藝發展至 3nm 節點。然而,實際上自進入 5nm 后,FinFET 就開始面臨鰭片穩定性、柵極寬度限制及靜電問題等挑戰。修修補補的 FinFET 終將力不從心,新的架構因此呼之欲出。

下面接棒的選手便是 GAAFET。GAAFET 即環繞柵極場效應晶體管,其架構本質就是把 FinFET 的 Fin 旋轉 90°,然后把多個 Fin 橫向疊起來,這些 Fin 都穿過 gate。

GAAFET 有兩種結構,一種是使用納米線(Nanowire)作為電子晶體管鰭片的 GAAFET;另一種則是以納米片(Nanosheet)形式出現的具有較厚鰭片的多橋通道場效應管 MBCFET。

據悉,三星在 3nm 制程節點就已經導入 GAAFET 架構,而臺積電將在 2nm 制程節點首度應用 GAAFET 晶體管,英特爾此前表示將在 Intel 20A 工藝上,引入采用 GAA 設計的 RibbonFET 晶體管架構。

隨著 GAAFET 晶體管的 gate(門)與 channel(溝道)的接觸面積變大,而且對于 FinFET 而言,Fin 的寬度是個定值;但對 GAAFET 而言,sheet(薄片)本身的寬度與有效溝道寬度是靈活可變的。更寬的 sheet 自然能夠達成更高的驅動電流和性能,更窄的 sheet 則占用更小的面積自然可以提供比 FinFET 更好的靜電特性,滿足某些柵極寬度的需求。

在同等尺寸結構下,GAAFET 的溝道控制能力得到強化,尺寸進一步微縮更有可能性,且新的結構所需的生產工藝應該與鰭式晶體管相似,可以繼續使用現有的設備以及技術成果。

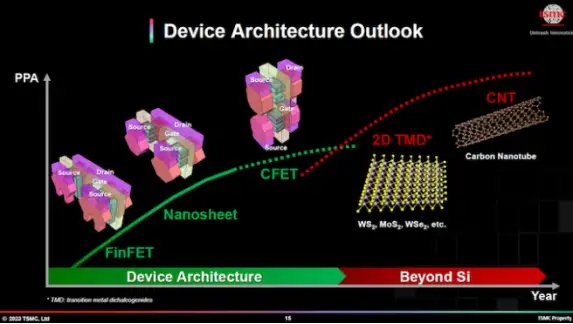

不過,GAAFET 雖然已經實現了在 3nm 甚至 2nm 工藝中的應用,但進一步縮小到 1nm 以下將面臨巨大的工藝挑戰。

這時,業界的科技巨頭們又開始紛紛調整策略,將他們的目光和精力聚焦在了 CFET 這一新興技術上。

CFET 大展身手

CFET 將不同導電溝道類型(N-FET 和 P-FET)的 GAA 器件在垂直方向進行高密度三維單片集成。

相較于現有主流 FinFET 與 GAAFET 晶體管集成電路工藝,CFET 突破了傳統 N/P-FET 共平面布局間距的尺寸限制,可將集成電路中邏輯標準單元尺度微縮到 4-T(Track)高度,同時將減少 SRAM 單元面積 40% 以上。在追求極致性能與密度的未來科技領域,CFET 無疑將成為基礎晶體管器件創新架構的有力候選者。

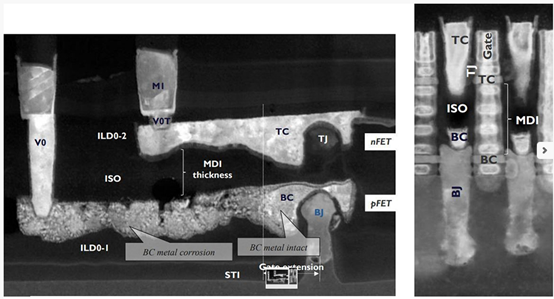

在 2023 的 IEEE 國際電子器件會議上,臺積電發布了一篇標題《面向未來邏輯技術擴展的 48 納米柵極間距的互補場效應晶體管 (CFET)》的論文,其器件的與眾不同之處在于采用了一種新方法,在頂部和底部器件之間形成一個介電層,以保持它們之間的隔離。納米片一般由硅層和硅鍺層交替形成。在工藝的適當步驟中,硅鍺特定蝕刻方法會去除這些材料,從而釋放出硅納米線。臺積電使用硅鍺層將兩個器件隔離開來,因為知道硅鍺層的蝕刻速度比其他硅鍺層快,所以使用了鍺含量特別高的硅鍺層。這樣,隔離層就可以在釋放硅納米線之前分幾步制作完成。

近日,臺積電資深副總經理暨副共同首席運營官張曉強在 2024 技術論壇上宣布,臺積電已成功集成不同晶體管架構,在實驗室做出 CFET。張曉強指出,CFET 預計將被導入下一代的先進邏輯工藝。CFET 是 2nm 工藝采用的納米片場效應晶體管架構后,下一個全新的晶體管架構。

不僅是臺積電,還包括三星、英特爾在內的芯片三巨頭,都對 CFET 的開發給予高度重視。

英特爾是三家中最早演示 CFET 的,早在 2020 年就在 IEDM 上推出了早期版本,隨后在 2023 的 IEEE 國際電子器件會議上,圍繞 CFET 制造的最簡單電路(inverter)做了多項改進。英特爾組件研究小組首席工程師 Marko Radosavljevic 表示:「inverter 是在單個鰭片上完成的。在最大縮放比例下,它將是普通 CMOS 逆變器尺寸的 50%。」此外,英特爾還通過將每個器件的納米片數量從 2 個增加到 3 個,將兩個器件之間的間距從 50 nm 減小到 30 nm。

三星對 CFET 的開發也很積極。在去年的 IEEE 會議上,三星演示了 48nm 和 45nm 接觸式多晶硅間距 (CPP) 的結果。不過這些結果是針對單個器件,而不是完整的逆變器。雖然三星的兩個原型 CFET 中較小的一款性能有所下降,但幅度不大,該公司的研究人員相信制造工藝優化將解決這一問題。

三星成功的關鍵在于能夠對堆疊 pFET 和 nFET 器件的源極和漏極進行電氣隔離。如果沒有足夠的隔離,這種被三星稱為三維堆疊場效應晶體管(3DSFET)的器件就會泄漏電流。實現這種隔離的關鍵步驟是將涉及濕化學品的蝕刻步驟換成一種新型的干式蝕刻。這使得良好器件的產量提高了 80%。

與英特爾一樣,三星也從硅片下方接觸器件底部,以節省空間。不過,這家韓國芯片制造商與美國公司不同的是,在每個配對器件中只使用了 1 片納米片,而不是英特爾的 3 片。據其研究人員稱,增加納米片的數量將提高 CFET 的性能。

當然,除芯片三巨頭之外,其他國家和地區的企業和研究機構也在積極參與 CFET 的開發與研制。

早在 2000 年前后北京大學就已經提出了三維堆疊互補晶體管的概念,并在 2004 年研發完成堆疊互補晶體管的雛形,發表了論文《A stacked CMOS technology on SOI substrate》同時還以第一專利權人在國內申請了專利《一種位于 SOI 襯底上的 CMOS 電路結構及其制作方法》。只是這一概念在當時太過超前,未引起太多關注。

近幾年來,該論文及其后續工作已被國際發明專利引用數百次且受到產業巨頭的推崇,IEDM 2021 大會中英特爾的有關晶體管堆疊技術的邀請報告《Opportunities in 3-D stacked CMOS transistors》中就引用了上述論文,且是引用文獻中時間最早的一篇;臺積電在 VLSI 2021 的報告《CMOS Device Technology for the Next Decade》中指出,北京大學的 3D Stacked CMOS 晶體管是業界第一個堆疊互補晶體管,比臺積電和英特爾要早 15 年。

在 IEDM 2021 上,北京大學集成電路學院發表題為《Demonstration of Vertically-Stacked CVD Monolayer Channels:MoS2 Nanosheets GAA-FET with Ion>700μA/μm and MoS2/WSe2 CFET」》的論文,展示了基于單層二硫化鉬的堆疊圍柵納米片器件,實現了開態電流超過 400μA/μm(@Vd=1V)或 700μA/μm(@Vd=2V),該結果遠超同類器件的文獻報道水平;并通過上百個器件的統計分析,顯示了該器件由三維集成和尺寸縮小帶來的性能提升;同時,首次報道了亞 1 納米溝道厚度的二硫化鉬/二硒化鎢 CFET 器件,實現了反相器邏輯功能。

中科院微電子所在 CFET 結構設計與仿真研究方面也取得了一定進展。2022 年 7 月中科院微電子所集成電路先導工藝研發中心殷華湘/吳振華研究團隊利用業界主流的 Design-Technology Co-optimization(DTCO)方法全面探索了 CFET 的器件架構優勢,提出了新型混合溝道 CFET(Hybrid Channel Complementary FET,HC-CFET)結構設計和集成方案。該結構能夠在單一襯底上,不借助晶圓鍵合等混合晶向技術,利用 SiNx 與 SiO2 的高刻蝕選擇比,通過分步溝道形貌刻蝕,實現對 N-FET 和 P-FET 首選高電子與空穴遷移率導電溝道的共同優化,即使得 N-FET 具有 (100) 溝道表面晶向,P-FET 具有 (110) 溝道表面晶向,從而在同等投影平面下獲得最佳的器件與電路性能。該結構設計與集成方案的可行性已通過 Virtual-FAB 模擬仿真驗證。進一步通過精確數值求解預測了全部寄生參數,對比了不同 CFET 架構下的 17 級環形振蕩器和 SRAM 單元性能。結果表明,相較于常規垂直集成 Fin 和垂直集成納米片的 CFET 結構(MS-CFET 和 MB-CFET),新型 HC-CFET 具有溝道晶向與空間布局優勢,展現出更高的工作頻率以及更優的噪聲容限窗口,以及在高度微縮的高性能 CMOS 集成電路應用上的巨大潛力。該成果以「Investigation of Novel Hybrid Channel Complementary FET Scaling Beyond 3-nm Node From Device to Circuit」為題發表在《電氣和電子工程師協會電子器件學報》期刊上(IEEE Transactions on Electron Devices 69, 3581 (2022), DOI: 10.1109/TED.2022.3176843)。

2022 年 12 月 Nature Electronics 發表了復旦大學微電子學院題為「Heterogeneous Complementary Field-effect Transistors Based on Silicon and Molybdenum Disulfide」的論文,團隊將新型二維原子晶體引入傳統的硅基芯片制造流程,實現了晶圓級異質 CFET 技術。相比于硅材料,二維原子晶體的原子層精度使其在小尺寸器件中具有優越的短溝道控制能力。利用硅基集成電路的標準后端工藝,將新型二維材料 MoS2 三維堆疊在傳統的硅基芯片上,利用兩者高度匹配的物理特性,形成 p 型硅-n 型 MoS2 的異質 CFET 結構。在相同的工藝節點下將集成電路的集成密度翻倍,并獲得了優越的器件性能。

1nm 何時到來?

Tom's Hardware 報道,英特爾在 IFS Direct Connect 大會上的一次閉門活動上確認,按目前計劃,14A 節點的「有意義」規模量產將落在 2026 年;而暫未正式公布的下一個制程節點 10A 預期于 2027 年底投產。

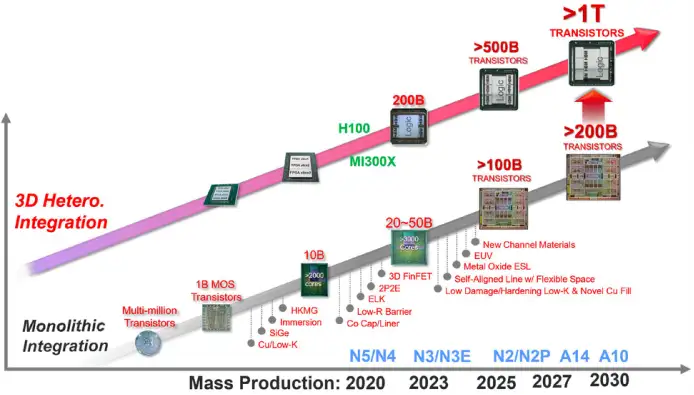

臺積電日前在 2023 年 IEEE 國際電子元件會議(IEDM)上,發布進軍至 1nm 制程的產品規劃藍圖。根據規劃,臺積電將并行推動 3D 封裝和單芯片封裝的技術路徑的發展。預計在 2025 年,臺積電將完成 N2 和 N2P 節點,使得采用 3D 封裝的芯片晶體管數量超過 5000 億個,而采用傳統封裝技術的芯片晶體管數量超過 1000 億個。

然后,臺積電計劃在 2027 年達到 A14 節點,并在 2030 年達到 A10 節點,即 1nm 制程芯片。屆時,采用臺積電 3D 封裝技術的芯片晶體管數量將超過 1 萬億個,而采用傳統封裝技術的芯片晶體管數量將超過 2000 億個。

IBM一直是半導體技術革新的領跑者。2021 年,IBM 宣布推出全球首款 2nm 芯片。與此同時,IBM 也早早開始對 1nm 技術進行研究。在 2022 年末的 IEDM 會議上,IBM 展示了其為通向 1nm 及以上準備的技術:互連 3.0 和 VTFET。

2022 年,日本芯片制造商Rapidus、東京大學將與法國半導體研究機構Leti合作,共同致力于開發 1nm 制程半導體。這種跨國合作模式為技術創新提供了新的視角和資源,有望加速 1nm 技術的研發進程。

2023 年 5 月,Imec公布了其 1nm 以下晶體管的路線圖,展示了未來幾年內實現 1nm 制程的可能路徑和技術難點。Imec 正致力于開發遠超現有技術極限的產品。隨后在 6 月,IMEC 還與 ASML 達成協議,雙方將在開發最先進高數值孔徑(High-NA)極紫外(EUV)光刻試驗線的下一階段加強合作,為使用半導體技術的行業提供原型設計平臺和未開發的未來機遇。

IMEC CMOS 總監 Naoto Horiguchi 在國際電子器件會議演講時表示:「僅使用 GAA 來縮放 CMOS 器件是非常困難的。借助 CFET,我們可以繼續器件擴展,然后可以將其與 Chiplet 和先進封裝等其他技術相結合,以提高芯片性能。CFET 正在為器件的持續擴展開辟一條道路。」IMEC 預計,CFET 架構將在 2032 年左右超越 1nm 節點。

然而,值得注意的是,CFET 面臨的問題還有很多,特別是未來量產過程中,CFET 的制造將更加困難。一方面 CFET 架構比 GAA 架構的 3D 結構更高,結構縱橫比的增加將帶來更大的制造挑戰;另一方面,CFET 需要非常高的摻雜劑激活,需要非常低的接觸電阻率,需要為 CFET 提供特殊的高 k/金屬柵極,而且這些都必須在非常高的堆疊結構中完成。

臺積電表示,CFET 架構的重大挑戰可能會導致工藝復雜性和成本增加。「為了克服這些挑戰,必須仔細選擇集成方案,以降低工藝復雜性,并最大限度地減少對新材料和工藝能力的要求。」臺積電器件架構開拓總監 Szuya Liao 表示,「參與早期 EDA/流程工具開發,為重大設計變更做好準備也很重要。」

評論