FOPLP,備受熱捧

半導體行業作為現代電子技術的基石,其持續進步為電子產品的性能提升和成本降低提供了源源不斷的動力。隨著芯片設計復雜性的增加和系統集成度的提高,布線密度的提升成為必然的趨勢。同時,隨著物聯網、云計算、大數據等技術的迅猛發展,設備之間的通信和數據傳輸需求也呈現出爆炸性增長,I/O 端口需求的增加成為了另一個推動半導體技術發展的關鍵因素。

本文引用地址:http://www.j9360.com/article/202405/458979.htm在這樣的背景下,傳統的封裝技術已經難以滿足日益增長的性能和集成度要求。因此,半導體行業不斷探索新的封裝技術,以應對布線密度提升和 I/O 端口需求增加帶來的挑戰。扇出型封裝(Fan-out Packaging)作為一種先進的封裝技術,憑借其獨特的優勢,逐漸成為了半導體封裝領域的新寵。

Fan-out 封裝的特點

體積更小:Fan-out 封裝不需要封裝基板,因此能實現薄型化封裝的需求。通過 Fan-out 封裝技術,不同的芯片可以被整合成一個單一的二維封裝體,實現了體積薄型化的 SiP(System in Package)封裝技術,這改變了原本需要利用直通硅晶穿孔 (TSV) 將數顆芯片做垂直疊加封裝的方式。

效能更強:在相同的芯片尺寸下,Fan-out 封裝可以實現范圍更廣、層數更多的重分布層 (Redistribution Layer, RDL)。由于 RDL 層數的增加,芯片的引腳數 I/O 也隨之增多。各種不同功能的芯片通過 RDL 聯結的方式整合在單一封裝體中,其功能性將更加強大。

成本較低:采用 Fan-out 封裝技術所生產的封裝體,能夠大幅縮短繁復的過程,并減少材料的使用,從而有效降低生產成本,實現低成本化的優點。

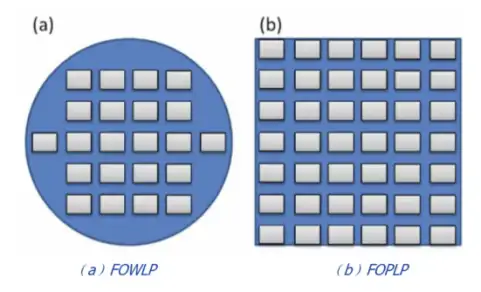

扇出型封裝主要分為扇出型晶圓級封裝 (Fan-Out Wafer Level Packaging, FOWLP) 和扇出型板級封裝 (Fan-Out Panel Level Packaging, FOPLP) 兩種。

作為異質整合封裝的新興技術,扇出型封裝技術發展至板級,因能以更大面積進行生產,達到既可以進一步降低生產成本又能滿足市場端對芯片效能的需求的目的,正成為先進封裝技術中能夠提供異質整合,同時又能降低生產成本的最有潛力的技術平臺。

具體看看,FOPLP 相比 FOWLP 都有哪些具體優勢,各自適用于哪些應用領域。

FOWLP 與 FOPLP 的較量

FOWLP 是晶圓級封裝(WLP)的一種。WLP 與傳統封裝不同點在于切割晶圓與封裝的先后順序。傳統封裝工藝步驟中,封裝要在裸片切割分片后進行,而晶圓級封裝是先進行封裝再切割。

回顧一下 WLP。WLP 于 2000 年左右問世,有兩種類型:Fan-in(扇入式)和 Fan-Out(扇出式)。開始 WLP 多采用 Fan-in 型態,可稱之為 Fan-in WLP 或者 FIWLP,主要應用于面積較小、引腳數量少的芯片。

隨著 IC 工藝的提升,芯片面積縮小,芯片面積內無法容納足夠的引腳數量,因此衍生出 Fan-Out WLP 封裝形態,也稱為 FOWLP,實現在芯片面積范圍外充分利用 RDL 做連接,以獲取更多的引腳數。

FOPLP 借鑒了 FOWLP 的思路和技術,但采用了更大的面板。因此,FOPLP 具備顯著的產能、效率提升和成本降低優勢。其高面積利用率有效減少了浪費,同時能夠在一次封裝過程中處理更多的芯片,顯著提高了封裝效率,形成強大的規模效應,從而具有極強的成本優勢。

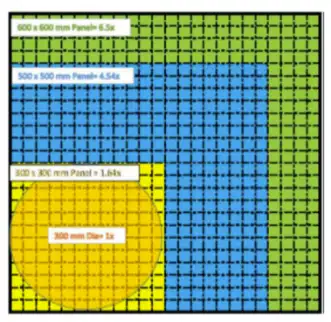

根據 Yole 報告,例如 FOWLP 技術面積使用率<85%,FOPLP 面積使用率>95%,可以放置更多的芯片數,成本也比 FOWLP 便宜;面板級封裝的成本與晶圓級封裝相比將會降低 66%。

來源:日月光,國盛證券研究所

FOPLP 擁有更高的面積利用率。來源:STATS ChipPAC & Rudoph Technologies

此外,FOPLP 的基板選材也更加靈活,可以采用玻璃基板或是金屬基板。

據 Yole 的報告顯示,隨著基板面積的增加,芯片制造成本逐漸下降。從 200mm 過渡到 300mm 大約能節省 25% 的成本,而從 300mm 過渡到板級封裝,則能節約高達 66% 的成本。

FOPLP 與 FOWLP 各自有各自的細分方向,FOWLP 側重于直接在晶圓上進行封裝,具有尺寸小、集成度高的特點,適用于高性能、高密度的應用場景,比如 CPU、GPU、FPGA 等大型芯片的生產;而 FOPLP 則通過在面板級別進行封裝,提供了更大的封裝尺寸和更高的生產靈活性,能夠滿足更多樣化的封裝需求。FOPLP 聚焦在高功率、大電流的功率半導體產品應用,不需要最先進的制程和設備,也不需要太細的線寬/線距,應用于 I/O 數約 10-500 個的 APE、PMIC、功率器件等芯片的生產。

FOPLP 作為先進封裝技術發展的一個重要分支,正在受到諸多廠商的追捧。

CoWoS 短缺,FOPLP 迎來契機

先進封裝最受市場矚目的是 CoWoS。CoWoS 可以分開來看,CoW(Chip-on-Wafer)指的是芯片堆疊,WoS(Wafer-on-Substrate)則是將堆疊的芯片封裝在基板上。根據排列的形式,分為 2.5D與 3D,不僅可以減少芯片所需的空間,也有效減少功耗,借此達到加速運算但成本仍是可控的目標。

隨著 ChatGPT 橫空出世,生成式 AI 紅遍全球,帶動 AI 芯片的需求強勁,英偉達(NVIDIA)的 H100、A100 全部由臺積電代工,并使用臺積電的 CoWoS 先進封裝技術,除了英偉達外,AMD MI300 也導入 CoWoS 技術,造成 CoWoS 產能供不應求。

因此不少廠商開始尋找某種其他的方案來解決產能問題,這也給 FOPLP 封裝帶來了新的機遇。

蘇州晶方半導體副總經理劉宏鈞表示:由于其工藝尺寸原因,FOPLP 技術指標弱于臺積電的 CoWoS-S,但其潛在優勢是成本和產能瓶頸突破的可能性。這些因素促使目前 CoWoS 的用戶努力尋找替代技術。

作為扇出封裝的后起之秀,FOPLP 正在以更低成本、更大靈活性而受到全行業的矚目。因此 FOPLP 也成為諸多大廠的選擇。

FOPLP 在這些市場發光發熱

近幾年,AIoT、5G、自動駕駛和光伏儲能行業的發展,大大拉動了功率器件、傳感器芯片和射頻芯片市場的需求。

根據 Prismark 的預測,到 2026 年,5G&物聯網、車用電子將成為唯二增加市場占有率的應用,占總體半導體營收近 30%;其中,在車載領域,伴隨著汽車新四化的演進,以往一輛傳統汽車使用 500-600 顆左右的芯片,如今平均每輛車所需芯片數量已經達到了 1000 顆-2000 顆,因此車用芯片將成為芯片成長率最高的應用類別。

汽車電子的快速發展讓扇出型封裝的重要性愈發明顯。一輛新能源汽車中半導體價值的 77% 都將以扇出型封裝來生產,而這其中的 66% 又可以歸屬于 FOPLP 技術。

此外,FOPLP 依托精密的重布線層(RDL)工藝,實現了芯片間(D2D)的高速、高密度互連,這一特質對于 AI 計算至關重要,確保了龐大數據流的無縫傳輸與高效處理,直擊 AI 時代的數據處理痛點。更進一步,FOPLP 在增強芯片功能集成度、縮減互聯距離及促進系統設計創新方面展示出的明顯優勢,恰與 AI 時代對芯片提出的高性能、高集成度標準不謀而合,為智能計算的未來鋪設了堅實的基石。

因此,從應用市場的角度來看,未來 FOPLP 技術前景廣闊。究其核心在于,在眾多先進封裝技術之中,板級封裝技術因具備大產能且更具成本優勢,是目前高速成長的功率器件、傳感器、通信等車規級芯片生產的最佳解決方案。

諸多廠商熱捧

在 FOPLP 方面,三星是絕對的引領者。在 2018 年,三星電機通過為三星 Galaxy Watch 推出具有扇出型嵌入式面板級封裝(ePLP)PoP 技術的 APE-PMIC 設備,實現了新的里程碑。三星電機繼續為具有成本效益的高密度扇出封裝進行創新,以便再次與臺積電競爭蘋果的封裝和前端業務。

去年,三星旗下 DS 部門的先進封裝(AVP)業務團隊開始研發將 FOPLP 先進封裝技術用于 2.5D 的芯片封裝上。借由此技術,三星預計可將 SoC 和 HBM 整合到硅中間層上,進一步建構其成為一個完整的芯片。

從國際學術會議上三星發表的 FOPLP 相關論文來看,三星正在致力于開發 FOPLP 先進封裝技術,以克服 2.5D 封裝的局限性。所以,一旦三星成功應用 FO-PLP 先進封裝技術,將能與其晶圓代工和內存業務產生協同效應。因此,三星正在借由提出一站式方案(Turn-key)來吸引客戶,也就是借由為 AI 設計廠商(例如 NVIDIA 和 AMD)生產半導體、再加上提供 HBM 和封裝技術來吸引客戶。所以,如果在封裝方面變得有競爭力,則三星將能壯大其半導體業務。臺積電因 2.5D 先進封裝在半導體代工市場上發揮了巨大的影響力。業內人士表示,三星或許計劃利用 2.5D 先進封裝技術來追趕臺積電。

日月光也是最早布局面板級扇出型技術的領導廠家之一。于 2019 年底產線建置完成,2020 下半年量產,應用在 RF、FEM、Power 和 Server 領域。2022 年日月光推出了 VIPack 先進封裝平臺,提供垂直互聯集成封裝解決方案。VIPack 就是以 3D 異質整合為關鍵技術的先進互連技術解決方案,建立完整的協同合作平臺。

此外,還有力成、群創等廠商結合自身的工藝能力投資扇出型板級封裝技術的量產。隨著 FOPLP 越來越受重視,近幾年行業內已經有不同商業模式的廠商加入這一市場爭奪戰,包括 IDM 廠、代工廠、封裝廠,甚至面板廠、PCB 廠等等,他們已強烈感應到通過扇出型技術涉足先進封裝領域的機會。

中國大陸扇出面板級封裝廠商也正乘勝追擊,目前多家廠商已經量產或具備生產能力。比如:

華潤微、奕斯偉、中科四合、天芯互聯等都已切入扇出型面板級封裝。

華潤微電子于 2018 年成立矽磐微電子(重慶)公司從事面板級封裝業務,面板級封裝技術有效解決了 Chiplet 封裝成本高昂的問題,更適用于功率類半導體封裝異構集成化。據悉,矽磐擁有先進封裝領域的市場、設計、設備、工藝和材料等各個環節的世界級團隊,可為客戶提供全方位 Fan-out 封裝技術解決方案——ONEIRO 封裝。

成都奕斯偉系統集成電路有限公司成立于 2017 年,隸屬于北京奕斯偉科技集團有限公司,核心事業涵蓋芯片與方案、硅材料、先進封測三大領域。成都奕斯偉系統集成電路有限公司是北京奕斯偉布局在成都的先進 FOPLP(面板級扇出型)封測基地,為客戶提供高性價比的系統集成封裝與測試服務。

天芯互聯科技有限公司為深南電子旗下全資子公司,天芯互聯依托系統級封裝(SiP)和板級扇出封裝(FOPLP)平臺,為客戶提供高集成小型化的半導體器件模組封裝解決方案和半導體測試接口解決方案,產品廣泛應用于高端醫療、工控、通信、半導體測試等領域。公司在深圳和無錫兩地均設有研發團隊和制造工廠,為客戶提供方案評估、設計仿真、封裝測試等一站式服務。天芯互聯科技有限公司無錫分公司目前在開展扇出型晶圓級封裝技術的研究。

中科四合也在致力于建設板級功率芯片扇出型封裝工藝制造平臺,并以此平臺為基礎開展先進 Fan-out 封裝工藝技術研究與功率芯片/模組產品研究,面向消費類電子、工控、汽車電子、通信/服務器、醫療等各種不同領域客戶進行新型高密度功率芯片/模組產品研發、制造、銷售,產品類型涵蓋 TVS、MOSFET、SBD、Bridge、DC-DC、IPM 等多種器件和模組。目前,中科四合已量產基于板級扇出型封裝的 DFN 類 TVS 系列產品。該 TVS 產品系列已在小米、海爾、海信等終端品牌中實現批量應用。

掣肘和機遇

當下仍需注意的是,FOPLP 要全面發展,面臨的制約因素還有不少,由于在工藝實現的過程中涵蓋了多種設備、工藝難點,面臨精度、效率和速度等多重挑戰。其中,面板尺寸和組裝工藝未能標準化是 FOPLP 應用的最大障礙。同時,FOPLP 封裝尺寸雖大,良率還不及 FOWLP,所以提高良率也是其發展重點。

未來,隨著 FOPLP 技術的不斷成熟和完善,以及更多不同領域的廠商加入這一陣營,扇出型封裝技術有望逐步走向成熟與普及。

根據 YoleIntelligence 在 2023 年發布的扇出封裝市場報告中的預測,FOPLP 市場規模將從 2022 年的 4100 萬美元迅速擴大,預計在 2028 年將以 32.5% 的復合年增長率增長至 2.21 億美元。

與此同時,FOPLP 的市場份額在 FOWLP 市場中的占比也將從 2022 年的 2% 攀升至 2028 年的 8%。

在不遠的將來,FOPLP 將憑借其獨特的優勢,迎來全面爆發的時刻。

評論