臺積電準備推出基于12和5nm工藝節點的下一代HBM4基礎芯片

在 HBM4 內存帶來的幾大變化中,最直接的變化之一就是內存接口的寬度。隨著第四代內存標準從已經很寬的 1024 位接口升級到超寬的 2048 位接口,HBM4 內存堆棧將不會像以前一樣正常工作;芯片制造商需要采用比現在更先進的封裝方法,以適應更寬的內存。

本文引用地址:http://www.j9360.com/article/202405/458830.htm作為 2024 年歐洲技術研討會演講的一部分,臺積電提供了一些有關其將為 HBM4 制造的基礎模具的新細節,這些模具將使用邏輯工藝制造。由于臺積電計劃采用其 N12 和 N5 工藝的變體來完成這項任務,該公司有望在 HBM4 制造工藝中占據有利地位,因為內存工廠目前還不具備經濟地生產這種先進邏輯芯片的能力(如果它們能生產的話)。

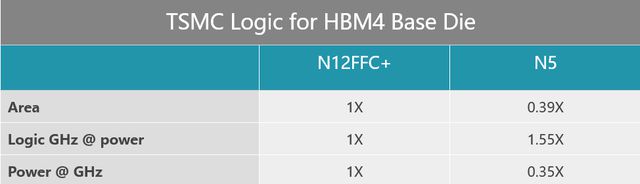

對于第一波 HBM4,臺積電準備采用兩種制造工藝:N12FFC+ 和 N5。雖然它們的目的相同--將 HBM4E 內存與下一代 AI 和 HPC 處理器集成,但它們將以兩種不同的方式連接用于 AI 和 HPC 應用的高性能處理器內存。

臺積電設計與技術平臺高級總監表示:"我們正與主要的 HBM 存儲器合作伙伴(美光、三星、SK 海力士)合作,在先進節點上實現 HBM4 全堆棧集成。N12FFC+高性價比基礎芯片可以達到HBM的性能,而N5基礎芯片可以在HBM4速度下以更低的功耗提供更多的邏輯。"

臺積電采用 N12FFC+ 制造工藝(12 納米 FinFet Compact Plus,正式屬于 12 納米級別的技術,但其根源來自臺積電久經考驗的 16 納米 FinFET 生產節點)制造的基礎芯片將用于在系統級芯片(SoC)旁邊的硅中間件上安裝 HBM4 存儲器堆棧。臺積電認為,他們的 12FFC+ 工藝非常適合實現 HBM4 性能,使內存供應商能夠構建 12-Hi(48 GB) 和 16-Hi 堆棧(64 GB),每堆棧帶寬超過 2 TB/秒。

高級總監說:"我們還在為 HBM4 優化 CoWoS-L 和 CoWoS-R。CoWoS-L和CoWoS-R都[使用]超過八層,以實現HBM4的2000多個互連的路由,并具有[適當的]信號完整性"。

N12FFC+ 上的 HBM4 基礎芯片將有助于使用臺積電的 CoWoS-L 或 CoWoS-R 先進封裝技術構建系統級封裝 (SiP),該技術可為內插件提供高達 8 倍網紋尺寸的空間,足以容納多達 12 個 HBM4 存儲器堆棧。根據臺積電的數據,目前,HBM4 在電流為 14mA 時的數據傳輸速率可達 6 GT/s。

臺積電代表解釋說:"我們與 Cadence、Synopsys 和 Ansys 等 EDA 合作伙伴合作,對 HBM4 通道信號完整性、IR/EM 和熱精度進行認證。"

同時,作為更先進的替代方案,內存制造商還可以選擇臺積電的 N5 工藝來生產 HBM4 基礎芯片。采用 N5 工藝的基礎芯片將包含更多的邏輯,功耗更低,性能更高。但可以說最重要的好處是,這種先進的工藝技術將實現非常小的互連間距,大約為 6 至 9 微米。這將使 N5 基本芯片與直接鍵合技術結合使用,從而使 HBM4 可以直接在邏輯芯片上進行三維堆疊。直接鍵合技術可實現更高的內存性能,這對于一直在渴求更多內存帶寬的人工智能和高性能計算芯片來說將是一個巨大的推動。

我們已經知道臺積電和 SK Hynix 正合作開發 HBM4 基礎芯片。臺積電很可能也會為美光生產 HBM4 基礎芯片。否則,我們會更驚訝地看到臺積電與三星合作,因為這家企業集團已經通過其三星代工部門擁有了自己的先進邏輯晶圓廠。

評論