Chiplet:后摩爾時代關鍵芯片技術,先進封裝市場10年10倍

大家好,我是小胡。在前面的內容我們講國內六大CPU廠商的時候,發現了一個問題,就是國產CPU后續工藝迭代的問題。

本文引用地址:http://www.j9360.com/article/202303/444982.htm

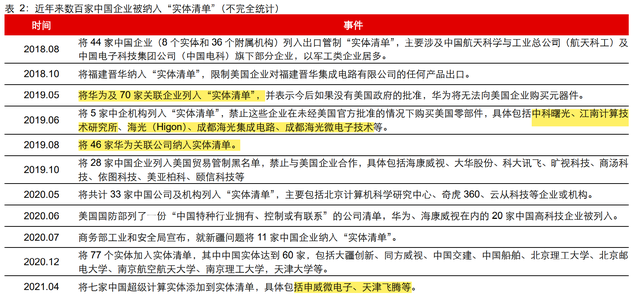

除了華為鯤鵬以外,其余五大CPU廠商目前主力芯片的制程工藝都在10nm以上,而六大廠商當中有四家被列入實體清單,鯤鵬920雖然是7nm工藝,但這兩年一直依靠庫存支撐,芯片供應鏈問題一直是國產CPU無法回避的問題。

今天我們就來跟大家聊聊芯粒技術,并挖掘A股相關的投資機會。

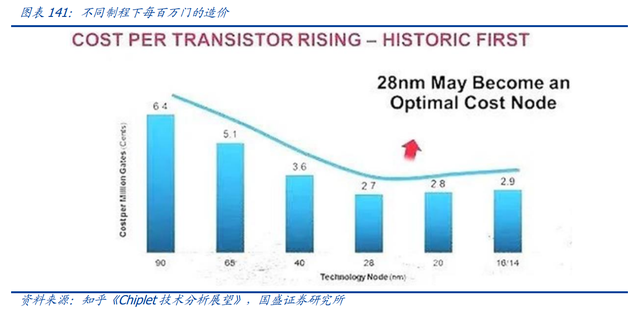

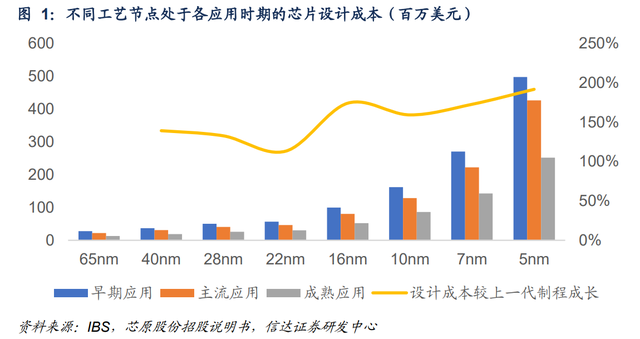

而芯片的設計成本到28nm以下成倍地增加,這就導致工藝升級對芯片性能提升的邊際收益縮窄,通常只有15%左右,也就是后摩爾時代經濟效能提升出現了瓶頸。

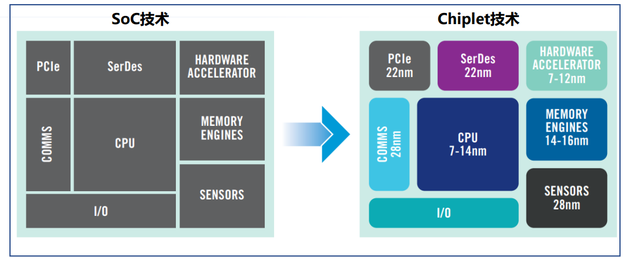

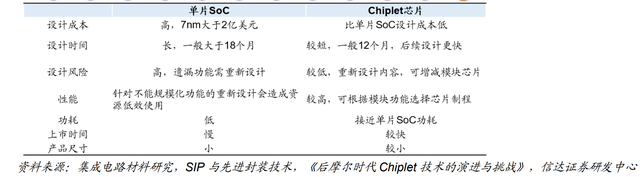

我們看傳統SoC技術與Chiplet技術的對比,傳統SoC芯片是把不同的IP核用相同的工藝制造在同一塊晶圓上面,比如CPU、內存、顯示控制這些模塊都是7nm。

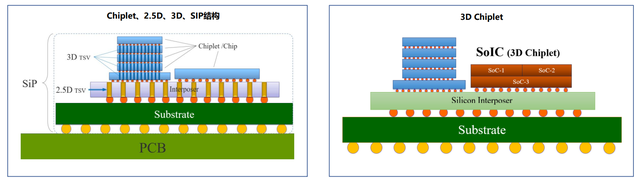

而Chiplet技術是在設計時就把不同IP核分開設計,按照需求選擇合適的工藝分別制造,比如CPU用7nm,內存用14nm,顯示控制用28nm。

最后再通過先進封裝技術將各個單元彼此互聯,最終集成封裝成一個系統級芯片組。

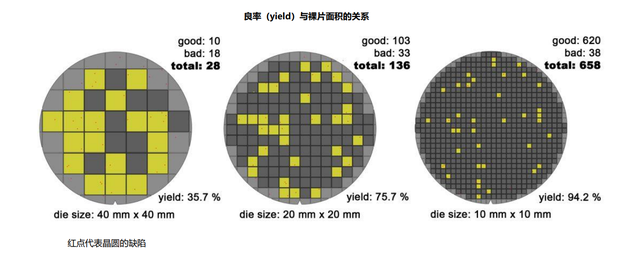

Chiplet有三大優勢,首先是高良品率,SoC是大芯片,裸片的面積大,出現一點缺陷一大塊都廢掉了,Chiplet是多顆小芯片分開制造,將裸片的面積做小,能大幅提高良品率。

其次是Chiplet具有高設計彈性,SoC芯片采用統一的制程工藝,導致芯片上各個IP核需要同步迭代,而Chiplet芯片采用先進封裝工藝,由小芯片組合構成,可以對芯片上部分模塊進行選擇性地迭代,研發周期更短,節省研發投入。

最后是低成本,在7nm相同方案下,Chiplet的良品率比SoC提高將近一倍,而成本下降了13%。

綜合來看,Chiplet相較傳統SoC具有多方面的優勢,既降低了成本,又提高了經濟效益,是后摩爾時代的發展趨勢。

那么到這里就可以回答很多人的疑問,Chiplet能不能讓國產芯片彎道超車?

答案是不能。

超大芯片與先進制程最受益Chiplet技術,國內主要產線均是成熟工藝,成熟工藝大芯片分小芯片制造,甚至用更落后的工藝制造的話,達不到降本增效目的,反倒可能增加成本,因為落后工藝單位晶體管成本本就偏高。

其實華為在19年推出的鯤鵬920芯片當時就用到了Chiplet技術,性能優異;國產芯片制造技術的提升,解決供應鏈問題,還是得依靠自主、先進的設備、材料,與晶圓廠共同推進,制造工藝的進步目前看沒有捷徑。

不過,Chiplet技術給我們帶來了新的投資機遇。

先進封裝迎新機遇

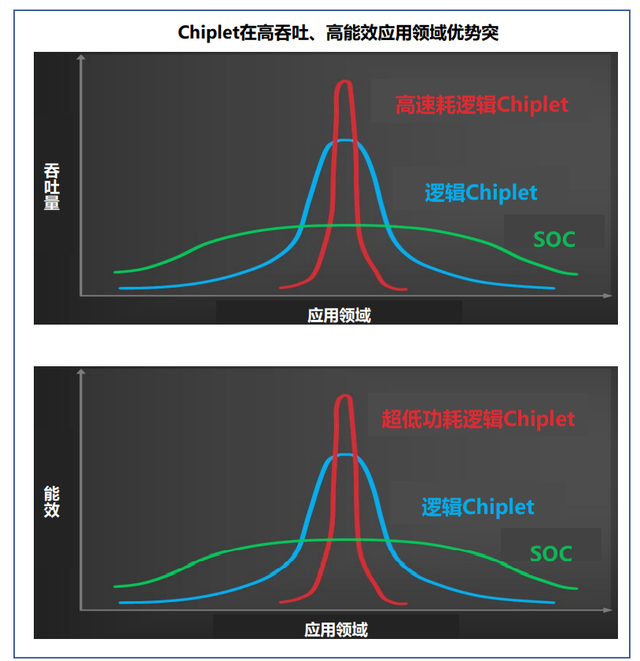

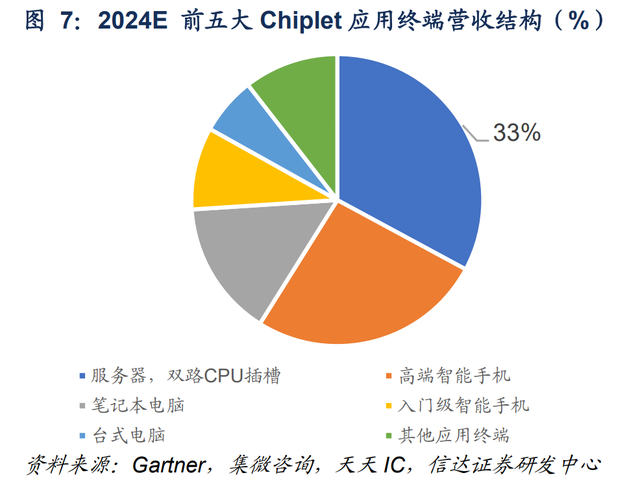

從Chiplet芯片需求來看,主要應用于服務器、高端智能手機和筆記本電腦。

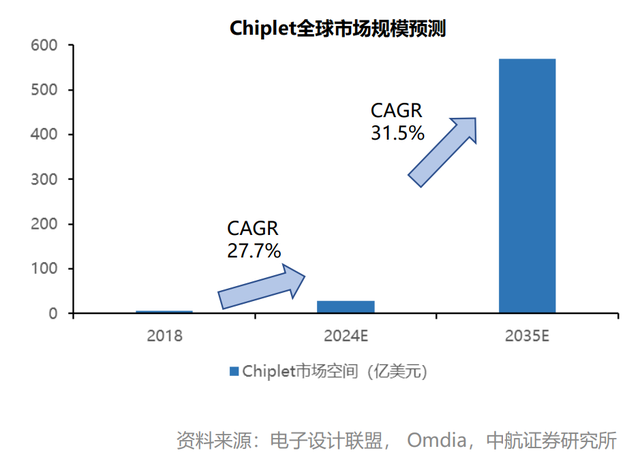

從空間來看,機構預測Chiplet市場將在2024年達到58億美元,并以每年31.5%的年復合增速,在2035年達到570億美元,10年10倍,目前Chiplet處于發展初期,未來的增速很快,有望重新拉動封測行業增長。

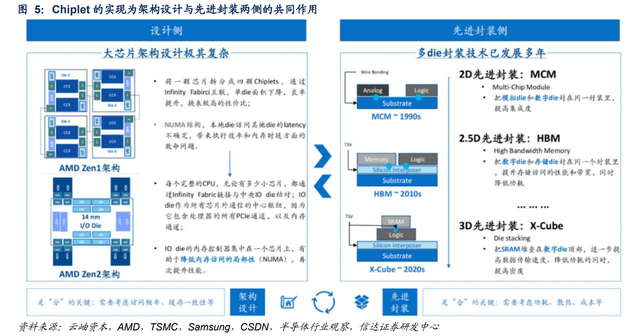

Chiplet實現的核心是先進封裝,用先進封裝把小芯片“合”好,但光有先進封裝也不行,還需要上游設計和中游制造把大芯片“分”好,上下游協同,我們主要看好先進封裝及芯片測試相關的公司。

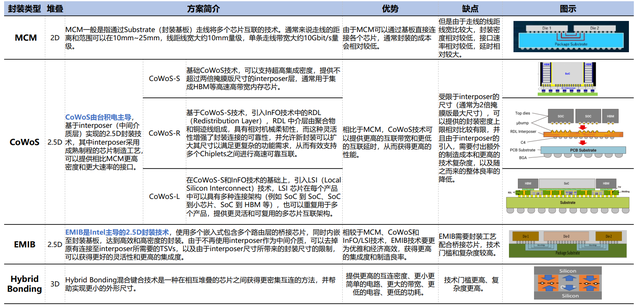

全球來看,具有前道工藝的代工廠或IDM企業在先進封裝技術研發與產業化方面具有技術、人才和資源優勢,利用前道技術的封裝技術逐漸顯現,目前支持Chiplet 技術的主流底層封裝技術主要由臺積電、ASE、Intel主導。

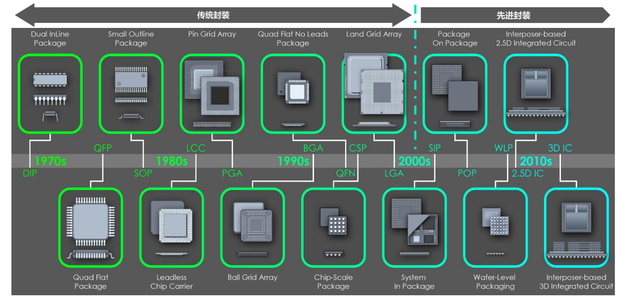

目前可用于Chiplet封裝解決方案主要是SIP、2.5D和3D封裝技術,其中,2.5D封裝技術發展已經非常成熟,并且廣泛應用于FPGA、CPU、GPU等芯片當中,近年來,隨著Chiplet架構的興起,2.5D封裝成為了 Chipet 架構產品主要的封裝解決方案。

為了節省芯片面積,未來,封裝也將從2D/2.5D轉向3D 疊,3D封裝能夠實現芯粒間的堆疊和高密度互聯,可以提供更為靈活的設計選擇,但是,3D封裝的技術難度也更高,目前主要英特爾和臺積電掌握3D封裝技術并實現商用。

評論