IBIS建模——第2部分:為何以及如何創建您自己的IBIS模型

本文引用地址:http://www.j9360.com/article/202204/433293.htm

簡介

在構建任何系統時,仿真都發揮著關鍵作用。它幫助設計人員預見問題,進而避免費時且成本高昂的修改。我們的目標始終是一次就成功!在仿真高速數字接口時,如果設計不當,簡單的PCB走線可能會影響信號質量。在信號完整性仿真中,IBIS(輸入/輸出緩沖器信息規范)模型用來表示器件的數字接口。

如IBIS系列文章的第1部分所述,IBIS是一個行為模型,通過以表格形式列出的電流與電壓(I-V)和電壓與時間(V-T)數據來描述器件的數字接口的電氣特征。IBIS模型應盡量準確,且不含任何解析錯誤,避免在之后使用時出現問題。此外,對于具有數字接口的每個部件或器件,都應該提供可用的IBIS模型。這樣客戶需要時,可直接從制造商的網頁上下載。但是,事實并非總是如此。對于IBIS模型用戶,他們常遇到的一個問題就是模型的可用性。當他們在設計中選用的部件沒有IBIS模型時,其產品開發可能受阻。

IBIS模型最好是由其制造商提供;但是,用戶也可以創建IBIS模型。本文介紹如何使用LTspice,基于SPICE模型創建最基礎的IBIS模型。下文使用IBIS建模手冊(IBIS 4.0版)中的規格來介紹LTspice仿真設置。還要介紹如何使用定性和定量品質因數來驗證IBIS模型。

何謂“最基本的”IBIS模型?

為了幫助客戶使用LTspice創建基本的IBIS模型,需要先定義“基本”一詞。基本的IBIS模型不僅取決于I/O模型關鍵字,還取決于需要建模的數字緩沖器的類型。這意味著需要重新審視IBIS的早期版本,以定義建立緩沖器模型需要滿足的最低要求,以及當時建模的數字接口的類型。事實證明,單端CMOS緩沖器是可以使用IBIS建模的最簡單的數字IO之一,本文將予以介紹。

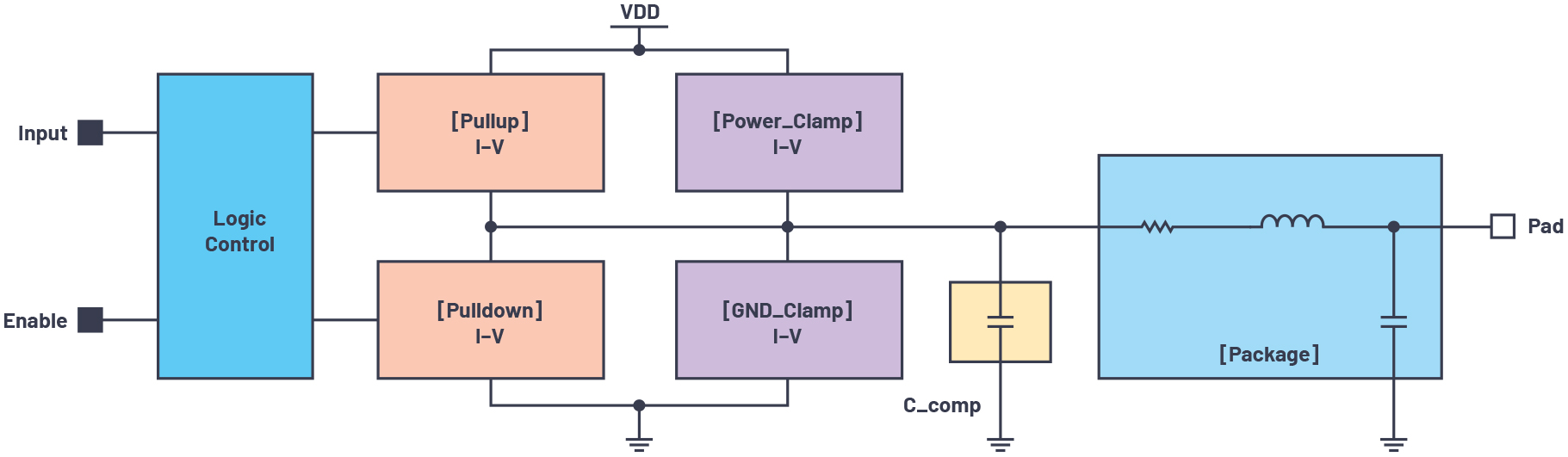

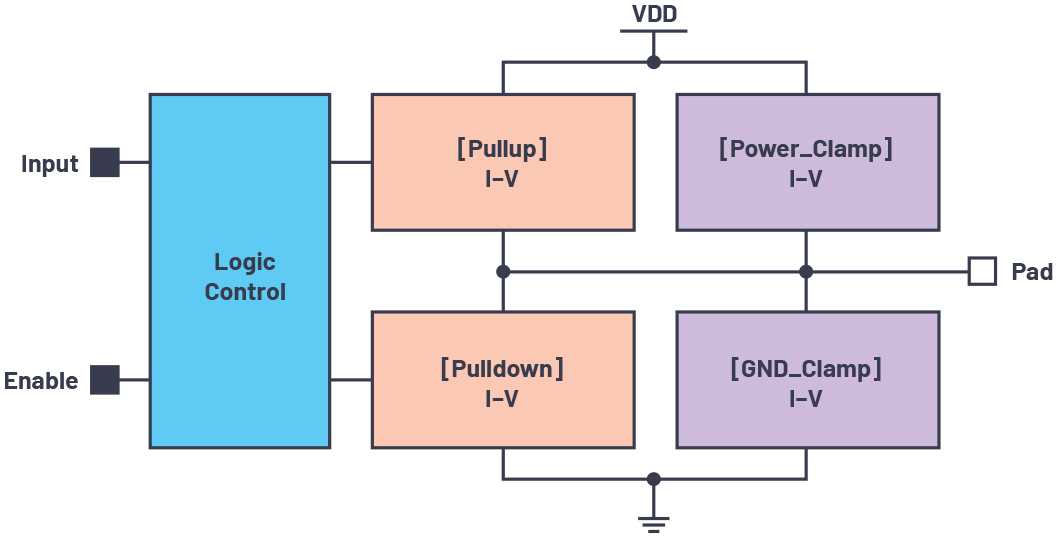

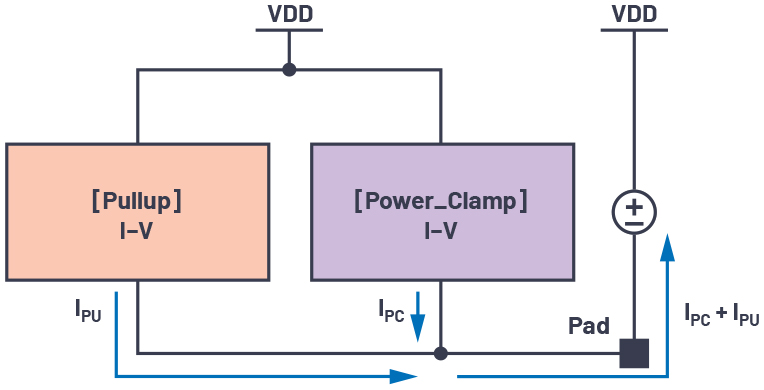

圖1 3態CMOS緩沖器的IBIS模型

表1 基于Model_type的IBIS模型組件匯總

Model_type | [封裝] | C_comp | [GND_ Clamp] | [Power_ Clamp] | [下拉] | [上拉] | V-T表 | [斜坡] |

輸入 | ? | ? | ? | ? | — | — | — | — |

3態 | ? | ? | ? | ? | ? | ? | ? | ? |

I/O | ? | ? | ? | ? | ? | ? | ? | ? |

圖1顯示3態CMOS緩沖器IBIS模型的結構。如第1部分所述,IBIS模型中的組件或關鍵字取決于模型類型。表1匯總列出基本的IBIS模型的組件,具體由Model_type決定。

應用案例

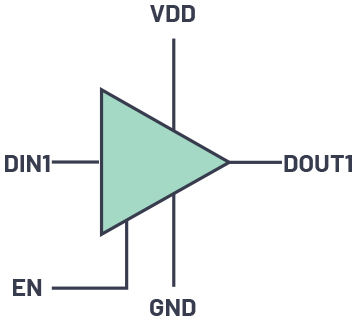

在本文中,我們將使用一個假設的ADxxxx器件的LTspice模型來創建IBIS模型。它是一個帶有使能引腳的單輸入和單輸出數字緩沖器。因此,得到的IBIS模型將具有兩個輸入(DIN1和EN)、一個三態輸出(DOUT1)。

一般來說,生成IBIS模型有五個基本步驟:

■ 建立預建模程序。

■ 對從SPICE模型中提取的C_comp、V-I和V-T數據進行LTspice仿真。

■ 格式化IBIS文件。

■ 使用IBIS解析器測試檢查文件。

■ 比較IBIS模型與SPICE模型在相同加載條件下的仿真結果。

IBIS模型提供典型數據、最小數據和最大數據。它們通過工作電源電壓范圍、溫度和工藝來確定[HA1]。為簡潔起見,本文只討論典型條件。

Ibischk Golden Parser系列可用于檢查IBIS模型是否符合IBIS規范。ibischk可執行文件可從IBIS.ORG網頁免費獲取。本文使用集成ibischk的第三方IBIS模型編輯軟件。

預建模程序

在開始仿真之前,用戶應該下載器件的數據手冊,并安裝SPICE模型和LTspice文件。通過確定部件具備的數字接口數量和類型(例如,輸入、開漏、三態等),對部件進行初始評估。

根據器件數據手冊,確定工作電源電壓、工作溫度、集成電路(IC)封裝類型、器件引腳排列、數字輸出時序規格的加載條件(RLoad和/或CLoad),以及數字輸入的低電平輸入電壓(VINL)和高電平輸入電壓(VINH)。ADxxx SPICE模型如圖1所示,其指標參數列在表2。

通過使用關鍵字,將有關器件數字接口的所有信息匯集到一個IBIS文件中。關鍵字是IBIS模型中用括號括起來的標識符,如第1部分所述。更多詳細信息請參閱此部分內容。

圖2 Adxxxx 3態數字緩沖器SPICE模型

表2 ADxxxx數據手冊參數

數據手冊參數 | 值 |

VDD | 1.8 V(典型值) |

工作溫度 | 25°C |

VINL | 0.3 × VDD |

VINH | 0.7 × VDD |

IC封裝 | 6引腳SOT-23 |

CLoad | 15 pF |

與IC封裝模型相關的關鍵字是[Package]。它包含RLC(電阻-電感-電容)寄生參數,代表從芯片焊盤到IC焊盤/引腳的連接。此信息可從制造商處獲得。也可以查找另一個IBIS文件的[Package]數據,只要該器件采用的封裝與正在評估的器件完全相同,并且來自同一制造商。6引腳SOT-23封裝的器件封裝寄生參數如表3所示。

表3 6引腳SOT-23封裝寄生參數

[封裝] | |||

變量 | 典型值 | 最小值 | 最大值 |

R_pkg | 1.595E-01 | NA | NA |

L_pkg | 4.455E-09 | NA | NA |

C_pkg | 0.370E-12 | NA | NA |

器件引腳排列如表4所示。關鍵字[Pin]用于描述引腳及其對應的模型名稱。[Pin]一般為3列格式。第一列是引腳編號,第二列是引腳描述,第三列是模型名稱。有些封裝包含[HA2]類似的引腳(VCC、GND)。這些引腳可以按模型分組和描述。在這種情況下,由于SPICE模型沒有給出有關內部晶體管級原理圖的信息,因此最好為每個數字接口創建單獨的模型。在IBIS文件中,模型名稱“Power”和“GND”用于命名電源和接地引腳。非數字接口和“請勿連接”引腳則描述為“NC”或無連接。請注意,模型名稱是區分大小寫的。由于在稍后的建模程序中還會用到,所以需給出具體的模型名稱。

表4 ADxxxx引腳列表

[Pin] | Signal_name | Model_name |

1 | VDD | Power |

2 | DIN1 | cmos_di1 |

3 | EN | cmos_en |

4 | DOUT1 | cmos_out1 |

5 | GND | GND |

6 | NC | NC |

ADxxxx真值表如表5所示。這在建立LTspice仿真時非常有用。還必須要知道如何將DOUT1引腳設置為高阻抗(高阻)模式、邏輯1和邏輯0。

表5 ADxxxx真值表

EN | DIN1 | DOUT1 |

0 | 0 | 高阻 |

0 | 1 | 高阻 |

1 | 0 | 0 |

1 | 1 | 1 |

LTspice設置和仿真

一般來說,IBIS模型通過前面提到的I-V(電流與電壓)和V-T(電壓與時間)數據描述數字緩沖器的行為。進行IBIS建模時,每種類型的數字接口都擁有[HA3]一組自己的I-V和/或V-T數據,如表1所示。表6更加詳細地列出了這些數據集。注意查看每個數據集的注釋。那些標記為“推薦”的數據,表示這些數據缺失不會在ibischk解析器測試中導致誤差。但是,這些數據集對通道仿真有一定的作用。例如,鉗位數據有助于分析信號反射。

表6 輸入和3態接口的I-V和V-T數據集

IBIS關鍵字 | 輸入 | 3態 | ||

V-I數據 | C_comp | 必需 | 必需 | |

[Power_Clamp] | 推薦 | 推薦 | ||

[GND_Clamp] | 推薦 | 推薦 | ||

[上拉] | — | 必需 | ||

[下拉] | — | 必需 | ||

V-T數據 | [上升波形] | 加載至VDD | — | 推薦 |

加載至GND | — | 推薦 | ||

[下降波形] | 加載至VDD | — | 推薦 | |

加載至GND | — | 推薦 | ||

[斜坡] | — | 必需 | ||

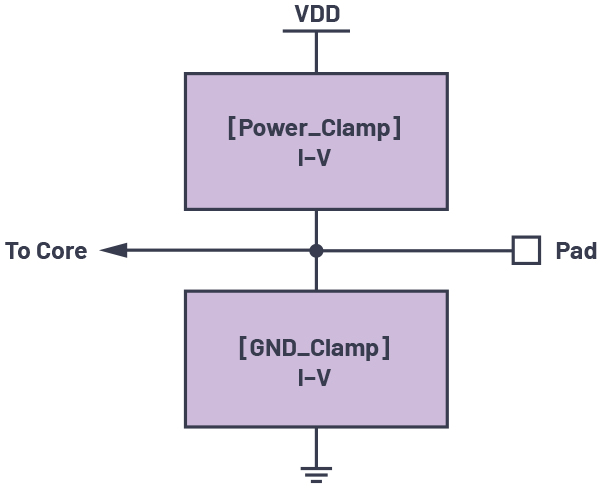

[Power_Clamp]和[GND_Clamp]

圖3 [Power_Clamp]和[GND_Clamp]關鍵字結構的概念圖

[GND_Clamp]和[Power_Clamp]通過以表格形式列出的I-V數據顯示數字緩沖器的靜電放電(ESD)器件的行為。[Power_Clamp]表示以VDD為基準的ESD器件的整體行為,接地箝位表示以GND為基準的ESD器件的整體行為。

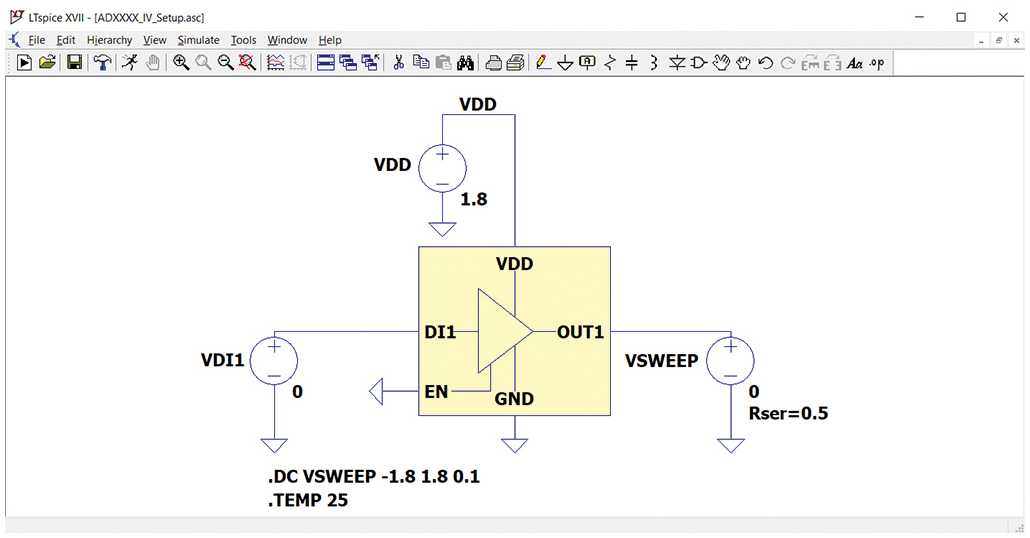

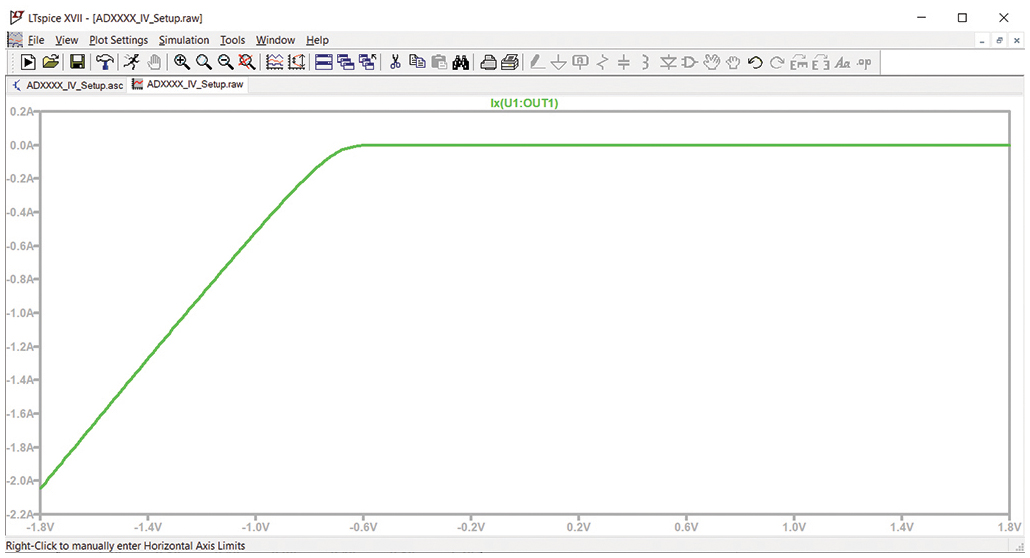

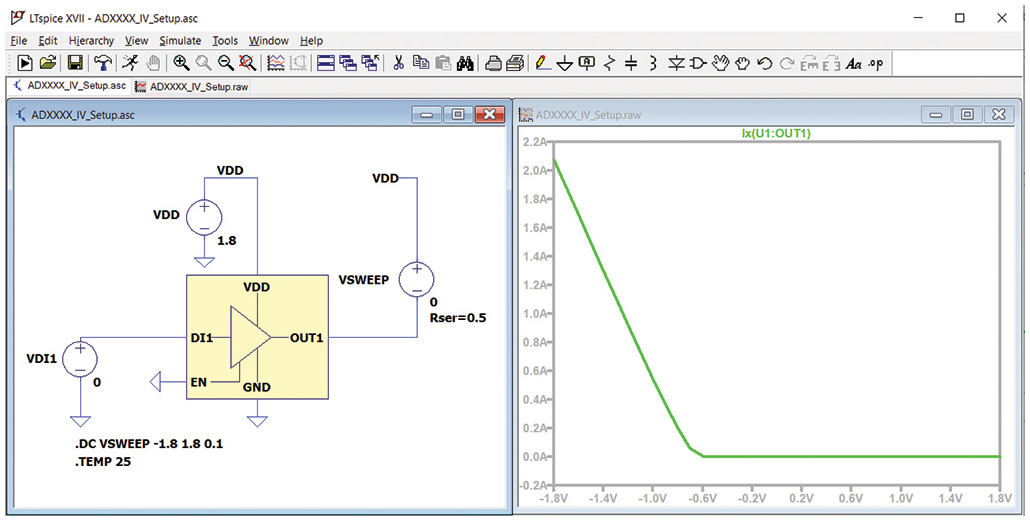

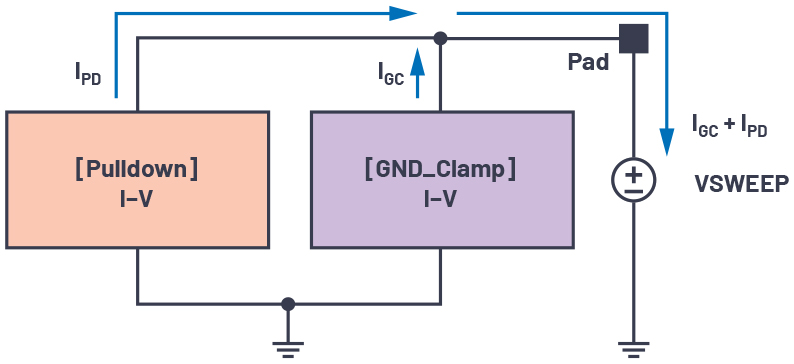

在LTspice中,I-V數據可以使用.DC SPICE命令/指令進行測量。DOUT1的接地箝位用圖4所示設置進行測量。在該設置中,使用適當的電源電壓將該器件配置為高阻態模式(請參見表5)。這可以確保將ESD器件與核心電路隔離。VSWEEP是以GND為基準的掃描電壓。使VSWEEP基準電壓接地,確保只顯示GND箝位ESD器件的特征。

根據IBIS規格,應掃描電壓軌以外(最好從-VDD到2 × VDD)的I-V數據,本例中是從–1.8 V到+3.6 V。通過直接執行此操作,掃描VDD以外的電壓將會開啟電源箝位ESD器件。為了避免這種情況,首先在–1.8 V至+1.8 V范圍內掃描VSWEEP,并使用外推方法添加3.6 V數據點。此方法適用于所有I-V數據集。

另外,請注意所有I-V數據集最多只接受100個數據點。如果數據點超過這個數目,在ibischk解析器測試中會提示錯誤。設置.DC命令的增量,使得到的數據點數量小于或等于99。這是為了容納用于2 × VDD外推的一個額外數據點。

進行直流掃描時,仿真中可能出現非常大的反向電流。要解決這個問題,將起始掃描從近似二極管勢壘電位(-0.7 V)設置為VDD (+1.8 V)。然后將數據外推至符合–VDD至2 × VDD I-V數據。另一種方法是將一個小電阻Rser與VSWEEP串聯,以限制極端電流。

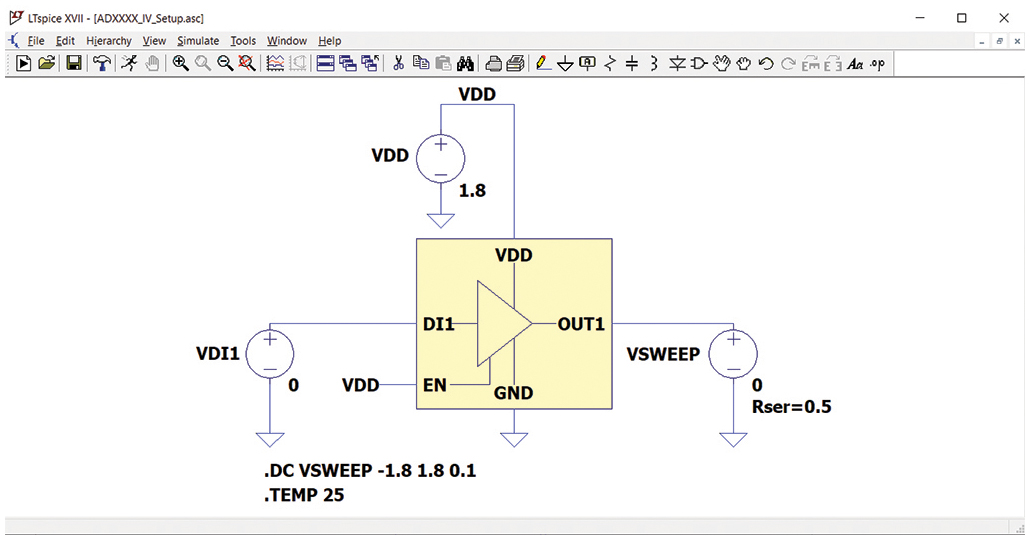

圖4 ADxxxx DOUT1接地箝位設置

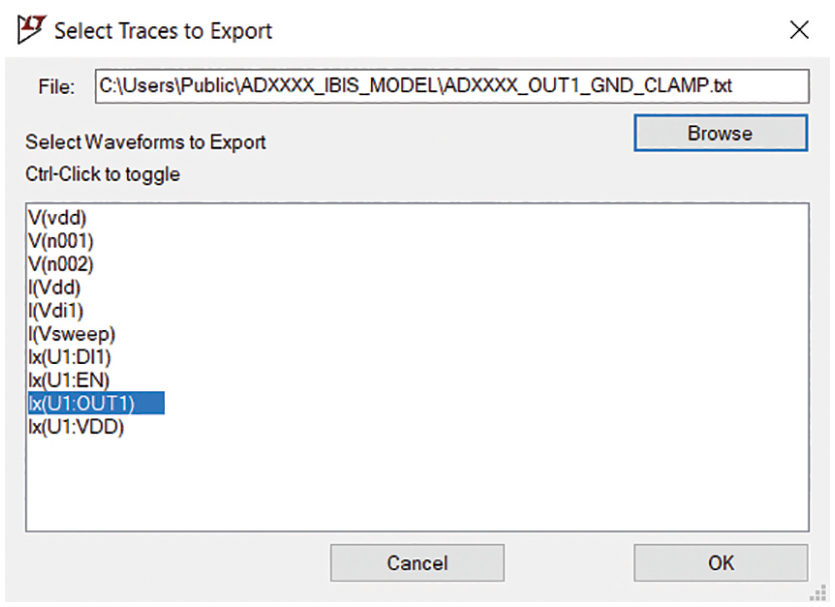

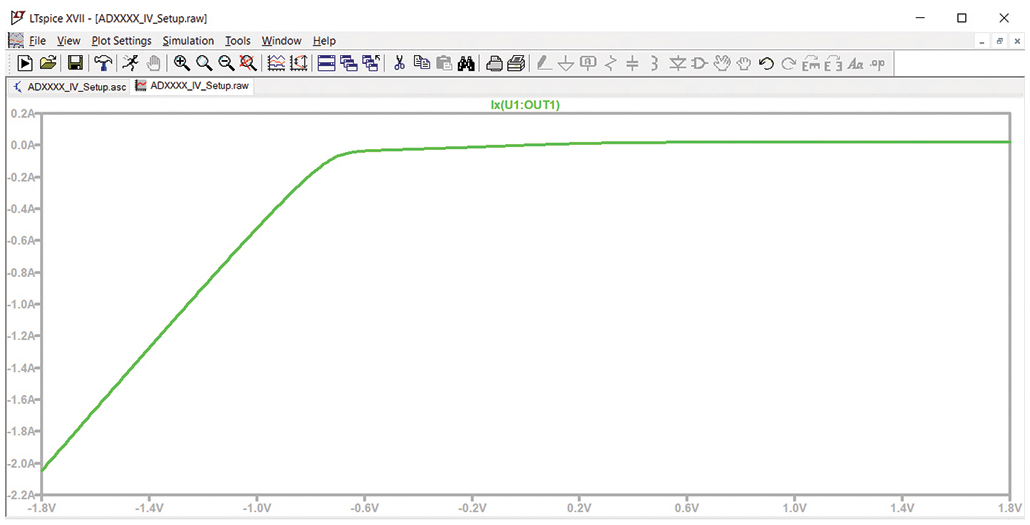

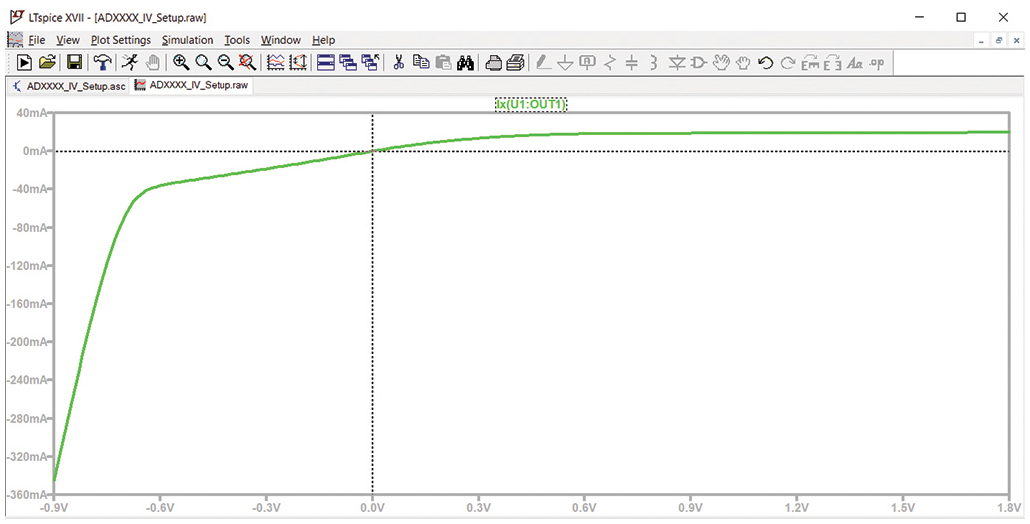

單擊運行按鈕,LTspice開始運行仿真。由于正在評估DOUT1,所以目標節點為Ix(U1:DOUT1)。雖然從技術角度來看I(VSWEEP)也是正確的,但IBIS模型需要Ix(U1:DOUT1)上的電流極性。這是為了最大限度減少I(VSWEEP)數據的進一步格式化,使其適合模型。結果應該如圖5所示。仿真完成后,先單擊結果窗口保存數據,然后單擊文件 -> 將數據導出為文本。導航至要保存的目錄,單擊受測節點,然后單擊OK(如圖6所示)。

圖5 接地箝位仿真結果

圖6 將仿真數據導出為文本

[Power_Clamp]數據提取與接地箝位設置類似,因此掃描電壓VSWEEP以VDD為基準。設置和結果如圖7所示。

圖7 ADxxxx OUT1電源箝位設置和結果

[下拉]和[上拉]

圖8 I-V關鍵字結構的概念圖

圖8顯示了I-V關鍵字結構的概念圖。[下拉]和[上拉]表示緩沖器中上拉和下拉元素的行為。如果以圖表形式表示,它們看起來就像MOSFET的I-V特征曲線。在提取[下拉]和[上拉]數據時,了解如何通過器件的真值表操控從輸出引腳輸出的信號非常重要。提取[下拉]和[上拉]數據的設置與[GND_Clamp]和[Power_Clamp]類似,即DOUT1引腳使能,且不處于高阻模式。

要提取[下拉]數據,DOUT1引腳應設置為邏輯0輸出或0 V。所以,必須設置適當的電源電壓,如圖9所示。對EN引腳施加1.8 V的等效邏輯高壓,以使能DOUT1引腳,對DIN1引腳施加邏輯0或0 V,將DOUT1引腳設置為邏輯0輸出。可以通過真值表(表5)進行確認。結果如圖10所示。

圖9 ADxxxx OUT1下拉設置

圖10 ADxxxx OUT1下拉圖

放大[下拉]數據,它類似于MOSFET的I-V特征曲線,如圖11所示。

圖11 ADxxxx DOUT1下拉圖(縮放視圖)

在保存下拉數據時,請注意它構成了[GND_Clamp]和[下拉]的總電流。圖12可以更好地說明這一點。要移除[GND_Clamp]組件,只需從[下拉]保存數據中逐點減去它。為了簡化這一操作,[GND_Clamp]和[下拉]直流分析的電壓增量、開始電壓和結束電壓必須相同。

圖12 來自下拉保存數據的實際電流

獲取上拉數據的設置如圖13所示。提供適當的電源電壓,以將DOUT1設置為邏輯1 (1.8 V)。這將確保上拉元件激活/開啟。然后,VSWEEP也在–1.8 V至+1.8 V范圍內掃描,并且以VDD為基準。以這種方式連接VSWEEP,可以防止用戶格式化數據以符合IBIS規范。

圖13 ADxxxx DOUT1上拉設置和結果

與[下拉]一樣,保存的[上拉]數據是從[Power_ Clamp]和[上拉]總電流得出的結果。因此,用戶需要從保存的[上拉]數據中逐點減去數據,以去除[Power_Clamp]組件,如果它們的直流掃描參數相同,這很容易完成。提醒大家,對所有的I-V數據測量使用相同的直流掃描參數。

圖14 來自保存的[上拉]數據的實際電流

[C_comp]

[C_comp]關鍵字代表緩沖器的電容,其最小、典型和最大拐角的值各不相同。它是晶體管和裸片的電容,與封裝電容不同。可以采用兩種方式提取[C_comp]。當引腳由交流電壓供電時,可以使用方程1中的公式來得出近似值,也可以使用方程2中的公式進行計算。

![]()

其中:

■ ImIac:被測電流的虛值

■ F:交流電源的頻率

■ VAC:交流電源的幅度

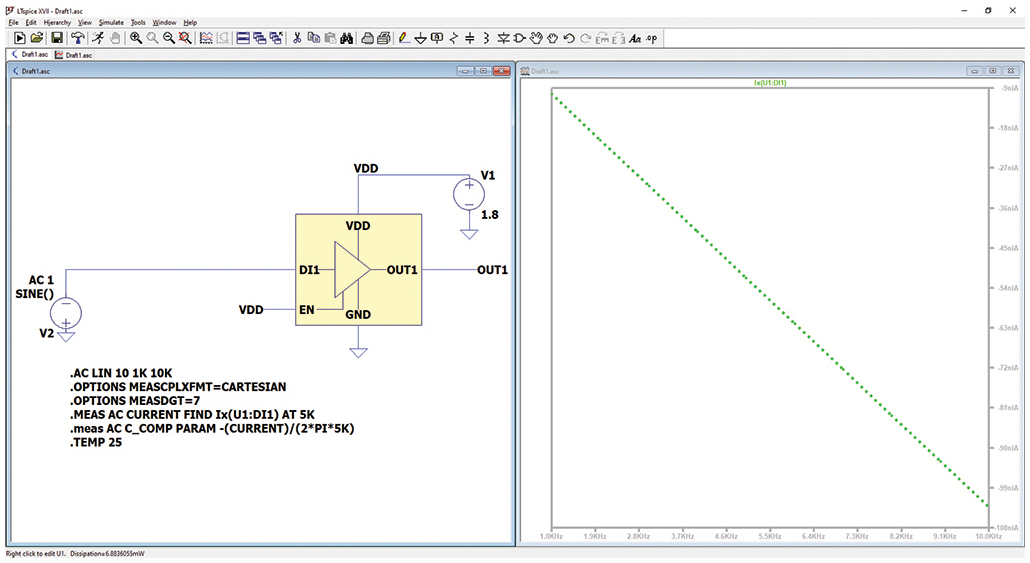

使用LTspice進行C_Comp提取

如圖15所示,可以通過提供交流電壓和頻率掃描來提取緩沖器電容。由于提供的是交流電壓,所以要測量電流的實部和虛部部分。當用交流電壓供電時,必須反轉電流的極性,以測量緩沖器的輸入電流值。測量輸出緩沖器電容時,對于圖15所示的圖,唯一要做的更改就是必須將交流電源連接至輸出引腳。

圖15 ADxxxx C_comp提取設置

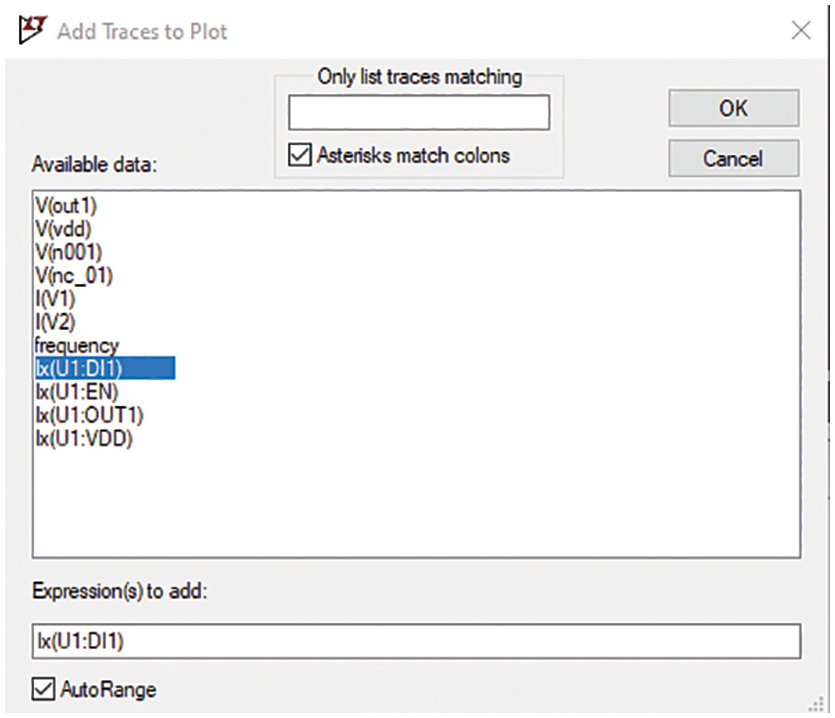

交流電壓的幅值可以是任意值,但通常設置為1 V。它將按照SPICE指令進行頻率掃描。使用.AC命令繪制波形時,默認設置為以波特模式顯示,單位為dB。必須將其設置為笛卡爾模式才能查看電流值,這樣可以直接使用緩沖器電容公式進行處理。要查看緩沖器電容波形,用戶必須先右鍵單擊波形窗口,然后單擊添加走線,再選擇被測量的引腳。波形圖窗口將顯示兩條線。

實線表示被測電流的實部,虛線表示被測電流的虛部。

圖16 向圖中添加走線對話框

若要將圖形設置從波特改為笛卡爾,右鍵單擊波形窗口左側的y軸,以打開左縱軸—幅度對話框。然后將圖示方式從波特改為笛卡爾。

圖17 將圖設置從波特改成笛卡爾

![[Android開發視頻教學]調試程序(17)](http://editerupload.eepw.com.cn/201010/683c167fad51533886b36639ff2dafb2.jpg)

![[Android開發視頻教學]Handler的使用(二)(15)](http://editerupload.eepw.com.cn/201010/060036606db1d754da56db282c235876.jpg)

![[Android開發視頻教學]Handler的使用(一)(14)](http://editerupload.eepw.com.cn/201010/eb9c23b6c856aeea242e44a15bb33adf.jpg)

![[Android開發視頻教學]SQLite使用方法(16)](http://editerupload.eepw.com.cn/201010/fea269731ea0ed920e4ec7e9e0fc592e.jpg)

![[Android開發視頻教學]文件下載(18)](http://editerupload.eepw.com.cn/201010/1cb9881533ef9443d97dc579762a9f8f.jpg)

評論