中科院EDA中心三維及納米集成電路設計自動化技術研究成果

研究方向一:三維納米級電路可制造性設計方法及EDA技術

本文引用地址:http://www.j9360.com/article/202204/433160.htm進入納米工藝節點,電路的物理結構對工藝容差和設計提出了新的挑戰,可制造性和成品率成為集成電路高端芯片能否實現批量生產并盈利的最關鍵因素之一,可制造性設計EDA技術搭建了溝通電路設計與工藝制造的橋梁,可系統提升納米芯片的良率和性能。

實驗室針對集成電路先進工藝制造和設計中存在的基礎性、前瞻性核心問題,開展三維納米級電路可制造性設計方法及EDA基礎理論和關鍵技術研究,構建納米加工與設計協同優化的具有自主知識產權的DFM軟件平臺,形成實現工藝熱點檢測和寄生參數提取的整套解決方案,從而實現新一代集成電路設計關鍵技術與EDA工具的創新和突破。研究內容包括可制造性設計、三維納米芯片CMP建模理論和方法、圖形效應建模、冗余金屬智能填充、EDA并行計算、全芯片熱點檢測和優化等關鍵技術。

研究成果:

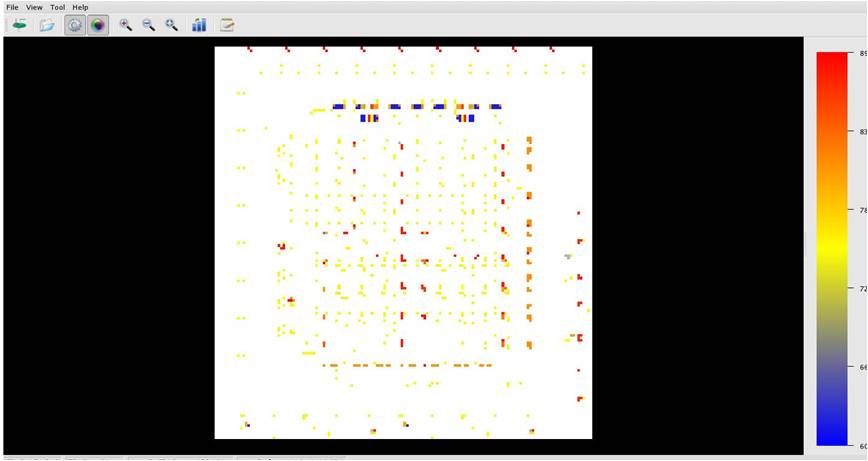

通過開展三維納米級電路可制造性設計方法及EDA技術研究,創新性地建立了納米尺度芯片多物理場CMP工藝仿真模型和設計優化技術,構建了納米加工與設計協同的ArtDFM參考流程和軟件平臺,滿足大型納米芯片DFM技術需求。Art系列DFM軟件包括業界首款32/28nm HKMG CMP模擬工具和納米節點銅互連CMP仿真工具,具有主流版圖格式(GDSII、OASIS等)快速處理、版圖參數提取、冗余金屬智能填充、CMP工藝仿真、熱點輸出與反標以及第三方應用集成等功能。Art系列DFM軟件支持多核架構自適應并行計算,其運算速度和精度達到業界先進水平,各項指標達到工業界使用標準,已應用于國內知名設計和制造企業,為其提供全芯片熱點檢測和表面平坦性預測服務。

納米芯片DFM平臺

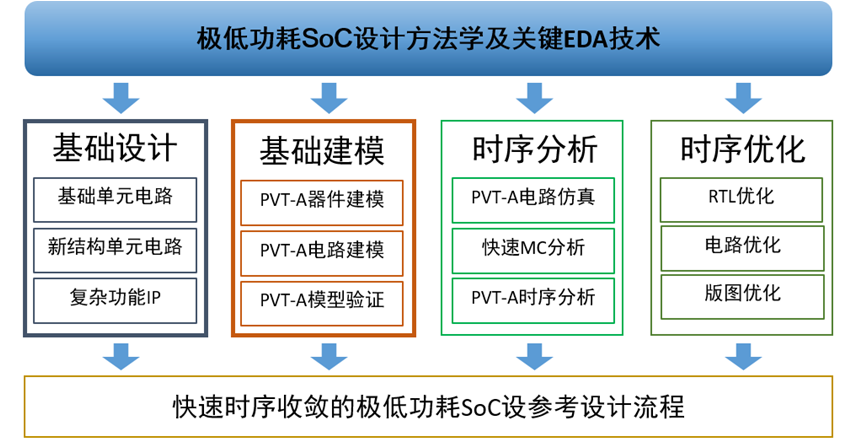

平坦性仿真熱點檢測 研究方向二:高頻電磁場分析及仿真技術 該研究方向重點在高頻電磁場算法基礎研究、算法應用研究以及算法工具開發這三個層面開展研究工作,研究內容主要包括電磁及多物理耦合場的多層級建模仿真與優化技術,面向電磁及多物理分析的模型降階算法,無線通信信道建模技術以及面向物聯網的定位等應用。 研究成果: 在基于廣義本征分解的集成電路互連系統高效物理建模研究中,實現了求解高頻電磁場參數問題的廣義本征分解方法(PGD)以及棱單元的靜磁場計算中的PGD方法。與常用的模型降階方法正交本征分解方法 (POD)相比,隨著參數空間維數的增加,PGD的優勢逐漸凸顯。以模擬低通濾波器的數值試驗為例,在頻率和電容率的參數空間中,PGD計算可以比迭代掃頻計算節省90%以上的運算時間。 在室內毫米波無線通信定位混合系統中,為提高定位精度,利用watersheds、主成分分析以及人工神經網絡等方法,實現了對LOS和NLOS波束的識別。此項毫米波波束判別工作屬于首創。 在并行計算研究中,結合任務級并行與數據級并行,提高了版圖參數提取效率。實現了網格剖分優化技術,對GDSII版圖解析得到的幾何結構文件,采用Tetgen/Gmsh等開源包進行網格剖分,并借助自動網格加密實現對版圖參數提取的加速。 在模型降階及其在電磁數值分析的應用研究中,課題組利用C++編程實現了POD/PGD兩種模型降階串行工具,利用模型降階中的“模式”作為相對獨立的任務級并行,采用數據級并行算法,對一維和二維參數空間中的全波問題進行了參數研究。算例表明,POD與PGD均可得到相當精確的解,從而獲得結構的共振模態。 研究方向三:亞閾值低功耗設計方法及EDA技術 該研究方向旨在研究亞閾值極低功耗SoC設計方法學,研發設計面向移動物聯網、體域網等應用的亞閾值SoC極低功耗IP,并為對應SoC設計研究關鍵EDA技術。主要研究PVT-A偏差下高魯棒性亞閾值極低功耗SoC設計方法學及關鍵優化技術,主要內容包括器件、版圖、電路和架構之間跨層協同設計和優化,亞閾值極低功耗基礎單元、新型結構電路、復雜功能IP的設計,PVT-A變化敏感情形的器件建模、電路建模和模型驗證技術,亞閾值極低功耗SoC快速統計分析與優化技術,高魯棒性可重構異步亞閾值極低功耗SoC設計技術,并研發相關核心算法及EDA軟件原型。 亞閾值極低功耗SoC設計方法學及關鍵EDA技術框架 研究成果: EDA中心在亞閾值極低功耗SoC設計方法學及關鍵EDA技術領域開展了多年的研發工作,研究設計了亞閾值溫度傳感器、32位亞閾值SAPTL超前進位加法器、16位亞閾值B-SAPTL加法器、16x16亞閾值ASYN-B-SAPTL異步乘法器、動態可重構亞閾值邏輯等多款極低功耗電路IP,技術指標均優于文獻報道的同類功能電路,研發了單元電路版圖微調軟件、電路結構自動評測工具、電路器件參數優化工具、快速High-σ蒙特卡洛分析工具、器件建模工具、PVT敏感的單元電路特征化工具等。 研究方向四:支持千萬門級的高速并行SPICE后仿真技術 現有SPICE仿真工具雖然算法各異,但總體都是基于CPU的通用軟件算法,在求解先進工藝的超大量器件模型,超大規模電路矩陣,特別是RC矩陣時,由于CPU架構和運算單元的制約,整體運算效率已無法適應先進工藝設計的需求。 該研究方向從系統架構層面構建新的仿真驗證方案,進行基于GPU/CPU異構平臺高精度并行晶體管級后仿真工具的開發。通過對仿真算法的分解,配合對應的專用硬件架構以適應仿真算法的特點,通過軟硬件協同,最終達到對現有仿真工具1個數量級以上的仿真加速效果,從而支撐更大規模、更復雜設計的仿真驗證,完成原仿真工具無法完成的仿真驗證任務。 研究成果: 截至2020年底,研發的仿真工具性能已達到主流工具的4~6倍。

評論