中科院:物聯網新型體系結構

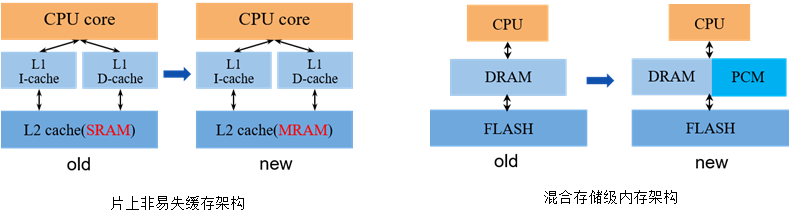

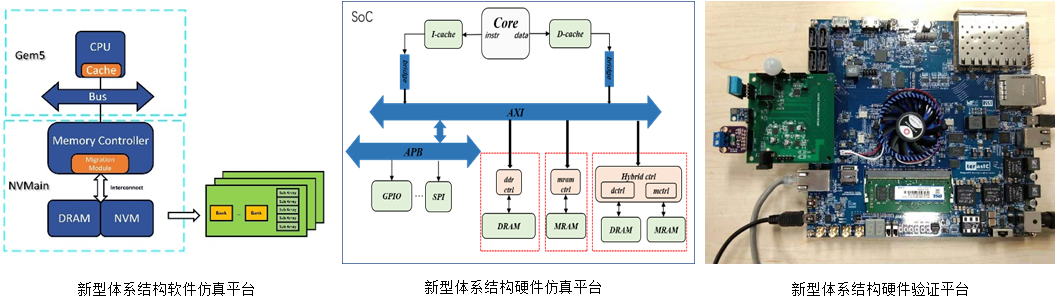

基于新型非易失存儲的高能效終端架構技術:為解決資源受限物聯網終端的“存儲墻”問題,利用MRAM、PCM等新型存儲器,構建異構非揮發存儲架構。通過研究軟、硬件協同的異構存儲架構管理技術,達到降低內存功耗、減小I/O延時的目的。此項工作得到國家重點研發計劃、北京市科技計劃、中科院先導專項的支持。

本文引用地址:http://www.j9360.com/article/202204/433142.htm

AI計算加速技術:GPU、ASIC、FPGA等AI加速器是實現高能效AI計算的重要手段,然而受限于移動計算環境對芯片面積、功耗等的要求,AI加速芯片片上緩存容量有限,當計算深度模型時需要頻繁訪問片外存儲,因此“內存墻”問題依然凸顯。該研究內容旨在研究面向AI加速芯片的近數據計算架構,解決AI加速芯片中的存儲墻問題。主要研究內容包括面向AI加速芯片的近數據計算架構、基于新型存儲技術的片上高帶寬存儲系統,以及支持片上資源可重構的指令集與系統軟件。

評論