一種基于LDMOS器件結構優化提升功率放大器功率附加效率 的方法

吳錦帆(電子科技大學電子科學與工程學院??四川??成都??610054)

本文引用地址:http://www.j9360.com/article/202005/413605.htm摘?要:本文介紹了一種通過改進LDMOS的器件結構,提升以LDMOS搭建的功率放大器的功率附加效率大信號指標的方法。在器件仿真環境中,通過對LDMOS的漂移區進行結構優化,提升器件的小信號增益,然后利用器件等效建模技術,在電路仿真環境中,搭建出功率放大器進行大信號仿真,在相同的工作條件下功率附加效率提升了約5%左右。

0 引言

橫向雙擴散金屬氧化物半導體場效應管(RFLDMOS)作為一種應用在射頻放大器電路中的晶體管,最能體現出其性能的器件參數有輸出功率,漏極效率,功率增益等,提高器件的這些參數一直以來是RFLDMOS研究者們的努力的方向,而隨著射頻終端數量的增加,用戶對數據傳輸速率和容量的要求越來越高,射頻電路一直有著向高頻率高效率的趨勢發展 [1] 。功率附加效率作為射頻功率放大器的大信號指標之一,射頻功率放大器具備較高的功率附加效率意味著系統需要更小的直流功率供給就可以產生較大的輸出功率用于RF信號源的放大。同時也意味著器件在工作的過程中,由于晶體管自身的熱阻所產生的熱消耗將降低,器件的工作壽命也會相應得延長 [2] 。因此,功率附加效率的提升不僅意味著輸出功率的提升,同時也延長了器件的工作壽命。

針對上述問題,本文提出了一種基于LDMOS器件結構優化的方案,通過大信號與小信號等效模型進行建模的方式,提升以LDMOS作為功率晶體管的射頻功率放大器的功率附加效率。文章第2節主要描述該方法的工作原理及流程;第3節給出LDMOS器件結構優化方案;第4節給出等效模型建模方法;第5節給出功率放大器仿真結果。

1 功率附加效率提升方法原理

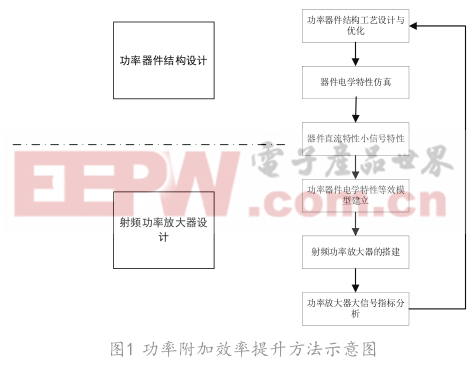

如圖1所示,功率附加效率指標提升的方法主要分為兩個階段,功率器件結構設計階段與射頻功率放大器設計階段。在功率器件設計階段,利用半導體工藝模擬以及器件模擬工具(TCAD)仿真軟件進行器件仿真模型的建立,其中在完成實際工藝與仿真軟件參數的校準之后,實現功率器件結構的建模以及器件電學特性的仿真,獲得器件的大信號直流特性以及交流小信號特性。以器件的直流特性與交流特性作為連接電路仿真與器件仿真的橋梁,通過搭建電學特性等效模型,達到在射頻電路仿真環境中功率器件的等效還原的目的。在射頻功率放大器設計階段,利用電路仿真軟件,完成射頻功率放大器的搭建以及大信號指標的仿真,通過調整電學特性等效模型實現功率放大器大信號指標的優化,并根據電學特性的優化目標指導器件結構設計的優化,最終實現射頻功率放大器的功率附加效率的提升。

2 功率器件結構設計與優化

LDMOS基本結構如圖2所示,主要由P_sinker,源極(Source),柵極(Gate),橫向漂移區(LDD),漏極(Drain)幾個部分組成,其中通過高能離子注入形成P_sinker將器件的源極與襯底進行了連接,通過背面減薄和背金工藝形成了背面源電極,減少了電極的數量以及襯底與源極的鍵合連線,降低了寄生的電感與電容,LDD的存在利用RESURF表面電場的原理提升了LDMOS的擊穿電壓,保證了器件能夠在高壓RF的用途。而本文中通過將LDD區進行水平分層,分為LDD1,LDD2,其中LDD1為相對低濃度的n摻雜,LDD2維持與原來結構相同的n摻雜濃度,保證了擊穿電壓與器件導通電阻的不變。低摻雜LDD1的存在降低了右側溝道與LDD區交界的pn結擴散電容 C gd 改善了器件的小信號特性。在相同的偏置電流I ds =0.18 A,中心頻率為f = 450 MHz,使用右側的新結構相比原先結構的S21提升了約12%。

3 功率器件等效模型的搭建

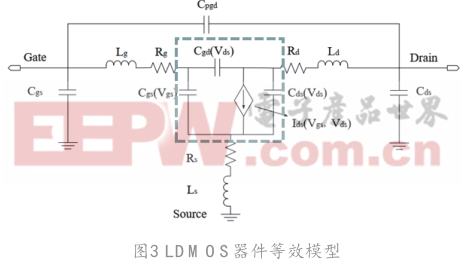

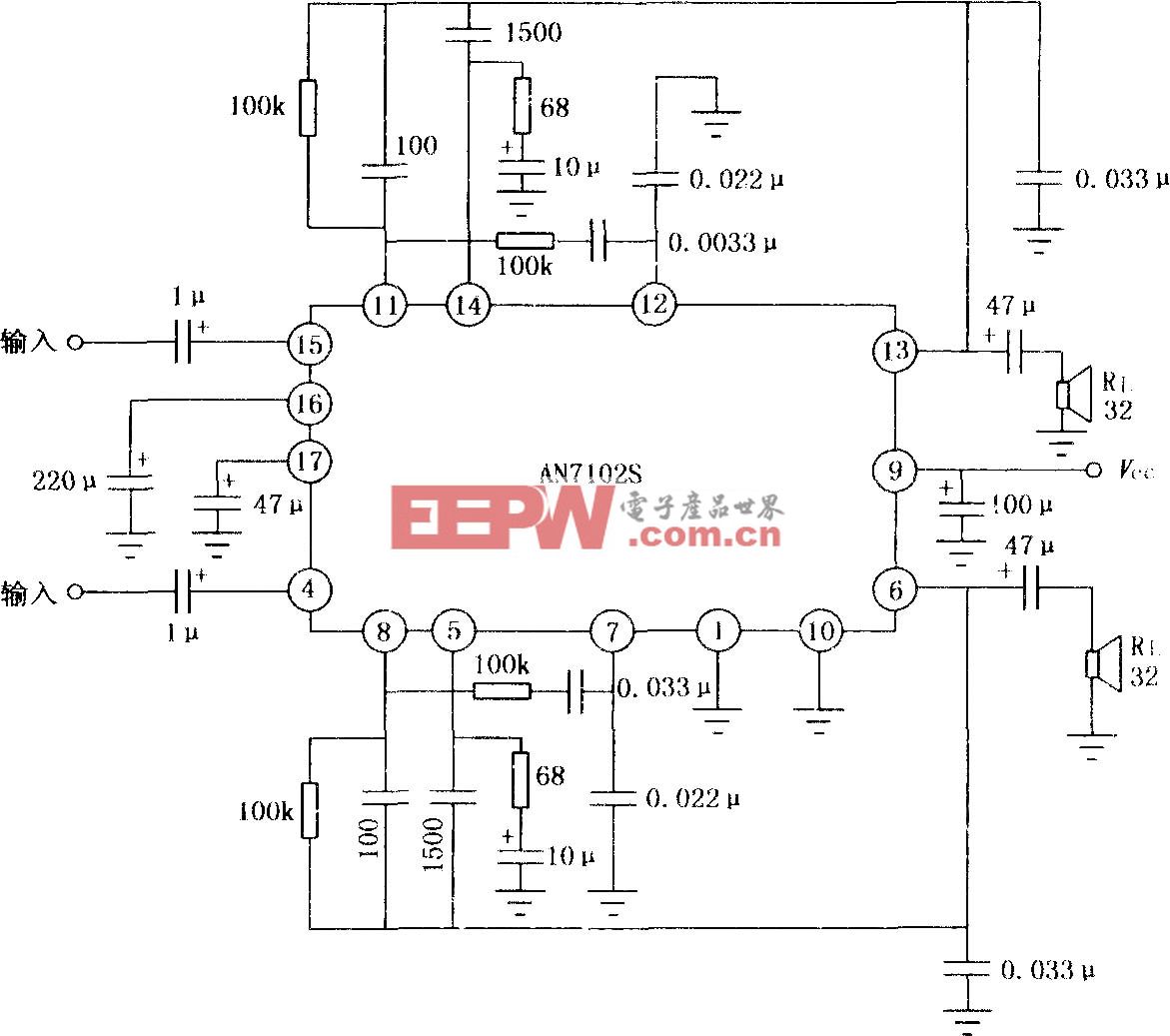

電學特性等效模型如圖3所示,其中,小信號等效模型和大信號等效模型結構是一致的,兩者不同的地方在于,大信號等效模型的本征部分是時變的,即虛線框內的本征部分受到端口電壓的改變而改變,而小信號的等效模型在固定的偏置點和工作頻率下是恒定的。

該模型主要分為兩部分,其中虛線框內的部分為器件的本征部分,受器件的偏置和工作頻率的改變而改變,器件的大信號直流模型表現為一個壓控流源,而小信號模型表現為一個恒流源。虛線框外的為器件的寄生參數部分,主要為器件進行封裝時產生的電阻和電感以及PAD對地耦合產生的寄生電容,寄生參數部分對偏置和工作頻率不敏感 [3] 。

器件的大信號非線性直流特性通常采用非線性經驗模型來建模,非線性經驗模型是以實驗測試數據為基礎,通過擬合I-V特性曲線的數據來確定經驗模型中公式所需要的參數。將RFLDMOS典型的轉移特性曲線,分為四個區:截止區、二次區、線性區和電流壓縮區 [4] 。

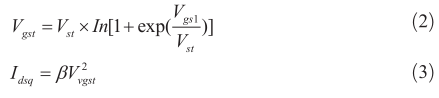

在截止區,RFLDMOS器件的漏極電流隨柵極電壓呈指數變化,此時的漏極電流有如下形式:

當柵極電壓逐漸增大,LDMOS器件進入二次區,此時的器件跨導隨柵極電壓線性增加,漏極電流與柵極電壓的平方呈正比。從LDMOS器件的截至區過渡到二次區漏極電流可統一表示為

V st 表征器件開啟的陡峭程度,V t 為LDMOS的閾值電壓, V st 和β的數值根據LDMOS的測試數據進行擬合得到 [5] 。

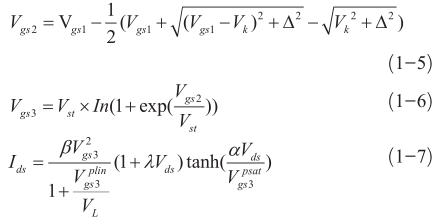

RFLDMOS的線性區電流表達式為

在LDMOS電流壓縮區,由于跨導的降低,漏極電流不再隨柵極電壓增加而線性增加,飽和區電流公式如下所示:

結合公式(1)~(7),在MATLAB工具中對器件的測試曲線進行了擬合,擬合結果如圖4所示,模型可以較好地擬合器件的直流特性。

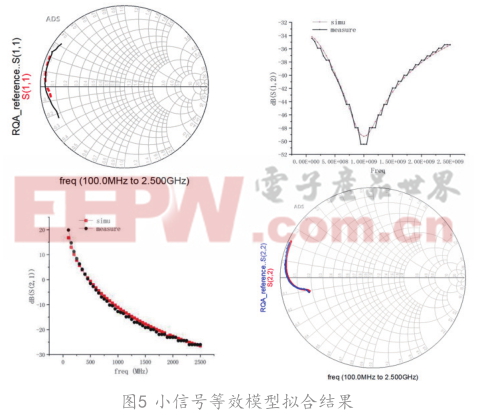

在ADS仿真軟件中搭建小信號等效模型,擬合結果如圖5所示,小信號模型計算結果與測試數據結果擬合程度良好,該小信號模型基本可以表征實際器件的端口特性。

4 功率放大器仿真結果與分析

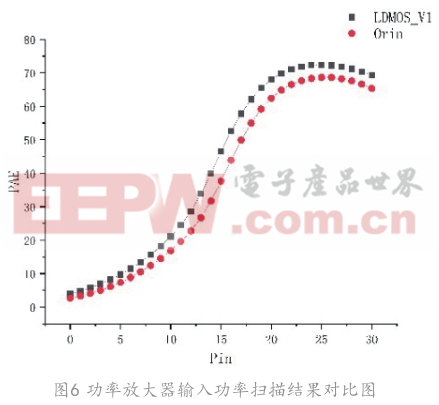

在ADS電路仿真中,將搭建好的LDMOS器件模型進行輸入輸出匹配,完成功率放大器的搭建,并進行大信號仿真。結果如圖6所示,通過器件結構的優化,當小信號模型中的 C gd 降低12%,在相同的匹配電路以及工作偏置條件下,可以實現Pout與PAE的整體提升其中,改進后的PAE相比于原來提升5%左右,Pout提升約1 dBm左右。

5 結論

隨著射頻終端數量的增加,射頻電路一直有著向高頻率高效率的趨勢發展。在射頻功率放大器電路中,功率晶體管作為放大器的核心元件,其端口阻抗及寄生參數不僅影響著放大電路的端口阻抗,電學參數特性的改變不僅會對匹配情況造成改變,也會對功率附件效率、功率增益等大信號特性造成影響。本文介紹了一種通過改進LDMOS器件結構,提升以LDMOS為功率晶體管的功率放大器的功率附加效率的方法,通過對LDMOS器件結構進行優化實現了放大器功率附加效率的提升。

參考文獻:

[1] Vestling L . Design and Modeling of High-FrequencyLDMOS Transistors[D]. Uppsala:Uppsala University,2002.

[2] 馮曦. 射頻功率LDMOS器件設計[D]. 北京:清華大學, 2006.

[3] Raab F H, Asbeck P, Cripp S, et al. Power amplifiersand transmitters for RF and microwave [J]. IEEE T MicrowTheory, 2002, 50 (3): 814-826.

[4] Raffo A , Scappaviva F , Vannini G . A New Approachto Microwave Power Amplifier Design Based on theExperimental Characterization of the Intrinsic Electron-Device Load Line[J]. IEEE Transactions on MicrowaveTheory and Techniques, 2009, 57(7):1743-1752.

[5] Bosi G , Raffo A , Trevisan F , et al. Nonlinear-embedding design methodology oriented to LDMOS poweramplifiers[J]. IEEE Transactions on Power Electronics,2017:1-1.

(注:本文來源于科技期刊《電子產品世界》2020年第06期第xx頁,歡迎您寫論文時引用,并注明出處。)

評論