FPGA及IP在邊緣智能中的機會

Bob?Siller?(Achronix公司?產品營銷總監)

本文引用地址:http://www.j9360.com/article/202003/411456.htm多種AI應用需要不斷加速,包括:視頻、圖像和語音識別;數據壓縮;加密與解密;自然語言處理;工業物聯網;汽車駕駛員輔助系統;低延遲邊緣推理;智能網卡和服務器加速。

在這些應用中,我們看到對性能的需求日益增長,從而產生了許多全新的、創新的系統架構。業界對硬件加速平臺的需求不斷增加,以釋放CPU周期,從而提供更好的系統總體擁有成本。微軟、谷歌、亞馬遜、蘋果和特斯拉等終端設備制造商已開始為其特定的AI應用工作負載開發自己的ASIC芯片,以推動不斷增強的產品差異化和競爭優勢。這促使半導體產品作為AI技術的關鍵驅動力而得到復興,特別是對于Achronix而言,越來越多的客戶正在尋找FPGA,以幫助盡快提供創新的AI功能。

2 解決開發AI的挑戰

開發人員在開發AI方案時,面臨2個關鍵挑戰:

①硬件平臺如何跟上全新的AI軟件算法和不斷變化的工作負載的創新速度?

②硬件制造商如何利用一個硬件平臺來平衡計算、存儲和I/O性能,以獲得最大的使用性能?

Achronix的Speedster7t FPGA器件和SpeedcoreeFPGA IP解決方案可以通過多種方式幫助應對這些挑戰。

FPGA從本質上是可重編程的,但直到最近幾年,它們才被主要用于網絡加速和預處理任務。隨著FPGA已經變得功能越來越強大,它們現在也作為CPU的協處理器和硬件加速器被用于核心應用功能中。

FPGA協處理器支持系統架構師去將性能關鍵功能轉移到專用硬件器件上。通過卸載這些功能,設計人員可以看到整體應用性能的顯著提高。隨之而來的其他好處是,當AI工作負載或算法最終發生改變時,設計人員只需在現場對FPGA進行重新編程,即可更新算法并提供更高的性能。相比傳統的ASIC,可以縮短產品上市時間、延長產品生命周期,從而最大限度地利用硬件投資。eFPGA IP為那些努力設計出完美AI架構的ASIC設計人員提供了令人信服的優勢。現實的情況是沒有完美的架構,最佳的架構取決于所分配到的工作負載。

eFPGA IP被嵌入在ASIC中,因而盡管ASIC架構是固定的,但是將關鍵算法卸載到器件的eFPGA部分,就可以在硬件平臺的整個生命周期中進行持續的更新并提高性能。這可以延長生命周期,并為類似于使用獨立FPGA的新功能提供更快的上市時間,而無需其他分立器件來支持。與連接到分立FPGA解決方案的ASIC相比,集成在同一個芯片上,使設計人員可以節省高達90%的成本,降低75%的功耗,并增加10倍的帶寬。

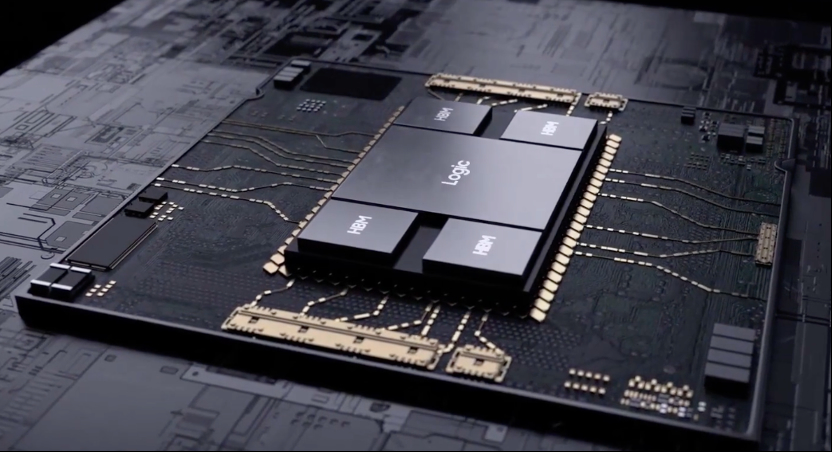

Achronix是唯一一家在批量應用中可同時提供經過驗證的FPGA和eFPGA IP解決方案的公司。Speedster7tFPGA具有平衡的架構,結合了諸如112 Gbps SerDes、PCIe Gen5和400 Gbps以太網接口等非常高速的I/O接口。

在將數據傳輸到Speedster7t之后,一種特有的片上網絡(NoC)架構支持這些數據以高達2 GHz的雙向速度在FPGA邏輯陣列中進行傳輸。與傳統的FPGA相比,NoC可以實現在FPGA架構中更快的數據傳輸速度,從而進一步減少路由擁塞并提高系統性能。新的機器學習處理器(MLP)單元模塊也被添加到其中,也提高了在AI應用中被經常使用的數學乘法和累加函數的性能。Speedster7t FPGA器件中的MLP是可配置的,以支持諸如整數、浮點和塊浮點等多種不同的數字格式,從而可以在較低的數據規模要求下實現更高的性能。

最后,擁有足夠的內存帶寬是幫助AI應用實現高性能的另一個關鍵要素。Speedster7t FPGA配備8個GDDR6內存接口,總帶寬可達4 Tbps。這有助于支持在人AI應用中存儲系數和其他數據密集型操作及工作負載。

把所有這些元素相結合,就為AI工作負載提供了令人信服的解決方案。Achronix提供了獨特、靈活的FPGA或eFPGA架構,以及帶寬優化的I/O、計算和存儲性能,這是未來AI應用的理想選擇。

評論