應用于微顯示芯片的MIPI DSI驅動接口設計

尹? 遠,黃嵩人 (湘潭大學?物理與光電工程學院,湖南?湘潭?411105)

摘? 要:隨著信息技術發展,高分辨率的微顯示器已廣泛應用于移動電子設備中,傳統顯示接口難以滿足其高 速率傳輸、低功耗、抗干擾、兼容性高等要求,因此本文針對以上問題,提出了一種基于MIPI DSI協議,并應 用于高分辨率微顯示芯片的顯示驅動接口的設計。

0 引言

微顯示芯片是一種特殊形態的顯示器,其物理尺寸 小,功耗較低,分辨率高,目前主要應用的產品形態 有:LCOS微顯示器,OLED微顯示器,LCD微顯示器 等。也可以通過光學系統產生大屏幕系統,常用于投影 系統和近眼顯示系統中[1]。其應用領域廣泛,如VR眼 鏡、AR智慧眼鏡、軍用頭盔、微型投影儀、車載抬頭 顯示等電子設備。

隨著消費級電子設備的發展,微顯示芯片應用的電 子產品越來越多,顯示的分辨率不斷增強,對顯示效果 的要求也日益提高,需要傳輸的數據量和速率也越來越 大,同時還要求設備保持高性能和低功耗,傳統的顯示 接口已滿足不了諸多要求。因此本文針對這種情況,設 計了一種適用于高分辨率微顯示芯片的MIPI DSI顯示驅 動接口[2]。

1 MIPI DSI協議介紹

MIPI DSI是MIPI(Mobile Industry Processor Interface,移動業處理器接口)聯盟為了對移動設備的外設接口標準進行統一,以提高系統兼容性、設計性能 和效率,而提出的一種顯示接口標準[3]。DSI接口是一 種高速的串行顯示接口,可實現高分辨率顯示,而且有 功耗低、抗干擾強的特點[4]。

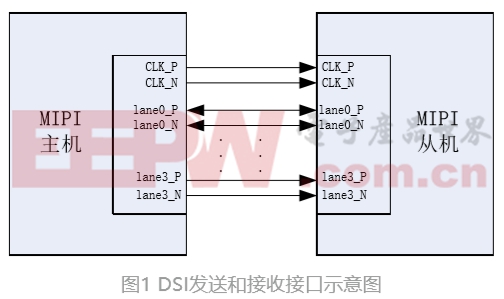

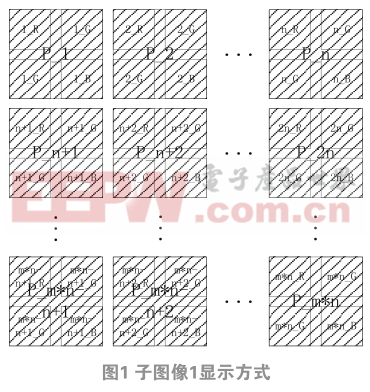

圖1所示是簡化的DSI接口示意圖[5],主機可以發送 高速像素數據和低速命令給從機,并可以從從機設備中 讀取狀態或像素信息。主機和從機之間的通信一般是配 置1對差分時鐘通道,1~4對數據通道。

MIPI DSI支持兩種基本操作模式,分別為命令模式 (Command Mode)和視頻模式(Video Mode)[3]。命令模式是指主機端向從機設備發送命令和數據,轉換為 DBI格式,對顯示設備進行讀寫操作,以此來間接控制 從機端的外圍設備的工作狀態。另外從機端會通過雙向 的數據通道0返回相關數據,主機端因此也可以讀取到 從機設備的狀態信息和緩存內容。視頻模式主要是通過 數據通道在高速傳輸模式下,由主機單向傳輸給從機以 圖像顯示或視頻數據,從機接收到進行解碼后,最終將 其轉為DPI時序格式直接傳送給顯示設備,進行實時顯 示[4]。

DSI接口支持兩種傳輸模式,分別為高速數據傳輸 模式(High-Speed Mode)和低功耗模式(Low-Power Mode)[6]。其中所有的數據通道都可以用于單向的高速 數據傳輸,如傳輸圖片和視頻數據。低功耗模式下的傳 輸只通過雙向的lane0進行,如低速數據和控制命令,速 率可達10 Mbit/s。時鐘通道傳輸高速傳輸過程中的同步 時鐘信號,采用高速DDR時鐘,速率可達到1 Gbit/s。

MIPI DSI協議中規定數據是以數據包的形式傳輸, 根據包的長度不同,分為長包和短包。短包固定4個字 節長度,由標識符DI、data0、data1、ECC校驗碼組成 [6],如圖2所示。長包是由包頭、包數據、包尾組成,如 圖3所示。包頭是由DI、指定數據包中數據個數的WC、 ECC碼組成,包尾是16 bit的校驗和,長包的總長度范 圍為6~65541字節[6]。

2 DSI接口工作原理

本文的設計目標是實現基于MIPI協議的顯示接口 的設計,支持4路通道的高速數據傳輸,包括圖片或視 頻,通道0實現Escape模式下的低功耗傳輸模式,用以傳輸低速控制命令或數據,且支持lane0雙向數據傳輸, 時鐘通道傳輸高速同步時鐘信號,支持RGB888格式的 數據輸出,具有ECC校驗、CRC校驗功能等[3]。

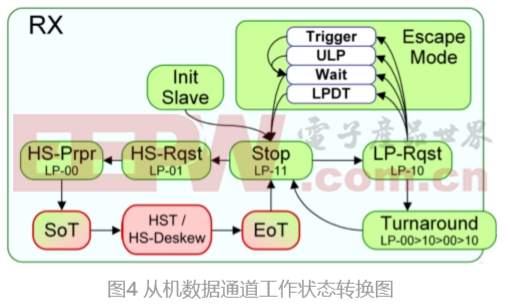

高速模式下,通道上有兩種狀態:HS-0、 HS-1[7]。在低功耗模式下,lane0上有四種狀態:LP00、LP-01、LP-10、LP-11[8]。根據總線上檢測到不 同的電平序列后,分別進入或退出相應的模式,如圖4 所示為從機通道工作的狀態轉移圖[7],可在高速模式、 Escape模式、TA(Turnaround)模式之間切換。

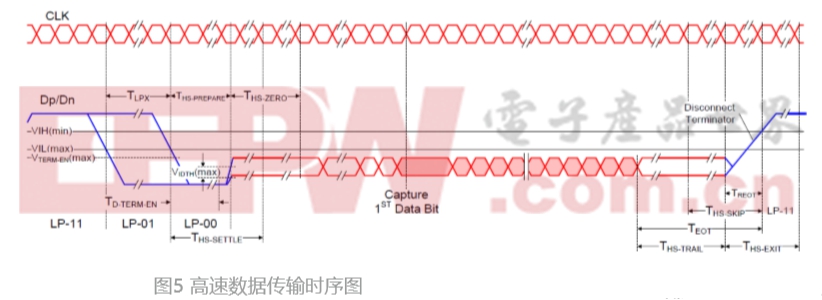

所有的數據通道都支持高速數據傳輸模式,從機接 收來自主機的高速串行數據進行編解碼。在空閑的時間 段,通道處于LP-11狀態。當從機端接收到發自主機端 的序列:LP-11→LP-01→LP-00,即高速請求序列, 之后便準備進入高速數據傳輸模式接收高速數據。如需 退出高速模式,則發送EOT→LP-11。圖5為高速傳輸 時序圖[7],定義了整個高速傳輸過程的方式和時序。當 從機端接收到高速模式下傳輸的數據后,會將數據包 中的像素數據解析出來,生成RGB格式數據、同步信 息、有效信息等,通過DPI接口輸出給顯示端進行顯示 成像。

當從機檢測到主機發送序列:LP-11→LP10→LP-00→LP-01→LP-00,進入Escape模式。之后 等待主機發送8 bit的命令,可進入其中的三種模式: ULPS超低功耗模式、LPDT低功耗數據傳輸模式、 Trigger模式。除了lane0都支持外,其他數據通道只支持 其中的超低功耗模式。其中使用較多的是低速數據傳輸 模式,lane0通過此模式可傳輸控制命令或數據。退出 Escape模式主機需發送序列:LP-10→LP-11。

進入TA模式需要發送請求序列:LP-11→LP10→LP-00→LP-10→LP-00,之后主機會釋放總線控 制權,由從機獲得總線控制權,通過lane0發送低速數據 返回給主機,數據內容一般是響應信息、錯誤報告、結 束包等,發送完畢后從機會發送TA模式的序列請求, 將總線控制權交還給主機。退出TA模式發送序列LP00→LP-10→LP-11即可。

3 MIPI DSI電路設計

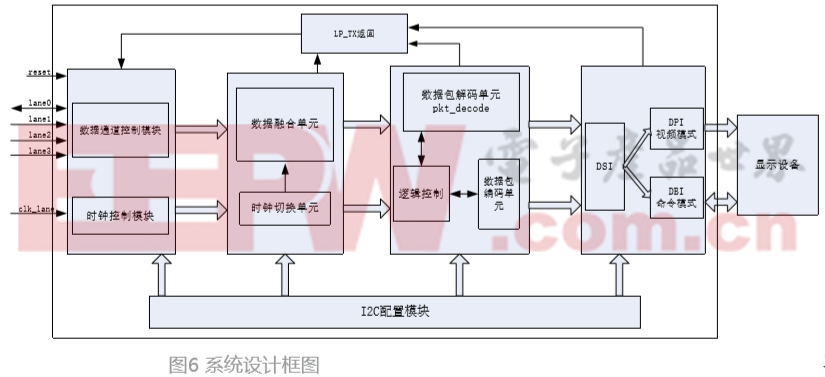

依據MIPI DSI協議的層次劃分,將DSI接口電路分 為物理傳輸層模塊、底層協議層模塊、通道管理層模 塊、應用層模塊4個主要模塊[3],系統設計方案如圖6 所示。

1)物理傳輸層:本層只要由時鐘通道控制模塊、 數據通道控制模塊組成,其中數據通道控制模塊又分 為數據通道0控制模塊和其他數據通道控制模塊。時 鐘通道控制模塊,主要實現了檢測時鐘通道LP→HS和HS→LP的模式切換。數據通道控制模塊,主要完成了4 個數據通道的高速模式和低功耗模式相互之間的切換檢 測,數據通道0的Escape模式和TA模式的檢測[3]。將接 收到的高速模式和低功耗模式下的串行輸入數據轉為并 行數據,并傳輸給通道管理層[3]。將TA模式的返回數據 進行并串轉化,再通過lane0傳輸給主機[2]。

2)通道管理層:主要分為高速數據接收模塊、低 功耗模式數據接收模 塊,以及時鐘切換模 塊。完成4個數據通道 的高速模式的SOT序 列檢測,接收物理傳 輸層發送過來的低功 耗模式命令和數據[3]。 實現數據融合功能, 將多通道的數據恢復原有字節順序,并整合起來。時鐘 切換模塊實現高速時鐘、低功耗下時鐘,以及TA模式 下的不同時鐘的切換。

3)底層協議層:主要完成高速模式和低功耗接收 模式的數據包的解碼和編碼,及ECC、CRC檢測。當接 收來自物理傳輸層的數據時,對高速和低功耗模式的數 據包進行解碼,檢測數據包的類型,根據長短包分別 進行處理,并對ECC 碼進行檢測校驗、糾 錯,以及CRC校驗。 對接收到的低速返回 數據包編碼打包,主 動生成對應的ECC校 驗碼、CRC校驗碼, 以返回主機以響應 (ACK)和錯誤報告 (Error Report)[3]。 另外需要處理來自物理層的錯誤信號和Trigger信號,以 及本層內檢測出的ECC校驗錯誤和CRC校驗錯誤[4]。

4)應用層:這部分直接與顯示端連接,將接收到 的數據和命令進行譯碼,分別可以進入視頻模式和命 令模式,最后轉換成顯示端能識別的DBI格式或DPI格式。進入視頻模式后,將接收到的高速像素數據轉為符 合顯示端兼容的DPI時序的數據,然后進行顯示。當進 入命令模式,將低功耗接收的數據包解碼,之后轉成 DBI格式數據寫到相應寄存器中。有時還需要從顯示端 讀到的DBI格式,然后將其編碼轉為DSI接口數據,最 后通過lane0發送給主機。

另外還有I2C配置模塊,用于對各模塊進行參數配 置,確保設計的成功實現,也可方便驗證和芯片調試, 提高該設計的靈活性和兼容性。

4 DSI接口仿真與測試

4.1 仿真平臺及方案

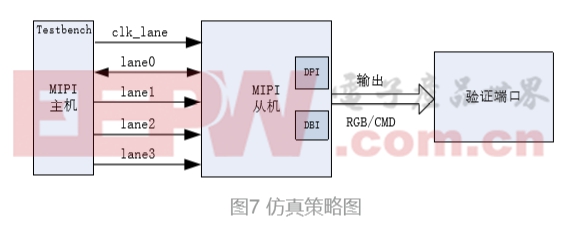

圖7所示為此接口設計的仿真策略圖,模擬MIPI主 機發送機制,通過數據通道發送高速數據,通過數據通 道0發送低功耗數據,該設計作為MIPI從機,接收數據 后進行編解碼,最終將相應的數據和命令輸出,通過觀 察驗證端口的仿真波形或數據比對,來確定設計是否完 成對應的功能要求。

4.2仿真結果及分析

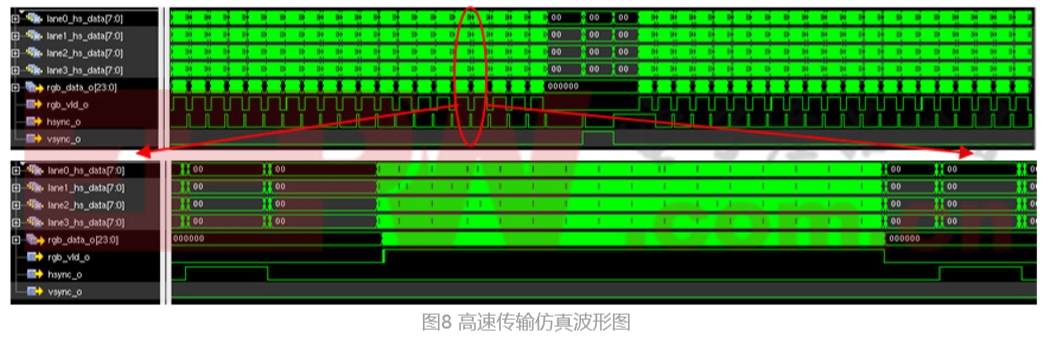

運行仿真后得到如圖8所示的波形圖,可以看出4個 通道都支持高速數據傳輸模式,能將接收到串行數據轉為并行數據,從數據包中解碼出圖像數據信息,如RGB 數據、數據有效信號、行同步信號、幀同步信號等,符 合設計的功能要求,高速功能通過驗證。其他功能也是 同理進行驗證,不再贅述。

4.3 FPGA原型驗證

在芯片流片前需要進行FPGA原型驗證,將ASIC代 碼移植到FPGA上,進行硬件上的驗證,這樣更接近芯 片實際情況,本質上模擬芯片的實際性能和應用,通過 FPGA快速實現硬件模塊,縮短開發時間,提高開發的 效率,同時可以降低流片的風險和成本,所以也是芯片 設計中的重要流程。如圖9為FPGA言行驗證的平臺,由 MIPI主機、轉接板、連接線、FPGA開發板等組成,驗 證通過后進行流片。

5 結語

本文介紹了一種基于MIPI協議,且應用于高分辨率 微顯示驅動的接口設計,該接口設計采用了四通道的數據差分數據通道和1對 高速差分時鐘通道。首先介紹了微顯示和MIPI接口的研 究必要性,接著介紹了MIPI DSI協議,之后著重講述了 MIPI DSI接口設計的工作原理,以及設計的系統方案、 主要模塊的工作流程,最后介紹了仿真和FPGA驗證的過 程及結果分析。支持高速傳輸模式、Escape模式、TA反 向傳輸模式,在低功耗模式下傳輸速率10 Mbit/s,高速 數據傳輸速率可達到900 Mbit/s。目前已完成設計,并經 過反復的仿真和驗證,達到了設計要求,已完成流片。

參考文獻:

[1] 季淵. 超還原硅基有機發光微顯示器研究[D].上海:上海大學, 2012.

[2] 譚振平,黃嵩人.應用于LCOS顯示芯片的MIPI DSI驅動接口IP 設計[J].科技傳播,2016,8(03):78-79.

[3] 譚振平. 基于MIPI協議的顯示驅動接口設計[D].湘潭:湘潭大學, 2016.

[4] 溫浪明. 基于MIPI-DSI協議的LCD驅動接口設計[D].廣州:華 南理工大學,2011.

[5] 鄭杰. 一種適用于全高清顯示的MIPI DSI接口設計[D].成都:電 子科技大學,2015.

[6] MIPI Alliance Specification for Display Serial Interface version 1.01.00[S].MIPI Alliance,2008.

[7] MIPI Alliance Specification for D-PHY version 1.2[S]. MIPI Alliance,2014.

[8] 蘇曉峰.基于MIPI規范的LCD驅動接口設計 [D].廣州:華南理工大學,2011.

本文來源于科技期刊《電子產品世界》2020年第03期第55頁,歡迎您寫論文時引用,并注明出處。

評論