一種高性能隔離運算放大器的設計與分析

Design and analysis of a high-performance lsolated amplifier

本文引用地址:http://www.j9360.com/article/201904/400021.htm容浚源,李頌,張遼,周澤坤,羅萍,張波

(電子科技大學 電子科學與工程學院,四川 成都 610000)

摘要:這款隔離運算放大器分為調制部分和解調部分,調制部分把輸入的模擬信號PWM調制為20MHz的方波信號,通過ADI公司的icouple?磁耦合模塊傳輸到解調部分,解調部分將方波信號解調為模擬的電壓信號。此款運放通過采用高速比較電路、離散采樣網絡和高精度基準源等優化方案,最終可以實現在0V~2.5V精確的1:1傳輸,頻率響應為3 MHz,輸出紋波小于3 mV。

*比賽榮譽:全國大學生集成電路創新創業大賽(ADI杯)全國特等獎

0 引言

本團隊設計系統:在輸入電壓是0V~2.5V的模擬信號中,實現襯底隔離的情況下能夠傳輸增益為1的信號操作,且相位帶寬大,線性度好,噪聲小,具有較小的溫度系數,同時為了使芯片具有更好的帶寬特性,設計系統時將工作頻率提高到20 MHz。

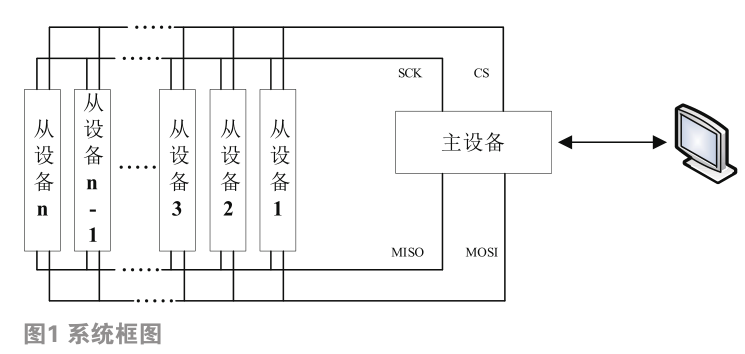

本系統主要由以下三部分組成,分別是:

House keeping模塊和基準模塊,產生基準電壓,供給電流偏置模塊IBIAS分別產生尾電流偏置,作為其他電路的偏置電流,基準后面接LDO型的分壓電路產生帶驅動能力和抗干擾能力的基準電壓,用于實現調制解調,還有產生等腰三角紋波RAMP用于比較器。需要注意的是,在隔離運放的兩側分別都需要一個housekeeping電路。

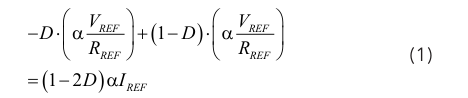

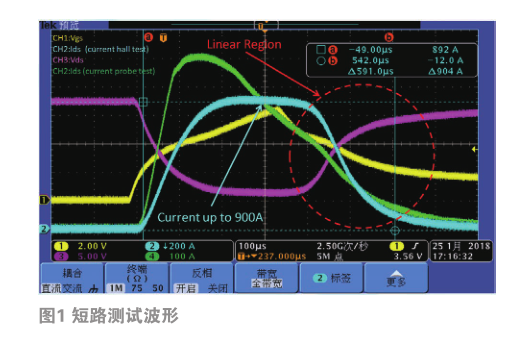

輸入PWM調制環路,如圖1所示,其功能是將輸入電壓V IN 轉化為20 MHz的信息以占空比的形式輸出至第三功能模塊;

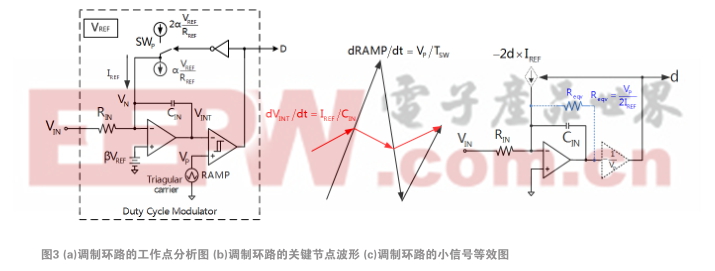

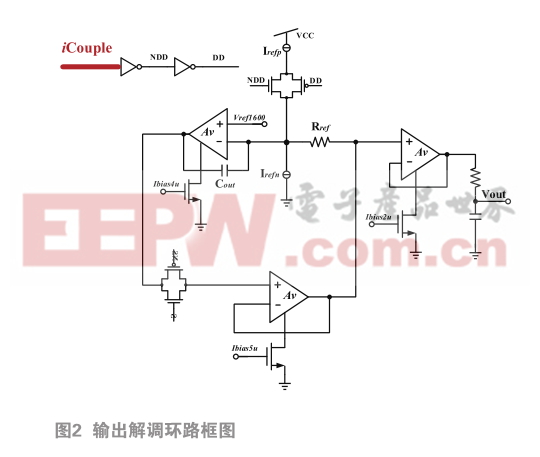

輸出解調環路,如圖 0-2所示,用于將頻率為20MHz的占空比信息轉化還原為模擬的輸出電壓

1 調制環路的直流工作點分析

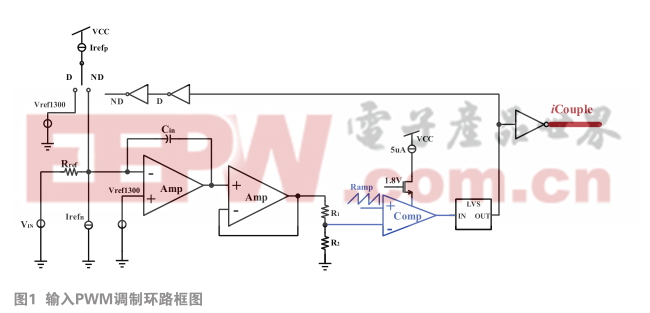

如圖3(a)所示,穩定時刻在忽略周期內的紋波時,運放負端電壓V IN 應鉗位到正端電壓βV REF 。接下來分析V IN 節點上的電流變化,在一個周期內D有效的時間段,開關SW P 斷開,電流源抽走α(V REF /R REF );在一個周期內1-D的時間段,開關SW P 閉合,兩個電流源疊加作用對V IN 節點充電流αV REF /R REF 。那么在一個周期內電流源對V IN 節點提供的電流為:

對上式化簡可得:

為了方便計算,取V REF =1 V,并計算α和β的值。

根據應用條件分別代入V IN =0 V和V IN =2.5 V,再考慮非理想因素將會影響占空比的產生和輸出電壓的復現,避開0%和100%占空比的出現,留有10%的余量即D IN =10%和D MAX =90%,化簡可得:α=1.56,β=1.25。為了方便基準電壓的產生,取α=1.6,β=1.3,最終輸入V IN =0 V時,占空比D IN =9.37%;輸入V IN =2.5 V時,占空比D MAX =93.6%。

2 調制環路的交流穩定性分析

分析調制環路的交流穩定性可以從兩方面入手,一種是從瞬態響應的角度分析,另一種是從環路增益的角度分析。

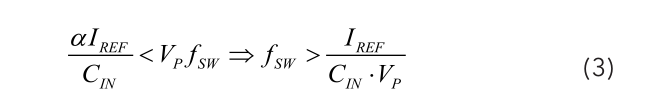

從瞬態響應的角度分析,需要V INT 的變化速度足夠慢,確保每周期V INT 和紋波RAMP比較到。環路結構如圖3(a)所示,在D和1-D的時間段內對V INT 節點充放電電流大小都為αI REF ,則V INT 變化斜率為αI REF /C IN ;假設RAMP為理想鋸齒波,其峰峰值電壓差為V P ,則RAMP斜率為V P /T SW =V P f SW ,則二者的斜率必須滿足如下關系,如圖3(b)所示:

從環路增益角度分析,如圖 0-3(c)所示分析環路增益有,

則環路增益下降為1時對應的角頻率為

將式代入式有

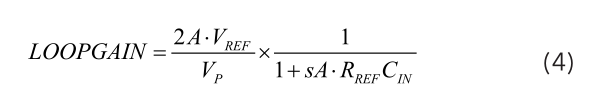

另一方面,取運放AMP輸出到V N 節點電流的增益如下:

根據圖 0-3(c)的等效關系且有:

環路穩定即設法降低ω UG ,即增大R eq1 或者增大C IN 。但是C IN 不應成為主要增大的途徑,因為C IN 同時也是運放AMP的密勒電容,強行增大C IN 將使其成為運放自身小環路的不可忽視極點,反而影響調制環路的相位裕度甚至環路的穩定性;

由R eq1 的公式可知:通過增大R REF 和V P 可以增大R eq1 ,但是R REF 不宜過大,原因是不容易匹配且容易引入各種寄生效應;V P 受限于比較器的共模輸入范圍,且V P 過大也難于產生高頻紋波電路。

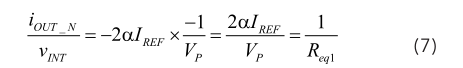

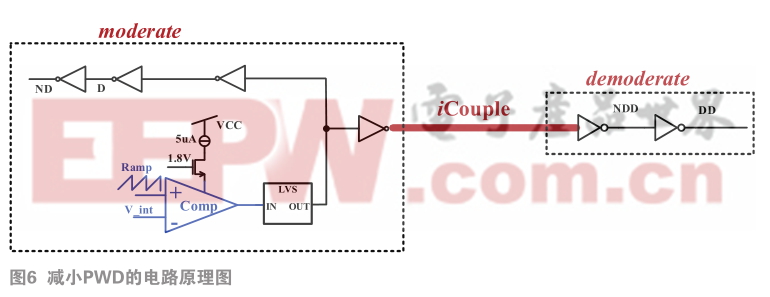

因此本系統將工作頻率為20 MHz,為了提高比較器的響應速度,采用在1.8 V電源電壓構成的比較器,紋波值為0.6 V~1.2 V,同時采用了占空比50%的三角波代替傳統應用中的鋸齒波,一方面更容易產生高頻紋波,另一方面紋波的斜率變為原來的2倍等效增加R eq1 。為此電路需要從5 V電源軌轉換為1.8 V電源軌,電路設計采用1/3分壓結構,而電路如圖4所示。由于RAMP的 電 壓 上 下 限 為 0 . 6V~1.2 V,Vint的動態范圍為1.8 V~3.6 V,不會造成后續的低耐壓比較器電路過壓。

在每個工作周期內,當比較器獲得比較結果后,通過快速的電平位移電路LVS將電源軌迅速恢復到5 V進行傳輸或者反饋,最終V IN 轉化為頻率20 MHz的信息,并以占空比的形式傳輸。

3 解調環路的直流工作點分析

通過將運放的負輸入端鉗位到βV REF ,可以得到穩定態關系,有

因此輸入等于輸出,電壓實現傳輸。

解調環路的交流穩定性分析與分析調制環路的方式一樣,根據圖2,可以先從各部分的增益入手即算整個環路的環路增益。

本系統采用離散采樣電壓進行反饋,主要作用是利用開關的作用用采樣的方式抑制運放輸出在周期內的紋波反應到真正的輸出,對于采樣模塊的離散傳輸函數為1

在頻率低于1/π倍的f SW 時(奈奎斯特定理,但這是必須要實現的),在s域的等效增益也為1,因此對環路沒有影響。值得說明的是,兩級采樣的增益也為1,但是在s域是相當于引入相位滯后,會令環路的相位裕度變小甚至不穩定。采樣結果到輸出電壓經過一個buffer增加帶載能力,防止輸出節點被電流鏡的切換影響。

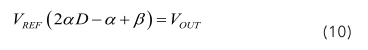

在本設計下,解調環路的環路增益LOOPGAIN為

為了調值環路和解調環路匹配,選取C OUT =C IN ,R OUT =R IN =R ref ,因此有f UG 為

因此采樣系統對環路穩定性和連續性建模沒有影響且環路穩定。

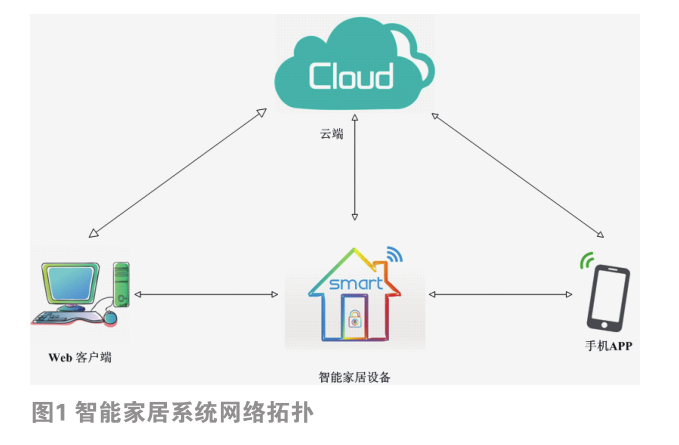

減小失配的策略分析與實施方案考慮輸出電壓誤差,輸出電壓與輸入電壓關系為

由式可得,引起誤差的只有兩項,即V OS_INT 和PWD,其中,V OS_INT 來源于調制環路和解調環路各自引入的誤差;PWD來源于傳輸過程中占空比改變,因而導致調制端的反饋占空比和解調端接收的占空比信息不一樣。

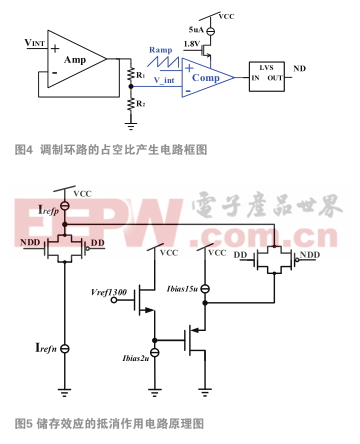

此文減小VOS_INT的主要方法除了提高環路增益還有減少開關動作的干擾。如圖5所示,當開關斷開以后,圖中節點Irefp將會被充電到5 V,在下周期開關重新閉合時,將會注入一股額外的電流對運放輸入端進行充電,而這股電荷因為開關斷開而不會被抽走,相當于引入很大的失配。為了消除這種影響,在開關斷開的時候另一路的開關閉合,源隨器將節點Irefp節點鉗位至βV REF ,當開關重新再打開時,額外注入的電流將會減少。

在減少PWD方面,本設計通過構造相同傳輸電路結構的方式,盡量保證從level-shifter分別到調制端和解調端電流鏡的占空比信號的延時一樣,盡可能保證兩側的占空比信息相等以減小PWD進而減小系統失配。

另外,開關頻率上的紋波也是值得消除的,因此輸出電路采用濾波電路減少開關頻率上的紋波大小,獲得更穩定的輸出。

4 系統參數仿真與結果

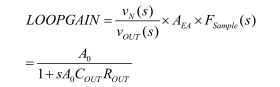

V IN 輸入一個直流電壓電平,仿真到穩定狀態后的3us時間內用軟件計算這3 us的輸出平均值(系統從啟動到穩定只需要7 us),輸入從0 V~2.9 V掃描90個點,cadence軟件自動生成曲線如圖7所示。

從圖中可以看到輸入低壓(約0 mV~250 mV)的幾個點輸出有失配,主要原因在于解調端運放擺幅限制決定的,運放下擺幅為Vov約為250 mV,和仿真結果對應;可以得到增益誤差為-0.22%,小于要求的0.25%;平均輸入輸出失配電壓是3.8163 mV,小于5 mV。

去 掉 圖 中 過 度 偏 離 曲 線 的 M 2 點 , 取 最 小 值V O,MIN =1.25216 V,最大值V O,MAX =1.25235 V,平均值AVG=1.25225。平均溫度變化速度為1.5 μV/℃,溫度系數為1.278 ppm/℃。

圖9是利用PAC仿真后得到的三個conner的波特圖,從上圖可得若以-3 dB處作為極點,則極點位置大概在3.3 MHz,若以90度相位滯后作為極點位置,則極點出現在1.8 MHz左右。

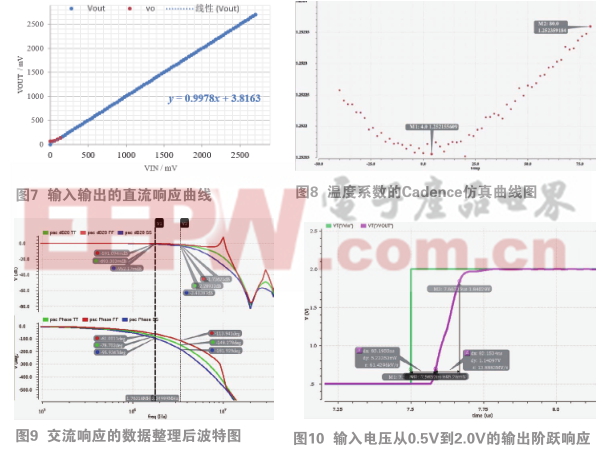

圖10 是輸入電壓從0.5 V到2.0 V階躍跳變,輸出電壓進行相應的波形,跳變在0.01 ns內完成,從圖中可得輸入到輸出發生10%變化的響應延時是85.2 ns,輸出10%到90%的上升延時是82.15 ns。

5 結論

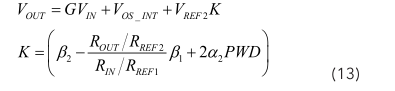

如表1為所有結果統計表。

參考文獻

[1] Razavi, Behard. Design of analog CMOS integrated circuits= 模擬CMOS集成電路設計[M]. 清華大學出版社, 2005.

[2] Zhou Z K, Shi Y, Huang Z, et al. A 1.6V, 5-ppm/C, C Curvature-Compensated BandgapReference [J]. Circuit & Systems I Regular Papers IEEE Transactions, 2012, 59(4): 677-684.

[3] Zhou Z K, Zhu P S, Shi Y, et al. A CMOS Voltage Reference Based onMutual Compensation of Vtn and Vtp [J]. IEEE Transactions on Circuits &Systems II Express Briefs, 2012, 59(6): 341-345.

[4] Bult K, Geelen G J G M. A fast settling CMOS op amp for SC circuitswith 90-dB DC gain [J]. IEEE Journal of Solid-State Circuit, 2002:108-109.

[5] Razavi B. Rotary TravelingWave Oscillator Arrays: A New ClockTechnolgy [C]// Wiley-IEEE Press, 2009:318-329.

本文來源于科技期刊《電子產品世界》2019年第5期第56頁,歡迎您寫論文時引用,并注明出處

評論