高速多通道CCD預放電路設計

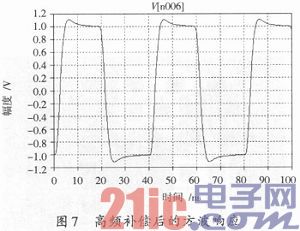

高頻補償后的放大器對方波的響應如圖7所示。本文引用地址:http://www.j9360.com/article/201809/388654.htm

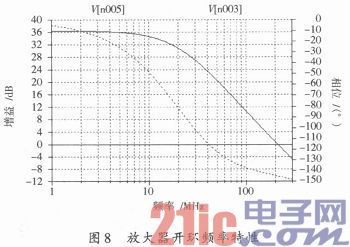

放大器的開環頻率響應如圖8所示,可以看出當放大倍數將為0 dB時,相位為-145°,不存在穩定性問題。

4 結論

高速多通道CCD預放電路設計中存在預放電路不能足夠靠近CCD的問題。高速運算放大器存在容易自激振蕩的問題。針對上述兩個問題,從電路原理和電路板設計的角度進行了高速多通道CCD預放電路分析和設計。通過電路原理設計中應用高頻補償技術,有效地解決了帶寬限制問題。通過電路板設計中去除運算放大器反饋端地平面的方法有效地避免了自激振蕩。因此,該設計可以有效地應用在高速多通道CCD成像電

路中。

評論