Achronix與Mentor共同打造以高等級邏輯綜合(HLS)與FPGA技術的連接推動5G應用新發展

FPGA技術因為具有其并行執行、運算性能高、功耗低、可重配置以及相比ASIC開發周期短等優點,目前在各個領域中都有廣泛的應用。但是隨著FPGA器件資源容量的不斷提高,邏輯設計的規模也越來越大,傳統的邏輯代碼設計變得十分復雜,開發周期也愈發漫長。由此,在2018年8月,基于現場可編程門陣列(FPGA)的硬件加速器件和嵌入式FPGA(eFPGA)半導體知識產權(IP)領導性企業Achronix半導體公司(Achronix Semiconductor Corporation)日前宣布:該公司FPGA技術系列產品已獲得其合作伙伴、西門子旗下的Mentor公司的支持,將持續為其提供優化的高等級邏輯綜合(HLS)流程。 HLS的引入,對于提高FPGA開發效率,提高算法的收斂、迭代速度,有著非常明顯的效果。

本文引用地址:http://www.j9360.com/article/201808/391383.htm該集成開發環境使設計人員能夠使用Mentor的Catapult?HLS和Achronix的ACE設計工具快速的用C ++實現FPGA設計。此項合作首先已可用于5G無線應用,以減少整體開發工作并提高結果的質量(QoR),它適用于任何面向Achronix技術的設計。

“Mentor功能強大的Catapult工具和Achronix的嵌入式FPGA技術結合在一起,可為那些其SoC設計需要高性能FPGA技術的公司提供了真正獨到的價值組合,而這些SoC可以使用經過驗證的、基于C語言的設計流程來進行配置,”Achronix負責市場營銷的副總裁Steve Mensor評論道。 “這種組合型解決方案很好地證明了Mentor和Achronix工程團隊之間的緊密合作關系。 我們首先面向的目標應用是5G無線,但是在其他許多需要最快開發時間的細分市場應用中,這項整體解決方案的獨特功能都有其價值。“

“我們高興地歡迎Achronix加入Mentor OpenDoor計劃,并樂于成為Achronix合作伙伴計劃的活躍成員。 這種開放且相互配合的合作伙伴關系具有非常高的戰略意義,并已經被證明是有益于我們的共同客戶,“Mentor公司Calypto Systems業務部市場營銷總監Ellie Burns說到。 “Achronix eFPGA提供了極強大的功能,它能夠適應一款具有現場可編程能力的SoC的后期變化和新要求。 再加上Catapult HLS和C ++的驗證速度,芯片設計人員現在可以在幾天而不是幾周或幾個月內輕松地從算法更改轉化為全新的低功耗、高性能硬件。“

將Catapult添加到Achronix設計流程

將Catapult HLS添加到Speedcore嵌入式FPGA技術設計流程,可使設計人員能夠在IP開發的后期階段進行算法更改,并優化算法和數字微架構。 集成化的驗證環境支持為已生成寄存器傳輸級(RTL)的代碼去重用軟件測試,從而將對專用RTL測試臺的需求減少80%以上。

Achronix ACE設計工具支持Catapult的RTL構造和原生語句。 目前,用于Achronix的Speedcore eFPGA產品及其Speedster獨立FPGA芯片的Achronix邏輯庫已被集成到流程中。

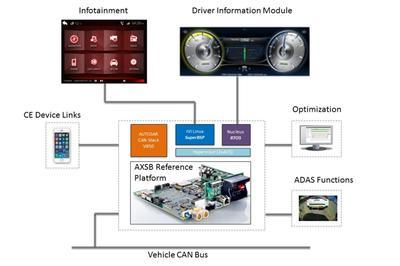

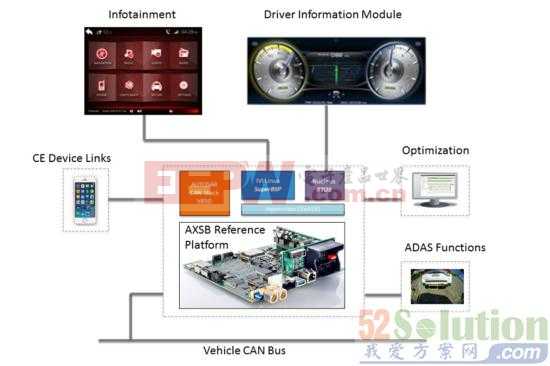

Achronix的高性能和高密度FPGA技術可用于數據中心計算、網絡和存儲中的各種硬件加速應用,5G無線基礎設施及網絡加速,先進駕駛員輔助系統(ADAS)和自動駕駛汽車。

Achronix經過Mentor公司的高等級邏輯綜合(HLS)流程支持后不斷優化的FPGA技術,和之前相比在性能開發、功能實現等方面都有著很大的進步,并且能使芯片設計的過程中低功耗和高性能,讓更多的研發人員,甚至算法設計人員,可以更加容易的使用FPGA完成設計。也更能發揮出FPGA并行的優勢,并且此項合作也應用到5G無線應用中,必將對今后5G技術產生重大影響。

評論