實現最高效的數據轉換:深入了解Achronix JESD204C解決方案

長期以來,Achronix為不同行業的數據密集型和高帶寬應用提供了創新性的FPGA產品和技術,并幫助客戶不斷打破性能極限。其中一些應用需要與先進的模擬/數字轉換器(ADC)和數字/模擬轉換器(DAC)進行對接——可由JESD204C完美地完成這項任務。

本文引用地址:http://www.j9360.com/article/202312/454288.htmJESD204B/C是由JEDEC定義和開發的高速數據轉換器串行接口標準。該標準減少了高速數據轉換器和其他高性能器件(如Achronix Speedster7t FPGA)之間的數據輸入和輸出數量。這種數字和模擬信號鏈的組合使設計人員能夠獲得簡化的小尺寸電路板布局,同時不會對終端系統的性能產生不利影響,從而使設計人員受益。通過高速通用I/O(GPIO)或SerDes通道來實現數據轉換器件之間的接口/互連。

Achronix在其Speedster7t FPGA器件上已經實現了JESD204C接口,使客戶能夠使用他們所選擇的ADC或DAC。由于是在同構FPGA架構上實現了軟的JESD204C接口,客戶可以使用他們喜歡的ADC/DAC器件并使其設計實現定制化。本文討論了基于Achronix Speedster7t FPGA器件的JESD204C解決方案。

Achronix JESD204C解決方案支持該標準提及的所有功能,并對以前的版本進行改善。旨在實現由標準機構提出的所有的四個目標:

·提高通道速率以支持所需的更高總帶寬——Achronix的解決方案目前支持每SerDes通道高達24.75 Gbps的數據速率。SerDes可以支持32 Gbps的JESD204C上限通道速率。用于測試設計的數據轉換器使用的是Analog Devices(ADI)的AD9082,它支持的最大數據速率為24.75 Gbps。

·提升有效載荷傳輸效率——Achronix的用戶可以使用FPGA邏輯來對其設計進行定制和優化。

·鏈路穩健性——Achronix的解決方案展示了在單通道和多通道模式鏈路的高度穩健性,同時保持確定性的延遲。例如,對于那些沒有量化效應的模式,采樣率可以達到AD9082支持的最高極限。

·向后兼容先前的JESD204B版本——Achronix將會提供JESD204B解決方案。

實驗室測試方案

Achronix已成功實現并演示了Speedster7t JESD204C的解決方案,該解決方案可連ADI的AD9082,AD9082帶有四通道16位DAC和雙通道12位ADC轉換件。實驗環回設置(如圖1所示)包括以下組件:

·Bittware的VectorPath S7t-VG6加速卡。板上使用的是Achronix Speedster7t FPGA器件。

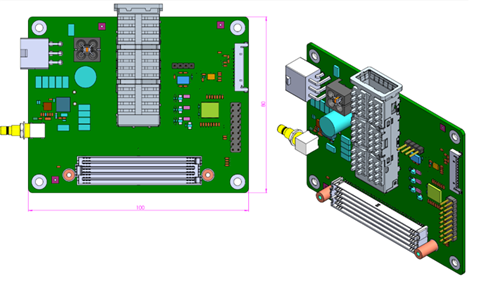

·連接VectorPath和ADI的EVAL-AD9082連接器。Achronix開發了一塊4-lane的QSFP到FMC的連接器,如果有需要的話,還可以調整為8通道或16通道。

·配備FMC連接器的ADI EVAL-AD9082 ADC/DAC板卡。

·所需的測試設備和其它配件。

圖1:連接VectorPath和ADI的EVAL-AD9082連接器板卡

實驗設置給發送(Tx)的和接收(Rx)的方向上提供完整的信號鏈。各組件的功能如下:

·在VectorPath加速卡上的Speedster7t AC7t1500 FPGA器件中實現JESD204C發送/接收IP功能。通過連接的PC上的Linux控制臺運行特定的測試腳本。

·Speedster7t SerDes通道通過定制的FMC-QSFP連接器板卡連接到ADC/DAC。QSFP28模塊支持四個SerDes通道,每個通道的運行速度為24.75 Gbps。

·通過所連PC調用API,完成對ADI的AD9082-FMCA-EBZ評估板上數千個寄存器進行編程配置。另外,也可以使用FPGA上的軟CPU核或SoC中的硬CPU核對寄存器進行編程配置。

·外部時鐘源使VectorPath加速卡和AD9082-FMCA-EBZ評估板同步。也可以通過使用AD9082-FMCA-EBZ上的振蕩器來生成內部時鐘,并通過FMC-QSFP連接器饋送到VectorPath加速卡。

·由一個任意波形發生器(AWG)產生波形被通過外部直傳送給ADC0和ADC1。

·環回發生在Speedster7t FPGA內部,處于JESD204C接收和發送模塊之間,而DAC輸出顯示在示波器上。

·DAC0和DAC1輸出的預期波形顯示在連接的示波器上。

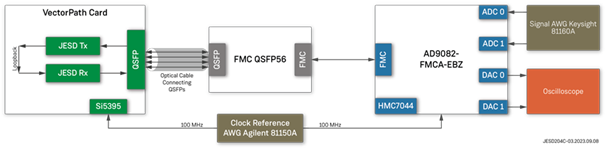

圖2:四通道環回示例

上圖顯示了一個四通道環回配置。信號路徑為AWG(I/Q信號)→AD9082-FMCA-EBZ(ADC)→FMC QSFP56→Speedster7t JESD204C Rx→環回→Speedster7t JESD204C Tx→FMC QSFP56→AD9082-FMCA-EBZ (DAC)→示波器。

AD9082-FMCA-EBZ的ADC0和ADC1的輸入I/Q波形具有相同的頻率,但相位相差90度。頻率取決于AD9082-FMCA-EBZ支持的模式,該設置可以在最小且可接受的抖動下,實現該特定模式所聲明的最高頻率。

基于Speedster7t FPGA器件,實現的先進的Achronix JESD204C解決方案,可以實現JESD204C數據轉換器所支持的最高速率。該解決方案為連接的ADC/DAC設備提供了一個與供應商無關的接口,從而支持客戶可以選擇他們喜歡的ADC/DAC供應商。

評論