如何使用一個DSP block實現4個11位浮點型數據乘法運算

概述

本文引用地址:http://www.j9360.com/article/201808/390514.htm隨著深度學習的發展,為了解決更加抽象,更加復雜的學習問題,深度學習的網絡規模在不斷的增加,計算和數據的復雜也隨之劇增。INTEL FPGA具有高性能,可編程,低功耗等特點,為AI應用加速提供了一種靈活、確定的低延遲、高通量、節能的解決方案。Arria10是INTELFPGA第一代集成IEEE754標準單精度硬浮點DSP block,可以為高復雜度的深度學習算法提供高精度,高能效的乘法運算。

深度學習算法復雜度高,需要進行大量的乘法運算,如實現一個卷積核為5*5的特征提取,需要進行25*25次乘法運算,而隨著特征提取量的增加,乘法運算也將成倍的增長。因此乘法器資源是實現深度學習算法的重要評估資源,本文主要介紹如何基于Arria10的一個18*18的乘法器實現兩個11*11的浮點mini-fp運算,從而4倍提高DSP block資源。

原理分析

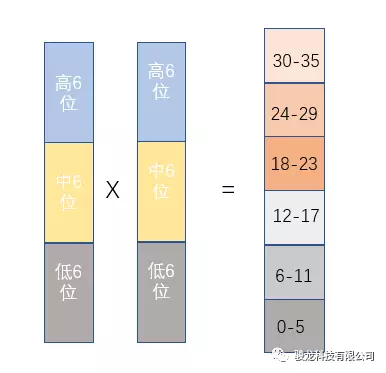

Arria10可變精度的DSP Block支持配置為兩個18*18或者18*19定點乘法器,進行18*18乘法運算時,如圖1所示,將輸入拆分為低6位,中6位,高6位,進行運算分析。

圖1 18*18乘法器運算

則對應的運算結果如下表所示:

將中6位輸入全設為0,則可以得到對應的輸出結果如下表所示:

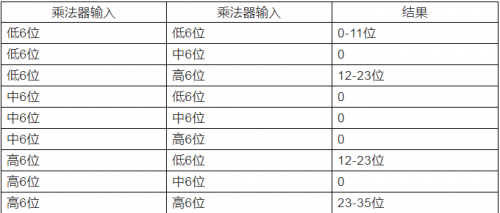

當高6位及低6位為帶符號位的輸入數據時,進行符號位提取,則剩余的實際數據有效位為5位,因此低6位*高6位及高6位*低6位的乘法結果最高有效位均為10位,進行兩個結果的加法運算,可以保證結果在12-23位以內,不會對高6位*高6位乘法結果造成影響。因此Arria1018*18的乘法器支持進行符號位提取后的兩個6*6的乘法運算,圖2是對應的仿真結果,乘法結果對應延時2個時鐘周期。

圖2 modelsim 仿真結果

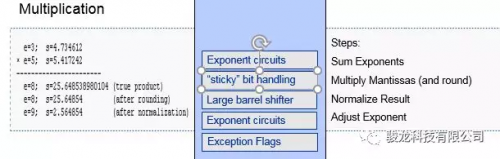

浮點型數據如圖3所示,包含符號位S,指數位E及尾數位M。

圖3 浮點型數據組合

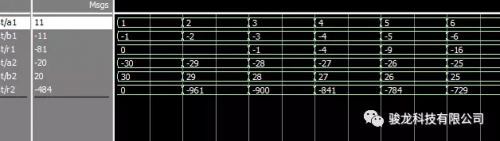

進行浮點型數據乘法運算,如圖4所示。

圖4 浮點型數據乘法

需要進行指數相加,尾數相乘,乘法結果取整及指數的調整。11位的浮點型數據尾數及指數各占5位,因此進行乘法運算僅需要進行包含符號位6位的數據相乘及對應的處理即可。Arria10的DSPblock可支持配置為2個18*18乘法器,而一個18*18的乘法器可以實現兩個6*6的乘法運算,因此一個DSPblock可以實現4個11位浮點型數據mini-FP的乘法運算。

評論