DSP的30年

要點

本文引用地址:http://www.j9360.com/article/201808/387562.htm1. DSP設計人員尋求優(yōu)化TI所稱的“三P價值”,即:性能、價格與功耗。

2. ADI設計人員了解其DSP所面向應用的功率包絡。

3. Microchip對數(shù)字信號處理采用了一種替代方案:數(shù)字信號控制器。

4. 未來,可編程ASSP器件為TI的DaVinci這類器件提供了一種替代品,將面向某些市場中的FPGA。

如德州儀器(TI )公司首席研究員GeneFrantz所言,該公司DSP先驅的頓悟始于上世紀70年代末,恰好在TI公司創(chuàng)造性的Speak Spell學習玩具放上零售貨架后不久。Frantz回憶那時有個顧客問:“如果你們可以用DSP給玩具加上語音合成,還能用它做別的什么嗎?”

當今年TI公司慶祝在DSP市場的30周年時,這個長久以來的問題已經過了無數(shù)次的解答。如果沒有DSP以及它在音頻、圖像和多媒體處理方面的推動作用,就不會有“信息娛樂”內容,沒有智能手機或平板電腦,沒有互聯(lián)網,也沒有APP的生態(tài)系統(tǒng)。

TI的“玩具”技術不僅促使公司進入了一個新的業(yè)務領域,而且為TI、其競爭對手以及工具供應商的開發(fā)建立了舞臺,推動DSP技術進入了各種應用與市場。與此同時,傳統(tǒng)DSP器件遭遇了各種替代性信號處理平臺的競爭,包括有DSP特性的CPU、用微控制器與DSP核心配對使用的數(shù)字信號控制器、用于為數(shù)字信號處理設計定制的數(shù)據(jù)路徑,甚至創(chuàng)建定制可編程處理器的FPGA,以及最新出現(xiàn)的有大量并行處理的圖形處理器,它可以解決數(shù)據(jù)并行問題。

DSP技術的起源要比Speak Spell玩具早幾年。在上世紀70年代初期,科學家們開始采用市售的現(xiàn)成TTL分立邏輯芯片,實現(xiàn)專門的信號處理“引擎”。早期系統(tǒng)相對速度緩慢,占用空間大。TRW公司在1973年發(fā)布了第一款實用的并行乘法器,并在兩年后增加了位片(bit-slice)ALU。但僅乘法器芯片就要數(shù)百美元,唯一能買得起這種產品的客戶只有研究實驗室、醫(yī)療掃描設備制造商及軍隊。

1978年,American Micro- systems公司推出了第一款專門為DSP設計的單芯片IC:12位的S2811。AMI發(fā)明了一種真正創(chuàng)新性電路設計,但其芯片實現(xiàn)時采用了一種激進的“V槽”(V groove)MOS技術,而這種技術從未用于量產的商業(yè)產品。

第二年,英特爾公司推出了Intel2920 16位“模擬信號處理器”,起這個名稱是因為英特爾要設計一種用于直接替換模擬電路的芯片,包括了板上的A/D和D/A轉換器。2920以數(shù)字形式處理模擬信號,但它缺少一個并行乘法器;此外,它600ns的周期速度太慢,無法在音頻段做出有用的工作,而音頻段是第一個大批量DSP芯片的市場。

第一只“真正”單芯片的DSP出現(xiàn)在上世紀80年代初,由貝爾實驗室和NEC推出, 市場分析公司Forward Concepts將其定義為并行MAC(乘法器-加法器)電路。貝爾實驗室的芯片叫DSP-1,是一種用于ATT與Western Electric設計中的容性器件。NEC的μPD7720是第一種真正量產、在商業(yè)市場上發(fā)售的單芯片DSP。盡管受制于粗糙的開發(fā)工具,NEC的芯片仍然可提供充足的速度,它用一個雙周期MAC實現(xiàn)122ns的周期時間,能夠在音頻段做一些有用的工作。

80年代末,理光公司的HiromitsuYagi為傳統(tǒng)的NMOS工藝重新設計了原AMI的S2811芯片。Yagi的工作結果是理光RD28211和AMIS28211。

TI加入游戲

在80年代,TI公司的Ed Caudel設計了后來成為該公司第一款DSP的初始架構。同年,Surendar Magar受雇圍繞DSP算法來優(yōu)化架構。1982年2月,TI在傳統(tǒng)的“國際固態(tài)電路研討會”上以一篇《具有數(shù)字信號處理能力的一種微計算機》(參考文獻1)的論文將設計結果公諸于世。1982年4月,Caudel在巴黎召開的“音頻、語音與信號處理國際研討會”上宣布了最終產品—TMS32010。

推出Speak Spell后,TI公司繼續(xù)為各種行業(yè)開發(fā)DSP器件,但業(yè)務的關鍵以及對市場增長起決定性作用的,還是圍繞處理器所出現(xiàn)的生態(tài)系統(tǒng)。業(yè)界最早的DSP工程師之一Frantz說:“TI成為第一家擁有一款復雜的信號處理芯片的公司,也理解到器件本身并非產品,產品是器件加支持加開發(fā)環(huán)境加一條器件熱線。我們?yōu)榭蛻魟?chuàng)造了一個產品,使他們可以將其用在自己的產品中。”

在早期年代,TI的DSP熱線是為客戶提供幫助的一個重要來源,尤其是很多情況下,回答電話問題的人正是被咨詢器件的架構師。Frantz說:“TI有一些非常大的客戶,我們接到這些大客戶從不同地區(qū)打來的電話,有六到七個不同區(qū)號。我們發(fā)現(xiàn)自己比他們還清楚他們公司在做什么東西。我們盡自己所能幫助他們發(fā)展。”也有很多來自小型新興公司的電話,咨詢著相同的問題,而TI早在業(yè)內成員順應趨勢做出選擇以前, 就看到了正在形成的市場。Frantz指出,這以后幾年間,公司發(fā)明了下一代信號處理器,做出了客戶想要獲得的“瘋狂”東西。在此過程中,TI一直牢記“三P價值”,即:性能(performance)、價格(pr ice)以及功耗(power di s -sipation)。Frantz說:“大多數(shù)人并不明白功耗是多么重要,但我們自60年代中期就一直致力于小功率器件技術,當時已經發(fā)明了計算器。”初期,TI開始了它的第三方計劃,鼓勵有DSP專業(yè)能力的小型公司去“填充”TI無法照顧到的“空白”。Frantz將計劃描述為一個“價值網”,所有參與者都可以通過它獲得收益,同時擴展了現(xiàn)有的客戶支持網絡。

Fernando Mujica是TI系統(tǒng)架構實驗室主任,是分析嵌入式處理方面的專家,他從Frantz這些DSP先鋒手中接過了接力棒。Mujica說:“過去30年來,我們生活中的方方面面幾乎都受到了DSP的影響。現(xiàn)在,我們正看到DSP開始做嵌入分析工作,這是需要最高程度可編程性的一個不斷增長和發(fā)展的領域。現(xiàn)在,信號調整與壓縮技術都實現(xiàn)為硬編碼的加速器,并與DSP整合在現(xiàn)代的嵌入式處理器中。”

今天的DSP和其它嵌入式處理器承擔了以往需要人工干預的工作。相關例子是拓展了汽車安全功能的范圍,包括偏離車道警告和主動巡航控制等,這些已出現(xiàn)在高檔汽車中。這些系統(tǒng)已超出了便利功能范疇,它們會向駕駛者提出警告,乃至在緊急情況下做剎車或轉向操作。

Mujica表示:“在不久的將來,嵌入分析解決方案將使自動化駕駛成為一種現(xiàn)實(圖2)。機器人是另外一個即將出現(xiàn)革命性變化的領域,因為嵌入式處理器的性能在增長,它們已能完成復雜的分析任務。”

小功率創(chuàng)新者

TI不是唯一一家在“三P價值”上推動DSP技術發(fā)展的公司。ADI公司以2001年開發(fā)的定點Blackfin處理器和90年代中期的浮點Sharc處理器,堅定不移地改進著功率/性能比。

隨著對處理精度的需求越來越高,設計者不斷地面臨著解決功率預算需求的難題。ADI公司處理器營銷總監(jiān)Colin Duggan以及Blackfin產品經理Richard Murphy表示,ADI公司專注于現(xiàn)有功率的高效利用,從而獲得越來越緊湊的設計,可確保有更好的系統(tǒng)便攜性,占據(jù)最少空間,使得總體運行成本較低。他們指出,低功耗通常發(fā)熱低,有助于獲得更高的系統(tǒng)可靠性,減少了系統(tǒng)級與空間級的冷卻,從而節(jié)省了相關的功率、空間和成本。

對于電池供電設備,較低功率的處理器能延長系統(tǒng)電池的壽命和充電間隔,有助于減小系統(tǒng)尺寸和重量,保證了便攜能力。處理器功耗的下降也讓設計者可以使用較小的電池,最大限度地節(jié)省了功耗與空間。

剛剛發(fā)布的BF60x高性能系列以及前代Blackfin中都采用了DPM(動態(tài)電源管理),開發(fā)人員可以將處理器功耗與程序執(zhí)行時的處理需求相匹配(圖3)。20 01年10月,ADI率先將DPM應用于首款發(fā)布的Blackfin處理器中。小功率處理器延長了系統(tǒng)電池的壽命,有助于減小系統(tǒng)體積與重量。

Blackfin處理器中采用的其它設計技術包括:可編程電壓以及頻率縮放;時鐘周期分辨率的動態(tài)時鐘門控;多電源域,支持深度睡眠與冬眠模式;高代碼密度,盡量減少了激活總線的能量;采用混合閾值電壓晶體管,獲得了最佳性能與功率效率;一個最高能效的全定制處理器核心;審慎采用硬件加速器;以及支持亞穩(wěn)態(tài)SDRAM,使板級功耗降至最低。

在浮點方面,ADI仍牢記低功耗技術,設計出了最新的Sharc 2147x。該處理器有5Mbit片上內存,設計者可以將功率存儲起來,以備擴展將數(shù)據(jù)移動到外存和其它處理器。該系列的集成內存與并行處理特性能夠提高性能,確保算法和程序執(zhí)行得更快,從而得到了凈功耗下降的好處。

兩兩比較(均在的典型功耗)有助于ADI做出方案。在Sharc系列中,ADSP-21261在150MHz時功耗為900mW,200MHz時為1.2W;與之相比,最新的ADSP-2147x系列在150MHz時功耗180mW,在266MHz時功耗363mW。在Blackfin系列中,BF527在600MHz時的核心功耗為205mW,待機功耗為10mW,而冬眠模式耗電大約為40μA;最新的BF592在300MHz時提供88mW的動態(tài)功耗,待機功耗不到1mW,冬眠耗電為20μA。該公司最高性能的Blackfin BF609有兩個500MHz核心,在1GHz時耗電400mW。

Duggan和Murphy指出,ADI的節(jié)電特性提供了靈活的控制,更新的工藝尺度有更高的功率效率。他們補充說,該公司的設計者都了解其DSP所要滿足的應用的功率包絡。

ADI的目標是,盡可能在應用的一個特定功率包絡中獲得最高的性能。用戶可編程PLL,可調降自身系統(tǒng)時鐘的外設,以及當某些外設不工作時關閉任何時鐘域的能力等,都可以節(jié)能。其它節(jié)能方案包括:采用高效的總線架構,盡量增加設計中采用高閾值電壓晶體管的百分比(一般為93%),以及使用PVP(流水線視覺處理器)做為加速器。

Microchip的DSC

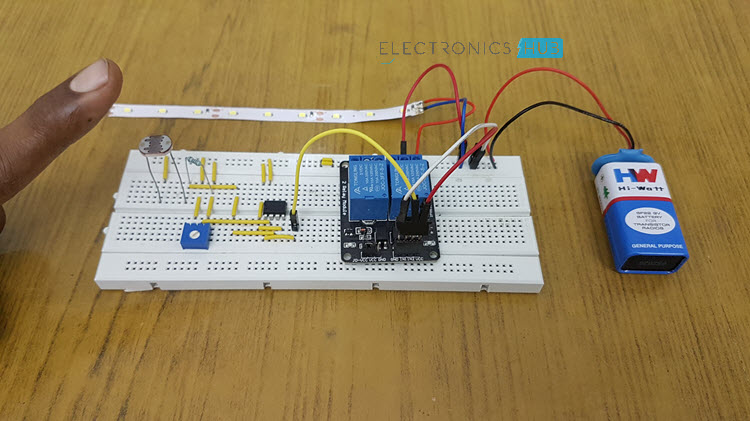

Microchip Technology公司的數(shù)字信號處理采用了另一種方案:DSC(數(shù)字信號控制器)。第一款芯片是用一個DSP與一只8位微控制器配對。然后,Microchip的工程師在一個PIC微控制器中集成了一個DSP核心,這就是2002年面世的16位dsPIC(參考文獻5)。

可縮放的dsPIC解決方案提供了專利的微控制器式中斷處理,可用于實時控制,據(jù)Microchip稱,用DSP做實時控制一直面臨著挑戰(zhàn)(圖4)。DSC核心采用一種修改過的Harvard總線架構,有16位寬的數(shù)據(jù)路徑和24位寬的指令路徑;廣泛尋址模式;一個16×16位的通用寄存器集;一個靈活的軟件棧;單周期16×16乘法功能;帶雙端口SRAM的DMAC(直接內存訪問控制);以及八個外設通道。

DSC的運行速度從30MIPS到70MIPS,用于數(shù)字電源、照明、電機控制、語音、生物計量、傳感器處理以及簡單濾波器等市場。芯片包含了用于語音處理的DAC、電機控制PWM、快速ADC,以及專門用于SMPS(開關電源)應用的ADC。Microchip公司稱這些器件具有高運放集成度,提供了微控制器般的“觀感”,設計者無需學習DSP設計或軟件就可以使用。

Microchip鼓勵從dsPIC到PIC24微控制器的無縫遷移,兩者的代碼與引腳兼容。同樣免費的MPLABX集成開發(fā)環(huán)境可用于Microchip的8位、16位與32位微控制器及其DSC。該公司稱其戰(zhàn)略是為工程師們提供簡單的解決方案,使應用開發(fā)人員(如數(shù)字電源)能夠方便地使用模擬友好的高度集成dsPIC。

轉向FPGA

從傳統(tǒng)DSP轉向基于FPGA的DSP硬件,這個過程會涉及一組新的設計技巧,以及對硬件的新理解。對于剛開始使用FPGA或DSP的開發(fā)人員,這種轉換可能是一個相當大的任務,它增加了設計日程的風險。高級經理Tom Hill為Xilinx編寫過一份白皮書《Xilinx DSP設計平臺:簡化FPGA在DSP中的使用》(參考文獻6),其中給出了Xilinx的DSP開發(fā)套件設計思想,以簡化FPGA的采用,算法與硬件開發(fā)人員在用Xilinx器件開發(fā)DSP應用時,能快速地進入狀態(tài)。

Hill指出,在90年代時,Xilinx設計了用于DSP處理的4000 系列FPGA。客戶很快發(fā)現(xiàn),他們可以用FPGA建立數(shù)字濾波器。大約1999年,時任Xilinx現(xiàn)場應用工程師的Bruce Newgard認為公司有一個很大的機會,但管理層需要一些有說服力的東西,才同意在Xilinx內部成立一個DSP部門。

2005年,Xilinx打造完成了一個DSP戰(zhàn)略,即與TI和MathWorks合作,為算法開發(fā)與設計實現(xiàn)引入FPGA/DSP協(xié)處理平臺和緊密集成的工具流。同一年,F(xiàn)orward Concepts估計,基于FPGA DSP解決方案的性能與靈活性可以應付20億美元的高性能DSP市場。Xilinx初期的目標市場是高增長的數(shù)字通信、MVI(多媒體、視頻與影像),以及防務系統(tǒng)。這些領域加起來,要占到80%以上的高性能DSP市場份額。

Xilinx與MathWorks合作開發(fā)了SystemGenerator,這是業(yè)界第一個針對Xilinx FPGA的DSP插件。今天,SystemGenerator for DSP是采用FPGA做高性能DSP系統(tǒng)設計的一款領先高級工具。

Xilinx 稱, 使用System Generator,沒什么FPGA設計經驗的開發(fā)人員也可以快速地通過算法FPGA實現(xiàn)量產質量的DSP,所花時間只有傳統(tǒng)RTL開發(fā)的幾分之一。工具提供了系統(tǒng)建模以及從MathWorks Simulink的自動代碼生成,并集成了RTL、嵌入、IP、Matlab,以及一個DSP系統(tǒng)的硬件。System Generator for DSP是XilinxDSP目標設計平臺(Targeted DesignPlatform)的一個關鍵部分。

Xilinx已轉換了自己的業(yè)務模型,從水平的FPGA供應商,變成為垂直的應用促進商,在不同的細分市場都有自己的業(yè)務。下一階段是由工具、IP、硅片和套件組成的面向算法的平臺。

Xilinx基于FPGA的DSP平臺現(xiàn)在可與真實世界的信號相連接,并有與高速數(shù)據(jù)轉換器的接口。數(shù)據(jù)會以極高速率采樣,然后下變頻,以簡化DSP硬件實現(xiàn)。Hill指出,F(xiàn)PGA通常用于處理接口和下變頻的系統(tǒng),但40%的情況下會與DSP器件一起使用。

一些用戶對于使用基于FPGA的DSP存在著一些疑問,如技術的易用性以及設計流程的障礙等,因此在2011年1月,Xilinx買下了AutoESL。雙方結合,就是2012年1月的XilinxAutoESL,它使設計者能更容易地快速用FPGA實現(xiàn)DSP系統(tǒng),并提供了向下一代AutoESL技術的一種更平滑轉換,這就是Vivado High-Level Synthesis 2012.2(參考文獻7)。隨著Vivado設計套件的推出,VivadoHigh-Level Synthesis(高級綜合)能夠讓開發(fā)人員將C、C++和System C直接應用于FPGA,而不需要手動創(chuàng)建RTL,從而加快了設計實現(xiàn)。

Hill指出,今天,如果你能用一只DSP做設計,客戶就會使用一只DSP;如果設計要求采用兩片或三片DSP,則FPGA就極有競爭力。對于高負荷的濾波,F(xiàn)PGA具有優(yōu)勢。FPGA能完成無線、雷達與軍用聲納對抗中的上/下變頻和數(shù)字預校正。醫(yī)療影像是另外一個重要領域,如有些CT掃描與擁有256個以上傳感器的超聲設備。

3 月份,Xilinx 推出了Zynq -7000,宣稱在一只器件上集成了“全部可編程的”SoC,它提供ASIC式的性能與功耗、FPGA的靈活性,以及微處理器的編程簡便性(圖5)。Zynq-7000生態(tài)系統(tǒng)包括硬件與軟件開發(fā)工具,以及操作系統(tǒng)。

Hill預測說,未來FPGA將是可編程ASSP的基礎,后者在某些市場領域上將替代TI公司DaVinci數(shù)字多媒體處理器這類器件。

不承認支持DSP算法與架構開發(fā)的工具供應商,就無從談起DSP的歷史。

評論