一種基于LDO穩壓器的帶隙基準電壓源設計

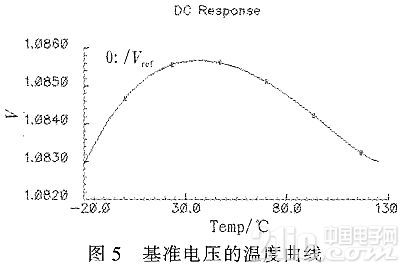

摘要:設計了一種結構簡單的基于LDO穩壓器的帶隙基準電壓源。以BrokaW帶隙基準電壓源結構為基礎來進行設計。采用Cadence的Spectre仿真工具對電路進行了完整模擬仿真,-20~125℃溫度范圍內,基準電壓溫度系數大約為17.4 ppm/℃,輸出精度高于所要求的5‰;在1 Hz到10 kHz頻率范圍內平均電源抑制比(PSRR)為-46.8 dB。電路實現了良好的溫度特性和高精度輸出。

本文引用地址:http://www.j9360.com/article/201808/386554.htm關鍵詞:帶隙基準;LDO穩壓器;溫度系數;電源抑制比;運算放大器

CMOS帶隙基準電壓源不但能夠提供系統要求的基準電壓或電流,而且具有功耗很小、高集成度和設計簡便等優點,廣泛應用于模擬集成電路和混合集成電路中。帶隙基準電壓源為LDO提供一個精確的參考電壓,是LDO系統設計關鍵模塊之一。

基準電壓的精度直接影響輸出電壓的精度,因此高精度基準參考電壓電路是LDO穩壓器的的關鍵。

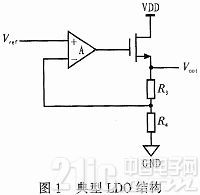

1 LDO穩壓器工作原理

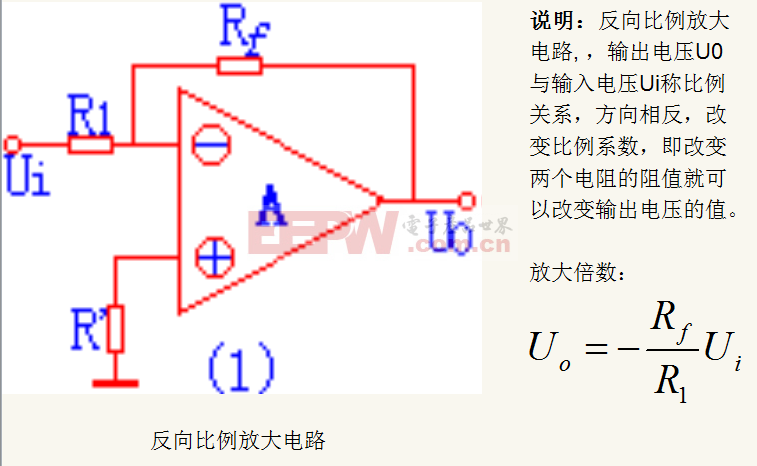

圖1是一個典型LDO電路結構。該結構主要包括4個部分:誤差放大器、電阻反饋網絡、參考基準電壓和調整管。當基準電壓源正常工作后,產生了一個精準的參考電壓,輸入到誤差放大器的同相端。采樣串聯電阻對輸出電壓進行分壓得到反饋電壓,并輸入到誤差比較器的反相端。誤差放大器放大基準電壓和反饋電壓之間的差值,其輸出直接驅動調整元件,通過改變調整元件的導通情況來控制穩壓器的輸出電壓。當反饋電壓小于基準電壓時,誤差放大器的輸出控制調整元件使其流過更大的電流,輸出電壓上升。反之亦然。

由上圖可知

Vout=(1+R3/R4)Vref (1)

2 帶隙基準電壓源的設計

2.1 帶隙基準的基本原理

產生基準的目的是建立一個與電源和工藝無關、具有確定溫度特性的直流電壓或電流。帶隙基準源的原理就是使負溫度系數和正溫度系數相互抵消來達到溫度補償的目的。其基本原理如圖2所示:其中Vbe具有負溫度系數,而VT具有正溫度系數,將Vbe和VT按一定比例系數求和,即可得到零溫度系數的基準輸出 Vref。

2.2 Brokaw結構的帶隙基準

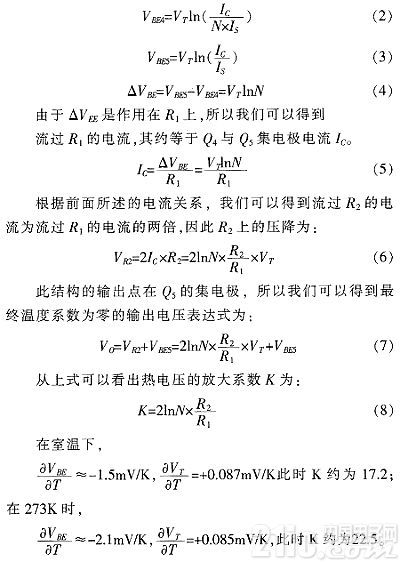

圖3為一個非常簡單的Brokaw結構帶隙基準電壓源。Q4與Q5的發射極面積之比為N比1。M2與M3構成電流鏡結構,并且它們的寬長比相同。這使得流過Q4與Q5集電極的電流相等,從而我們可以得到如下的關系:

從這個式子我們可以看出,BrokaW結構的帶隙基準相較于前面的結構最大的好處就是他將所需的R2的值減小了一半,并且直接在產生PTAT電流的支路上生成帶隙基準電壓。

這樣不僅使得電路結構簡化,同時減小了所需的靜態功耗。除此之外減小R2的值還能夠減小輸出電壓的噪聲。由于以上的優點,使得它成為了一種非常流行的結構。

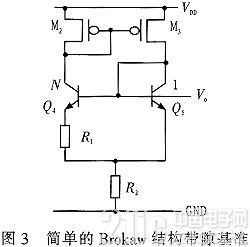

2.3 帶隙基準電壓的實現電路

實際的電路圖如圖4所示。帶隙基準電壓的整個實現電路由啟動電路和Brokaw結構帶隙基準組成。對于基準電壓源電路,啟動也是一個需要考慮的問題。當電源上電時,所有的晶體管均傳輸零電流,因為電路的兩個支路允許零電流,則晶體管可能處于無限期關斷狀態,這時就需要增加電路以擺脫這種狀態。啟動電路就是為了使電路在上電過程中脫離零電流點而穩定工作;另外,為了降低功耗,啟動電路在系統正常工作后應斷開。

啟動電路由M1~M2組成。電路上電時,A點電位迅速提高,使得Mg導通,從而拉低了B點電位,電路啟動,并且M1導通,M2和M7導通,將A點電位拉低,使得Mg截止,啟動電路關閉,電路穩定在正常工作點。

2. 4 電路仿真

電路基于1.0μm HVCMOS 40V/5V標準CMOS工藝模型,采用Cadence的Spectre進行仿真。仿真結果如下:

根據圖5,由溫度系數計算公式:

可算得在-20~125 ℃溫度范圍內溫度系數為17.4 ppm/℃,具有良好的溫度特性。

3 LDO緩沖器電路結構設計

3.1 運算放大器的設計

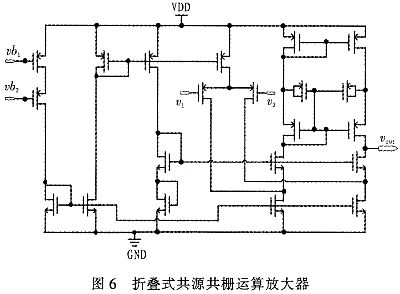

運算放大器根據其中級聯放大單元的數目,可以分成單級、兩級和多級運放3類。單級運放結構相對簡單,但增益較低;兩級運放能實現較高的性能,穩定性較好,得到了廣泛應用,但是速度、頻率特性方面一般比一級運放要差一些:3級以上的運放稱為多級運放,它們能實現更高的增益,但需要復雜的補償電路來保證運放的穩定性。全差分運放是指輸入和輸出都是差分信號的運放,它同普通的單端輸出運放相比有以下幾個優點:更低的噪聲;較大的輸出電壓擺幅;共模噪聲得到較好抑制;較好地抑制諧波失真的偶數階項等。所以高性能的運放多采用全差分形式。

一般常用的3種全差分運放有:直接套筒式共源共柵運放、折疊共源共柵運放和簡單兩級全差分運放。經過比較,為了減小直接套筒式共源共柵結構對運放輸出擺幅的限制,可以采用折疊共源共柵結構。折疊結構與直接套筒式結構相比,功耗要略大一些,增益也有所降低,但是它的輸出電壓擺幅遠大于前者,緩解了增益、電源電壓與輸出擺幅之間的矛盾。因此折疊共源共柵是一種廣泛應用的運放結構。

由于所設計的電路應用于電源芯片系統中,基于速度等方面綜合考慮,選擇的是一個折疊式共源共柵運算放大器,另外由于運放在基準中是用作負反饋,所以選用單端輸出的折疊運放。具體電路如下圖:

3.2 LDO緩沖器電路

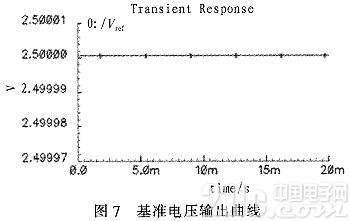

將以上所述的帶隙基準電路、運算放大器與電阻反饋網絡、LDO緩沖器相結合,即可得圖1所示典型LDO電路。根據輸出公式:

通過調節R3與R4比值即可獲得所需基準電壓2.5 V。由圖7易知基準輸出電壓精度高于5‰,滿足高精度要求。

4 結束語

LDO穩壓器對基準模塊具有較高的精度要求,從仿真結果可以看出在-20~125℃溫度范圍內,基準電壓溫度系數大約為17.4 ppm/℃,而且基準電壓輸出精度高于5‰,是一種低溫度系數高精度的CMOS帶隙基準電壓源。本文給出的帶隙基準電壓源的設計方案符合LDO穩壓器對高精度電壓的所需。

評論