DMA緩存解耦的一點見解

DMA(英文全稱:Direct Memory Access,中文:直接內存訪問)是一種不經過CPU而直接從內存存取數據的數據交換模式。在DMA模式下,CPU只須向DMA控制器下達指令,讓DMA控制器來處理數據的傳送,數據傳送完畢再把信息反饋給CPU,這樣就很大程度上減輕了CPU資源占有率,可以大大節省系統資源。

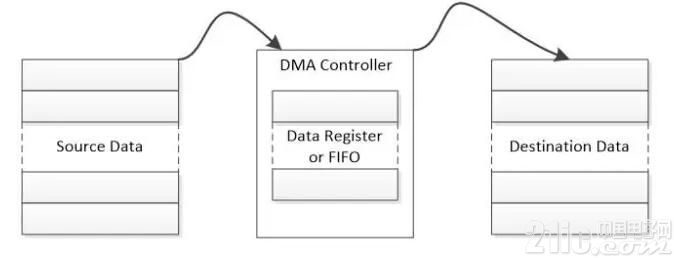

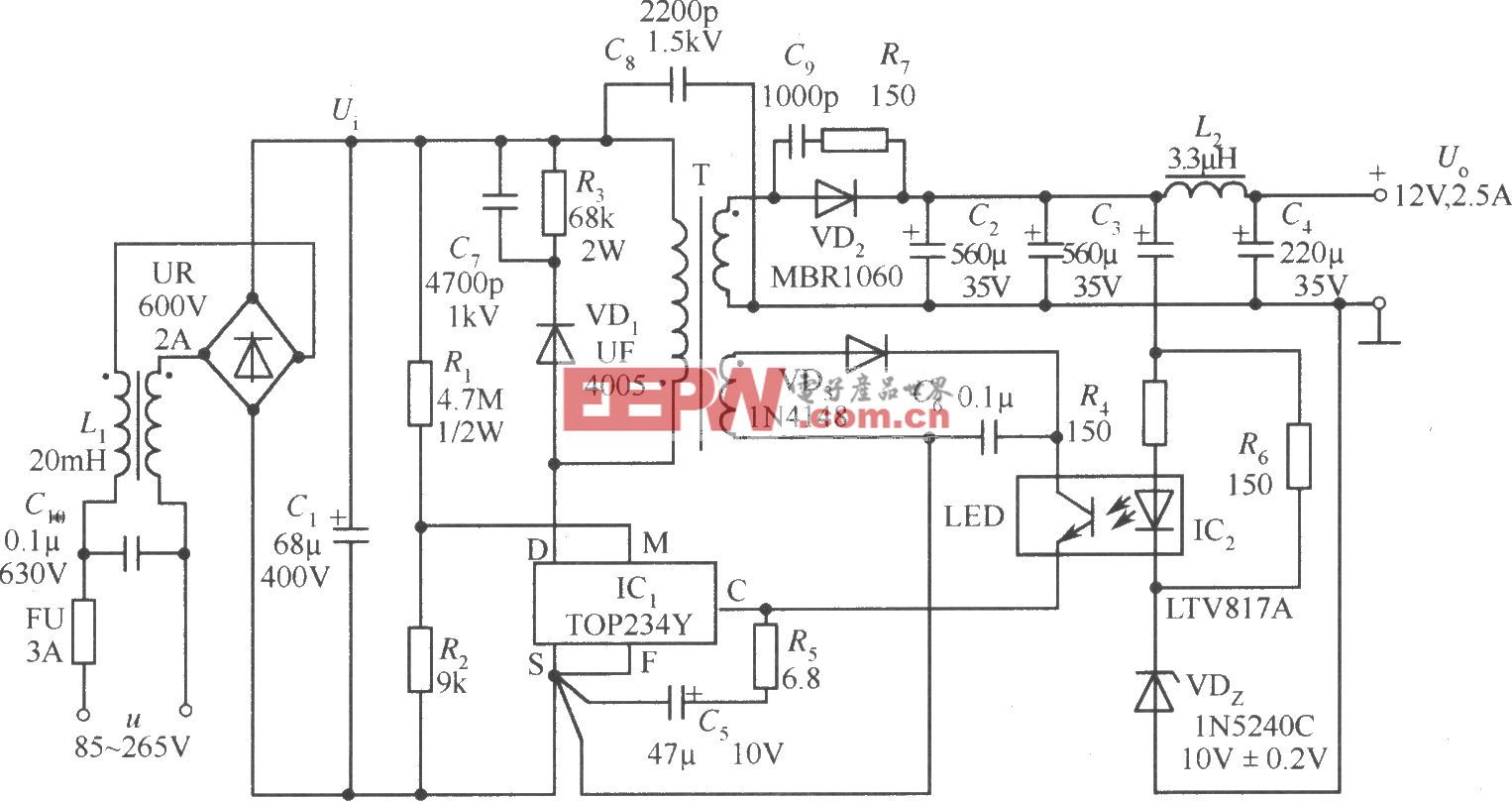

本文引用地址:http://www.j9360.com/article/201808/386005.htmDMA的傳輸模型結構見下圖:

Figure 1 DMA傳輸模型

從上圖可知,使用DMA從源地址傳輸數據到目的地址,數據都必須通過DMA控制器內部的寄存器或FIFO作緩存,而不是在源和目的地之間直接傳輸,這是因為源和目的所在設備的傳輸速度不一樣,接口也不一樣,要適應這些情況,數據在DMA控制器內的緩存是必不可少的,這樣可使在低速設備傳輸數據時,高速設備可被釋放并可被重新利用,這可看作是一種解耦,使低速設備和高速都能高效工作而不相互影響。

筆者在工作過程中,曾遇到一個有關DMA的issue,具體如下:在某個應用使用DMA進行大數據量傳輸過程中,經常出現數據傳輸異常,檢查系統的調試打印信息,發現DMA在階段性傳輸結束(會產生相應的中斷)后,重新啟動新階段的DMA傳輸(使用相同的通道)時,有時會出現申請的DMA通道還在活動狀態的情況,導致后面的數據傳輸無法正常啟動。按照一般的思路,驅動程序設置好參數,啟動DMA后,就可以去做其他工作,中斷的到來就意味著該次的DMA傳輸結束了,但矛盾的是有時發現傳輸結束的DMA通道卻不在空閑狀態,要說明的是,所有的DMA通道資源都是預先分配好的,不同驅動程序使用各自不同的通道,不會互相干擾。開始認為是驅動程序沒有設計好,出現競爭導致函數重入,但閱讀整個驅動源碼后,沒有發現這方面的問題。

重新分析整個DMA傳輸過程:數據從源設備到目標設備,中間是要經過DMA controller Data transfer register或FIFO這個中轉站暫存,而中斷產生的條件是只要源或目的地址更新到與通知地址相同,這樣當中斷發生時,最后的數據可能還在中轉站內,傳輸還在進行當中,由于最后的數據傳輸什么時候能真正結束,取決于目標器件以及當時的總線仲裁等情況,時間比較隨機,此時中斷服務函數重新啟動新階段傳輸前檢查該通道時就有可能查詢到DMA通道還處于忙狀態,這樣就會導致重新啟動DMA通道失敗而無法繼續進行數據傳輸。

初步認為issue的產生是由于真正的數據傳輸結束滯后于DMA中斷的產生(這個應該是硬件設計的一個bug),因此解決的方法就是加入等待,這可以通過多次重復查詢來實現。按照這個思路,修改驅動程序,重新進行測試,問題沒有復現,數據傳輸正常,這說明以上的分析推斷是正確的。

通過上面的例子可以看到,充分理解DMA設計的一些硬件基本機理,對我們在工作當中解決一些實際問題還是很有幫助的。

評論