使用SDNet開發創新型可編程網絡

Lagopus FPGA 可最大化電信和云服務的SDN/NFV 功能。

日本電報電話公司 (NTT) 是一家全球電信集團控股公司,負責制定管理策略和推動研發工作發展。 我們是 NTT 研發部的研究人員,正領導兩個針對軟件定義網絡 (SDN) 和網絡功能虛擬化 (NFV) 的創新型項目。針對其中的一個項目,我們已經開發出一個名為 Lagopus 的高性能軟件 SDN/OpenFlow交換機[1],我們認為這是迄今為止作為開源軟件發布的 OpenFlow 1.3 兼容交換機中的佼佼者。針對第二個項目,我們開發出一個具有軟件包處理感知功能的 40 Gbps FPGA 網絡接口卡 (NIC) ——Lagopus FPGA。

本文引用地址:http://www.j9360.com/article/201808/385497.htm早期階段采用賽靈思面向網絡的 SDNet 軟件定義規范環境,是我們能夠成功開發這些技術的關鍵所在。在本文中我們將介紹如何使用SDNet滿足我們的項目目標。

實現 SDN/NFV 卓越性能的 LAGOPUS FPGA

云服務供應商和網絡服務運營商正在轉向采用SDN,將其作為自動配置系統的關鍵支持技術。NFV 通過將網絡系統從專有硬件設備轉變為商用硬件系統,充分運用 PC 服務器、基于商用芯片的交換機和軟件工具,在幫助電信運營商降低資本支出和運營支出方面起著至關重要的作用。許多云服務提供商和電信運營商將為其新一代商用網絡部署 SDN 和 NFV。

NTT 集團是商業服務和研發領域的 SDN 和NFV 領跑者。在日本總務省的自助下,NTT 已經啟動一項與先進 SDN/NFV 相關的研究工作——O3 項目。Lagopus 是 O3 項目的主要可交付成果,其結合使用開放網絡基金會 (Open Networking FoundaTIon)的 OpenFlow 1.3 協議、商用英特爾 x86 服務器和商用 NIC, 可實現高性能軟件包處理和靈活的流程控制。 Lagopus 的主要優勢有: 能在商用服務器上實現超過 10Gbps 的高性能軟件包處理、高達百萬流量輸入的彈性網絡流控制、針對虛擬提供商邊緣 (vPE)/ 虛擬客戶端設備 (vCPE) / 虛擬演進分組核心網 (vEPC) 框架的可擴展流程分配器。

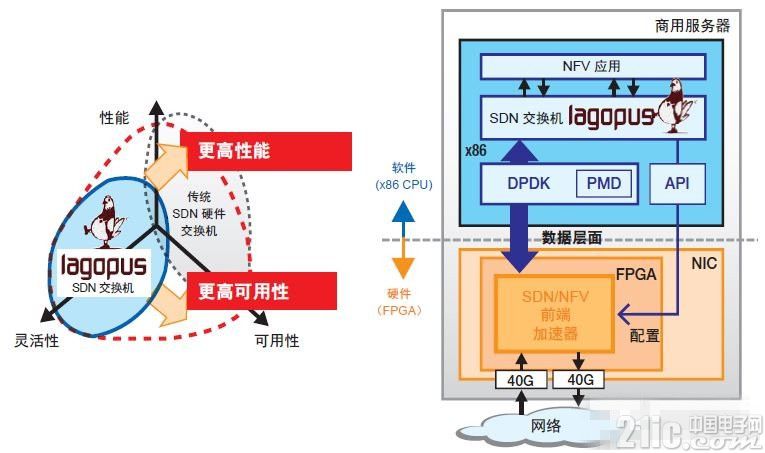

Lagopus FPGA 項目旨在通過在運行于商用服務器上的 FPGA 上靈活地對軟件加速和硬件加速功能進行分區,實現 40/100Gbps 的高性能包處理。圖 1顯示了 Lagopus FPGA 的概念和架構。這種靈活的架構能借助 FPGA 加速并以純軟件實現方式將 Lagopus交換機的 10Gpbs 線速提高到 40Gbps 線速。這一性能提升的代價僅僅是 x86 CPU 的功耗增大不到 10%。該架構還能極大地增強我們的網絡故障排除能力,這對真正虛擬化的網絡有實質性意義。

圖 1 — Lagopus FPGA 的概念和架構

目前, 我們正在使用先進的 FPGA 和設計工具聯合為 Lagopus 和網絡運營商的原始硬件知識產權(IP) 設計一種先進的軟件可編程數據層面,其目的不僅是獲得更高的系統性能,也是為降低功耗和成本。通過與賽靈思團隊合作,我們已經在基于賽靈思 Virtex?-7 All Programmable FPGA 的 80Gbps NIC演示板上成功集成了 Lagopus 和我們的 IP。2015 年2 月,我們在東京舉辦的 NTT2015 年研發論壇上首次演示了 Lagopus FPGA。同年 8 月,我們還在加州庫比蒂諾舉辦的 Hot Chips 27 大會上展示了我們的卓越成功。

我們使用 SDNet 開發環境創建 Lagopus FPGA系統。這種新穎的動態可重編程數據層面包處理工具鏈讓我們能夠在不影響性能的情況下,把數據包分類、編輯、搜索、負載均衡和統計測量等高強度數據層面運算轉交給 FPGA NIC 處理(均在10/40/100GbE 千兆位級以太網線速下實現),為 Lagopus和 NFV 應用提速。我們認為這是我們項目的最佳解決方案,可增強 SDN/NFV 技術的關鍵組成部分—— 分類 IP 的功能。該環境的快速可重配置包流水線功能讓我們能夠迅速方便地更新網絡協議和功能。

SDNet 環境涵蓋云計算數據中心和廣域網中豐富多樣的用例,從而擴大了 Lagopus FPGA 的使用潛力。對 NTT 而言,這種靈活、軟件定義硬件設計技術能實現差異化網絡業務的靈活部署。

SDNet 擴大了 Lagopus FPGA 的使用潛力:這種靈活的軟件定義硬件設計技術能實現差異化網絡業務的靈活部署。

SDNet 環境奠定設計基礎

隨著新興市場上 SDN/NFV 技術競爭日趨激烈,Lagopus FPGA 項目的一大設計挑戰是在緊湊的開發期內完成開發,以如期進行部署和推廣。我們從 2014 年 10 月開始設計 Lagopus FPGA 系統,三個月后,即在 2015 年 1 月完成首次集成。

鑒于該系統設計的復雜性,這是一項了不起的成就。圖 1 所示是 Lagopus FPGA 系統的頂層架構,它由包含軟件 FPGA IP 包在內的四個技術軟件層組成:(1) NFV 應用;(2) Lagopus 軟件交換機;(3)硬件抽象層,例如應用編程接口 (API)、英特爾數據面開發套件 (DPDK)、一組用于x86 快速包處理的庫和驅動程序;以及 (4) FPGA NIC IP 內核套件。該多重技術軟件層會增大追蹤問題根源的難度,如丟包和性能降低,削弱調試和立即隔離故障的能力。實際上這也是所有 SDN/NFV 架構的重大難題。為克服這些難題,我們采用了 SDNet 環境和賽靈思Vivado? Design Suite。

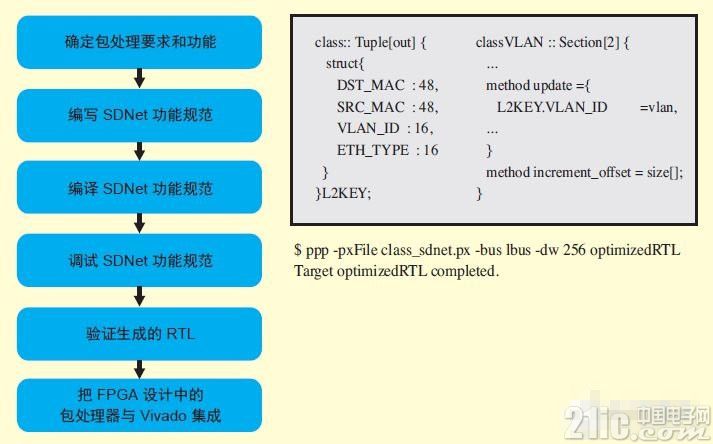

我們在啟動 Lagopus FPGA 的設計工作時,先確定我們對包處理功能的要求,并且制定出一個開發流程。圖 2 是這一開發流程的一般性介紹和SDNet規范的示例代碼段。我們決定創建一個完美匹配的濾波器。該過濾器采用來自虛擬 LAN 的關鍵信息。借助這個過濾器,我們可以把硬件分類功能卸載到FPGA NIC,在 x86 上為 Lagopus 的軟件數據層面提速。我們可使用 Lagopus 和 SDN 控制器之間的OpenFlow 協議注入流程項,進而通過 DPDK 流程指示器 API 配置濾波器項。

圖 2 — SDNet 環境的設計流程

為實現這一策略,我們創建了相應的 SDNet 功能描述,如圖 2 的代碼段所示。我們隨后把該代碼輸入 SDNet 編譯器,設定總線類型、總線寬度和生成的 RTL 類型等選項。編譯在數秒鐘內完成。SDNet功能描述的實際代碼規模大約為 250 行代碼。相比之下,等效的 RTL 需要由數萬行代碼構成。考慮到我們的工作日程緊張,我們十分欣賞 SDNet 規范的簡潔性。受我們開發時間的約束,要在 RTL 中重新設計并驗證這一復雜模塊是無法做到的。

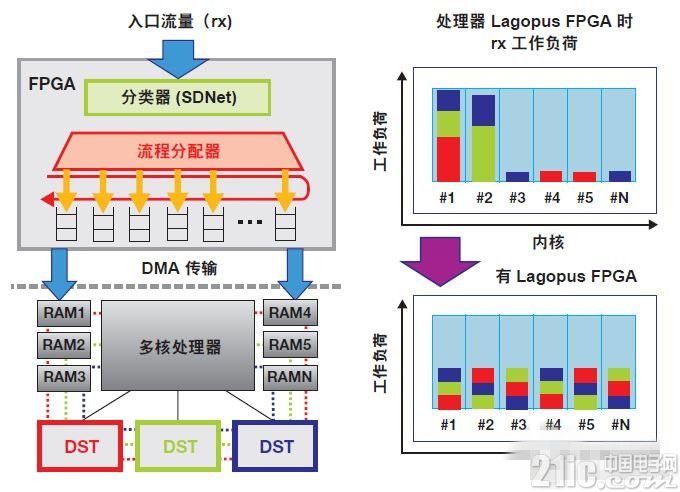

下一步我們使用工具命令語言 (Tcl) 外殼程序,將生成的 RTL 與 Vivado Design Suite 上的其他外設IP 集成在一起。圖 3 所示為集成式 SDNet 分類器和我們定制的流程分配器。我們的目標編程器件是賽靈思 Virtex-7 XC7VX690T FPGA。

圖 3 — FPGA 流程分類與分配

借助 Lagopus FPGA,我們僅以 x86 功耗上升不足10% 為代價,便實現了 40Gbps 線速軟件包處理能力。

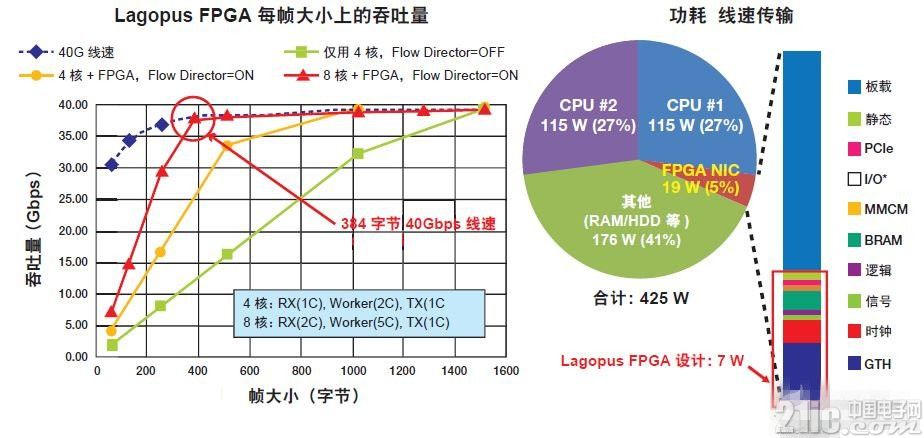

由于分類后的包流(指向 32 個接收 [rx]DMA隊列)通過在 x86 多核 CPU 上工作的 Lagopus 的軟件數據層面能夠得到有效分配,這種集成 FPGA 設計讓系統不僅能減少 Lagopus 的 OpenFlow 工作線程占用的 CPU 周期,而且還可平衡每個內核的工作負荷(圖 3)。因此,, 我們使用 Lagopus FPGA 實現了更高性能—— 達到 40Gpbs 線速軟件包處理能力,而且付出的代價僅僅是 x86 CPU 的功耗增大不到 10%(如圖 4 所示)。

圖 4 — 性能與功耗關系圖

SDNet 環境與 Vivado Design Suite 結合運用,有助于我們項目的啟動,讓我們能夠最大程度地豐富Lagopus FPGA 系統的特性集,優化性能并降低功耗。NTT 研發部在 SDN/NFV 領域的領先地位,加上我們對賽靈思 SDNet 開發環境的運用,讓我們為電信和云基礎架構將帶來革命性變化。為此,我們將繼續運用軟定義、可重編程的 SDNet 負載模塊來優化我們的設計方法。包括 API 在內的 SDNet 規范的不斷快速修改在我們設計未來平臺時能為我們提供更多益處。

『本文轉載自網絡,版權歸原作者所有,如有侵權請聯系刪除』

評論