并行總線與串行總線

雖然隨著技術的發展,現代的數字芯片已經集成了越來越多的功能,但是對于稍微復雜一點的系統來說,很多時候單獨一個芯片很難完成所有的工作,這就需要和其它芯片配合起來工作。比如我們現在的CPU的處理能力越來越強,很多CPU內部甚至集成了顯示處理的功能,但是仍然需要配合外部的內存芯片來存儲臨時的數據、需要配合橋接芯片擴展硬盤、USB等外圍接口;現代的FPGA內部也可以集成CPU、DSP、RAM、高速收發器等,但有些場合可能還需要配合專用的DSP來進一步提高浮點處理效率、配合額外的內存芯片來擴展存儲空間、配合專用的物理層芯片來擴展網口、USB等,或者需要多片FPGA互連來提高處理能力。所以的這一切,都需要用到相應的總線來實現多個數字芯片間的互連。如果我們把各個功能芯片想象成人體的各個功能器官的話,總線就是血脈和經絡,通過這些路徑,各個功能模塊間才能進行有效的數據交換和協同工作。

本文引用地址:http://www.j9360.com/article/201807/383770.htm我們經常使用到的總線根據數據傳輸方式的不同,可以分為并行總線和串行總線。

并行總線:

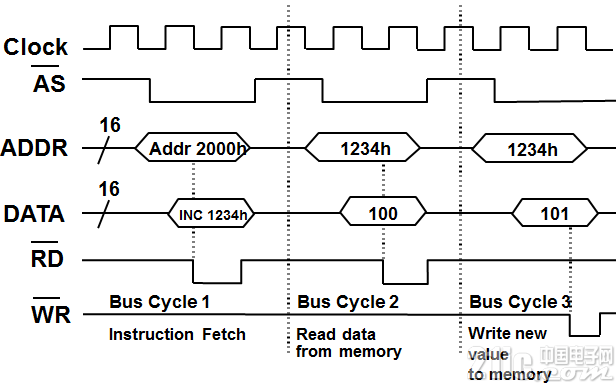

并行總線是數字電路里最早也是最普遍采用的總線結構。在這種總線上,要傳輸的數據線、地址線、控制線等都是并行傳輸,比如要傳輸8位的數據寬度,就需要8根數據信號線同時傳輸,如果要傳輸32位的數據寬度就需要32根數據信號線同時傳輸。除了數據線以外,如果要尋址比較大的地址空間,還需要很多根地址線的組合來代表不同的地址空間。下圖是一個典型的微處理器的并行總線的工作時序,其中包含了1根時鐘線、16根數據線、16根地址線以及一些讀寫控制信號。

很多經典的處理器都采用了并行的總線架構。比如大家熟知的51單片機就采用了8根并行數據線和16根地址線;CPU的鼻祖,Intel 公司的8086微處理器最初推出時具有16根并行數據線和16根地址線;現在很多嵌入式系統中廣泛使用的ARM處理器則大部分使用32根數據線以及若干根地址線。

并行總線的最大好處是總線的邏輯時序比較簡單,電路實現起來比較容易,但是缺點也是非常明顯的。比如并行總線的信號線數量非常多,會占用大量的管腳和布線空間,因此芯片和PCB板的尺寸很難實現小型化,特別是如果要用電纜進行遠距離傳輸時,由于信號線的數量非常多,使得電纜變得非常昂貴和笨重。

采用并行總線的另外一個問題在于總線的吞吐量很難持續提升。對于并行總線來說,其總線吞吐量=數據線位數×數據速率。我們可以通過提升數據線的位數來提高總線吞吐量,也可以通過提升數據速率來提高總線吞吐量。以個人計算機里曾經非常流行的PCI總線為例,其最早推出時總線是32位的數據線,工作時鐘頻率是33MHz,其總線吞吐量=32bit×33MHz;后來為了提升其總線吞吐量推出的PCI-X總線,把總線寬度擴展到64位,工作時鐘頻率最高提升到133MHz,其總線吞吐量=64bit×133MHz。下圖是PCI插槽和PCI-X插槽的一個對比,可以看到PCI-X由于使用了更多的數據線,其插槽更長(來源:網絡圖片)。

但是隨著人們對于總線吞吐量的要求的不斷提高,這種提升總線帶寬的方式遇到了瓶頸。首先由于芯片尺寸和布線空間的限制,64位數據寬度已經幾乎是極限了。另外一方面,這64根數據線是共用一個采樣時鐘,為了保證所有的信號都滿足其建立保持時間的要求,在PCB上布線、換層、拐彎時需要保證精確等長。而總線工作速率越高,對于各條線的等長要求就越高,對于這么多根信號要實現等長的布線是很難做到的。

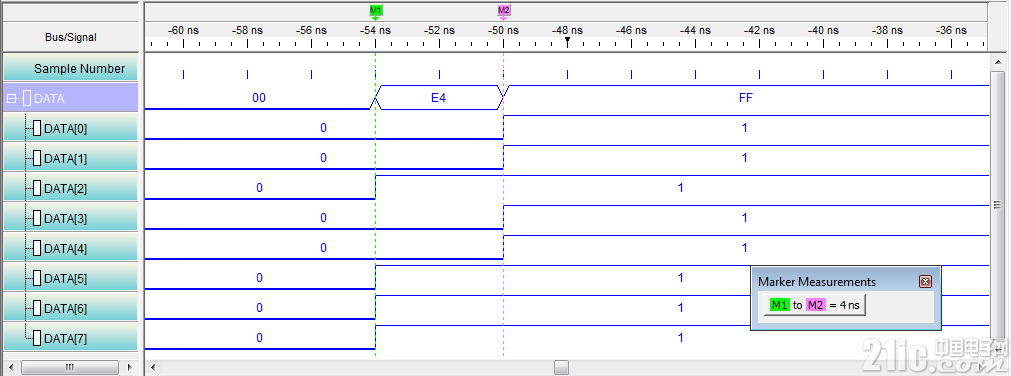

下圖是用邏輯分析儀采集到的一個實際的8位總線的工作時序,我們可以看到在數據從0x00跳變到0xFF狀態過程中,這8根線實際并不是精確一起跳變的。

對于并行總線來說,更致命的是這種總線上通常掛有多個設備,且讀寫共用,各種信號分叉造成的反射問題使得信號質量進一步惡化。

串行總線:

為了解決并行總線占用尺寸過大且對布線等長要求過于苛刻的問題,隨著芯片技術的發展和速度的提升,越來越多的數字接口開始采用串行總線。所謂串行總線,就是并行的數據在總線上不再是并行地傳輸,而是時分復用在一根或幾根線上傳輸。比如在并行總線上傳輸1個Byte的數據寬度需要8根線,而如果把這8根線上的信號時分復用在一根線上就可以大大減少需要的走線數量,同時也不需要再考慮8根線之間的等長關系。

采用串行總線以后,就單根線來說,由于上面要傳輸原來多根線傳輸的數據,所以其工作速率一般要比相應的并行總線高很多。比如以前計算機上的擴展槽上廣泛使用的PCI總線采用并行32位的數據線,每根數據線上的數據傳輸速率是33Mbit/s,演變到PCI-E(PCI-Express)的串行版本后每根線上的數據速率至少是2.5Gbit/s(PCI-E 1代標準),現在PCI-E的數據速率已經達到了5Gbit/s(PCI-E 2代標準)或8Gbit/s(PCI-E 3代標準)。采用串行總線的另一個好處是在提高數據傳輸速率的同時節省了布線空間,同時芯片的功耗也降低了,所以在現代的電子設備中,當需要進行高速數據傳輸時,使用串行總線的越來越多。

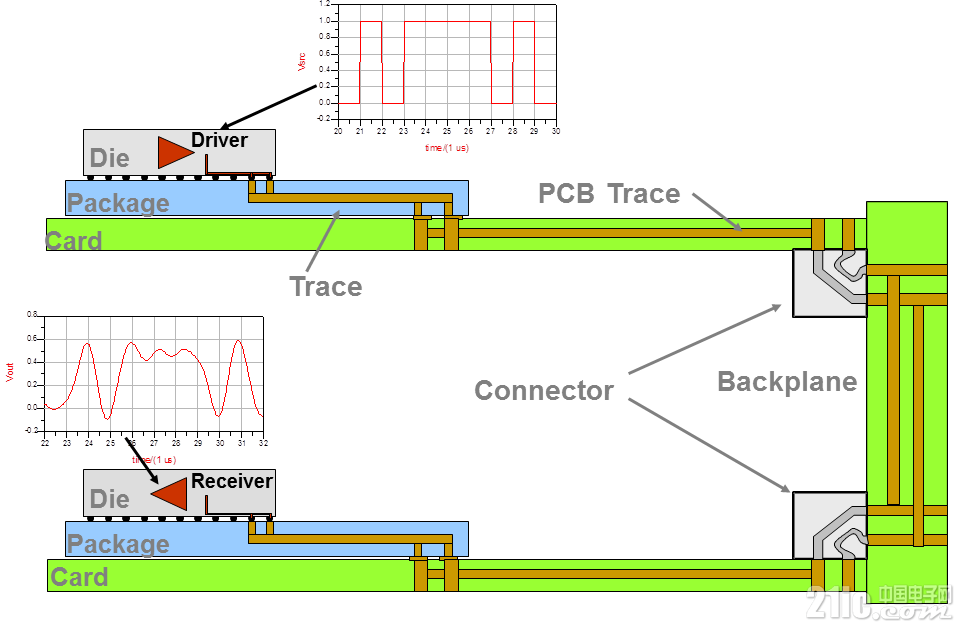

數據速率提高以后,對于阻抗匹配、線路損耗和抖動的要求就更高,稍不注意就很容易產生信號質量的問題。下圖是一個典型的1Gbps的信號從發送端經過芯片封裝、PCB板、連接器、背板傳輸到接收端的信號路徑,從中我們可以看到在發送端的接近理想的0、1跳變的數字信號到達接收端后由于高頻損耗、反射等的影響信號波形已經變得非常惡劣,所以串行總線的設計對于數字電路的工程師來說是個很大挑戰。

使用串行總線的設備的體積、功耗和數據傳輸速度都比使用并行接口的設備更有優勢,因此得到了廣泛的應用。比如以前在計算機上廣泛使用的連接打印機的DB25的并口已經被USB和網口取代,以前連接硬盤的40pin的PATA接口已經被串行的SATA接口取代,以前計算機上的PCI擴展槽已經被PCI-Express取代。但是如前所述,采用串行總線以后信號的數據速率一般都會有幾倍甚至幾百倍的提升,對于電路的設計和測試都提出了很高的要求,因此需要設計和測試工程師掌握大量的高速設計的相關知識和技能。

評論