RISC-V能否繼紅五月后再度掀起熱浪?

6月24日-27日,全球芯片設計及半導體知識產權(IP)領域內最負盛名的“設計自動化大會(DAC)”將在舊金山舉行,每年的DAC都吸引了來自全球的EDA工具廠商、IP廠商和芯片設計師參加。作為該項活動的第55屆,組委會公布本屆大會為一些新的技術擴展了展覽面積并新增了研討話題,包括人工智能與機器學習、汽車和物聯網等等。但是值得大家關注的還有一個新的領域:RISC-V開源硬件。

本文引用地址:http://www.j9360.com/article/201806/382443.htm

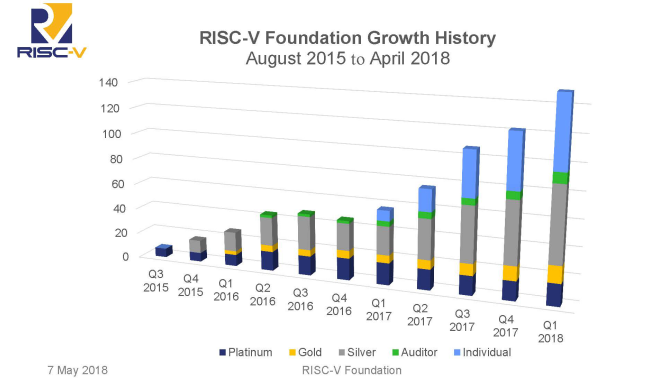

谷歌、高通、三星、華為、特斯拉……隨著越來越多的行業巨頭加入RISC-V基金會(RISC-V Foundation),RISC-V架構的行業認可度快速提升,基于該架構的新興產品和解決方案開始在市場中不斷涌現。而RISC-V社群在第55屆DAC大會上的表現將會再次引起行業的高度關注,此次RISC-V基金會將與其成員公司 Imperas Software、Microsemi、SiFive、Syntacore, UltraSoC及Western Digital 在2638號展位上向芯片設計行業介紹其最新的技術與生態建設進展。

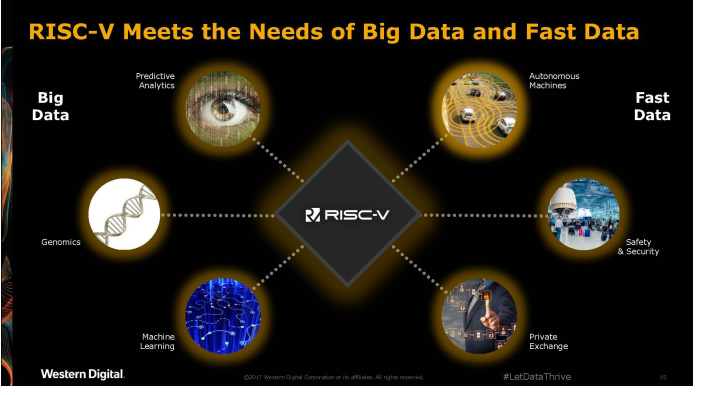

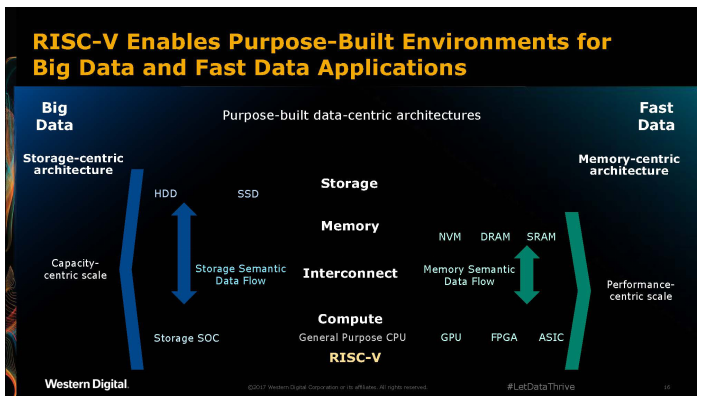

北京華興萬邦管理咨詢有限公司首席分析師劉朝暉表示:“RISC-V生態在第55屆DAC定會引起廣泛的關注,這是因為RISC-V開源硬件的價值已經不再僅僅是節省NRE和授權費用了,一些領先的芯片設計公司開始利用RISC-V ISA指令架構定義和實現自己的芯片特性,已在市場中形成獨有的差異化優勢。這是Microsemi和Western Digital等公司已經用實際產品證明過的一條創新之道。”

在此次DAC大會前,RISC-V社群中的許多成員已經在不斷為行業帶來新的亮點和熱點。UltraSoC和Imperas于6月21日聯合宣布:雙方將達成一項廣泛的合作,為多核系統級芯片(SoC)開發人員提供結合了嵌入式分析技術和虛擬平臺技術的強大組合。根據協議條款,UltraSoC將把Imperas開發環境的關鍵元素納入其提供的工具中,從而為設計人員提供一個統一的系統級預處理和后處理芯片開發流程,顯著地縮減了產品開發時間和整體開發成本。

通過結合半導體知識產權(IP)和相關軟件,UltraSoC提供行業領先的獨立片上監測、分析和調試技術。Imperas首創的虛擬平臺方法使得軟件開發人員能盡早啟動SoC項目的相關開發工作,并提供一系列調試工具為開發人員提供系統全局視角。將兩家公司提供的技術結合起來可創造一個強大的、帶有一個通用軟件調試環境的集成化設計流程,為項目發展提供平穩過度。

北京華興萬邦管理咨詢有限公司高級分析師陳皓表示:“就在剛剛過去的這個五月,RISC-V生態在全球多地迎來了一次集中式的爆發,多項行業活動在世界不同地方如火如荼開展,并得到了行業內外的廣泛關注,蓬勃發展前景一覽無余。無論RISC-V生態最終走向何方,2018年的5月是芯片設計領域內值得記住的一個月份。”

讓我們先將目光聚焦至西班牙巴塞羅那。5月7-10日,第8屆RISC-V研討會在巴塞羅那舉行,谷歌、IBM、英偉達、恩智浦、西部數據、UltraSoC、SiFive、Microsemi等一眾RISC-V領域的翹楚企業參加會議。該會議吸引了數百名與會者,從大企業、初創企業到學術機構和普通愛好者,皆踴躍參加。

UltraSoC作為目前唯一一家提供RISC-V跟蹤解決方案的公司以及本次活動的贊助商,其首席執行官Rupert Baines攜首席技術官、銷售和工程代表等6名成員參與活動。會議期間,UltraSoC首席技術官Gajinder Panesar發表了主題演講,對UltraSoC領導的RISC-V規范調試工作組(Debug Working Group)及UltraSoC的跟蹤解決方案進行了介紹。此外,UltraSoC還在其展位上演示了基于SiFive和Andes內核的運行控制和指令跟蹤案例,吸引大量觀眾駐足交流和觀看。

UltraSoC的RISC-V處理器跟蹤解決方案從今年2月開始已經全面供貨,這是業界首款商用RISC-V處理器跟蹤IP產品,也是RISC-V生態系統中關鍵的推動性技術。除了作為一種獨立的IP模塊來集成至UltraSoC的SoC架構中,UltraSoC還提供各種不同的打包選擇項來使RISC-V設計人員快速上手并實現運轉,而無須將UltraSoC用于其他功能。

處理器跟蹤功能支持對程序的行為進行詳細的、逐條指令式的查看,它于系統開發人員而言是一項關鍵需求。UltraSoC的RISC-V跟蹤編碼器同時支持32位和64位RISC-V設計,IP模塊可以順利地與UltraSoC產品組合的其他部分進行集成;其所有產品均采用支持開放架構和業界標準架構方式,在SoC的核心部分設置自分析功能。

看過巴塞羅那的行業盛景,讓我們再將視線轉移至中國上海。5月15日,世界領先的商業RISC-V處理器IP提供商SiFive在上海舉辦首屆(2018)技術研討會,來自SiFive、西部數據、Microsemi、燦芯半導體、UltraSoC及中科院計算所在內的專家學者、行業精英齊聚一堂,共同對RISC-V技術發展趨勢、生態系統、應用及原型芯片的快速定制展開深入探討。該研討會的舉辦,正值全球半導體產業聯盟董事會在中國舉辦,UltraSoC首席執行官Rupert Baines及其中國團隊參加了該次研討會。

UltraSoC作為RISC-V生態系統的積極參與者,早在去年9月就與SiFive形成了良好的合作關系。UltraSoC的嵌入式分析半導體知識產權(IP)通過SiFive DesignShare生態系統對外提供,該生態系統為任何公司、發明人和創客都提供了駕馭客制化芯片動力的能力。UltraSoC的調試與追蹤功能可以支持SiFive Freedom平臺的用戶去廣泛對接其設計中所用到的各種工具與接口。

“UltraSoC致力于提升新的芯片設計的數量,而我們與SiFive在DesignShare生態中的合作是這項工作的自然延伸。”UltraSoC首席執行官Rupert Baines表示。“我們專注于推動半導體行業新興力量的加速形成,所采用的方法既包括在RISC-V基金會中發揮會員作用,也包括與SiFive這樣的單個合作伙伴關系。通過DesignShare模式來提供UltraSoC的IP,將使各地的芯片開發商都能夠盡享開源硬件的優點,并為市場帶來全新的、創新的設計。”

領先廠商兩岸三市造勢,64位RISC-V立志高端。在SiFive舉辦技術研討會的同期,另一家為RISC-V生態系統做出積極貢獻的廠商晶心科技(Andes Technology)也于5月3日、15日、17日分別在新竹、深圳、上海三地舉辦第十三屆晶心嵌入式技術論壇。該論壇以“萬物聯網劃世代?智能生活躍云端”為主題,聚焦于晶心科技新一代微處理器指令集架構AndeStar V5,以及AI結合IoT而成的AIoT領域重點應用。UltraSoC作為晶心科技的合作伙伴,其首席執行官Rupert Baines也受邀參與了本次活動。

UltraSoC先進的嵌入式分析技術目前已獲晶心科技采用,來支持其AndesCore系列RISC-V處理器。利用UltraSoC包括業界唯一商用RISC-V處理器跟蹤解決方案在內的獨一無二的IP產品系列,晶心科技可以實現其復雜應用嵌入式產品的開發加速和調試增強,這些應用包括人工智能(AI)、計算機視覺、網絡控制器和存儲等。

晶心科技的內核都基于高性能的AndeStar V5 32位及64位架構,與UltraSoC的合作伙伴關系將使客戶在使用Andes V5 N25及NX25處理器時,可以選擇并集成先進的嵌入式分析功能。使用晶心科技高性能32位及64位處理器內核的客戶,在RISC-V處理器追蹤功能之外,還能夠利用UltraSoC的SoC分析與調試IP,這些功能結合在一起就給SoC設計師帶來了全面的可視性,不僅可以觀察內核的性能,而且還可以觀察整個系統的運行。

除了SiFive和晶心科技,UltraSoC的解決方案還獲得了Codasip、Microsemi、Roa Logic、Syntacore和Esperanto等主要RISC-V處理器供應商和多家工具供應商的支持和采用。UltraSoC正在攜手這些廠商共同推動RISC-V的生態向更廣闊的空間發展。

北京華興萬邦管理咨詢有限公司高級分析師胡霞表示:“今年年初以來,我們一直在對國內外媒體上的RISC-V相關話題進行監測,結果是國內媒體對RISC-V的報道數量相比2017年有巨大的增加。盡管產業化的道路還很漫長,但是國內芯片設計企業的確可以考慮利用指令架構的創新來走出新路。”

也許,加州大學伯克利分校最初開發RISC-V處理器架構時并不會想到該架構會發展得如此迅速甚至火爆,然而事實就在眼前,隨著一場“RISC-V的紅色五月盛宴”以及在第55屆DAC上RISC-V生態的宏大亮相,產業發展的新機遇正在形成。正如UltraSoC的首席執行官Rupert Baines所言:“RISC-V,2018大勢所向。”

作者:北京華興萬邦管理咨詢有限公司首席分析師劉朝暉、高級分析師陳皓、高級分析師胡霞

評論