完全卷積神經網絡IP——DPU “聽濤”系列 SoC

作者/深鑒科技ASIC副總裁 陳忠民

本文引用地址:http://www.j9360.com/article/201805/379458.htm算法、數據和算力并稱為新AI時代三大驅動力。如何在追求更好性能的同時實現低功耗、低延遲和低成本,逐漸成為擺在所有AI從業者面前的艱巨挑戰之一。

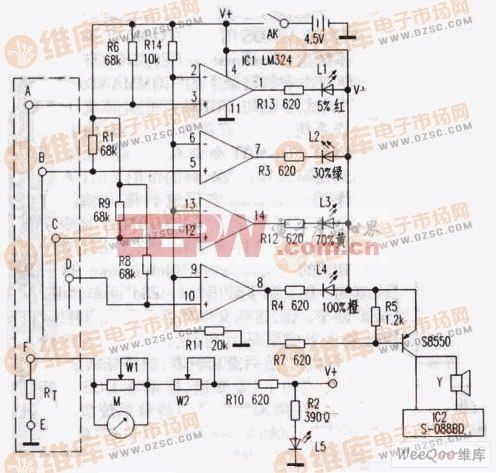

很多硬件平臺都展示了自身所具備的強大算力,然而當用戶在真正運行一個應用時,卻發現在讀取數據時會產生比較明顯的卡頓現象。這表明,即便用戶在掌握大量數據的前提下,依然不能將AI運算單元填滿,從而導致計算硬件的計算效力低下。以谷歌第一代TPU為例,其平均硬件乘法陣列使用率只有28%,這意味著72%的硬件在大部分時間內是沒有任何事情可以做的。 另外,如果將完成16位整數加法能量消耗定義為1,那么將32比特的數據從DDR內存傳輸到芯片中,就將花費1萬倍的能量消耗。因此,過大的訪問帶寬增加了數據的復用性,導致AI芯片功耗高居不下。

而要提升計算效率、降低功耗,總結起來有三條路徑:首先,優化計算引擎,增加計算并行度;其次,優化訪存系統;第三,利用神經網絡稀疏性,實現軟硬件協同設計。這樣的產品規劃路線能走得通的一個關鍵因素,就在于用戶在未來的ASIC芯片和之前的FPGA模組上使用的是同樣的編程和軟件開發環境,能實現在應用上的無縫切換。

DPU “聽濤”系列 SoC

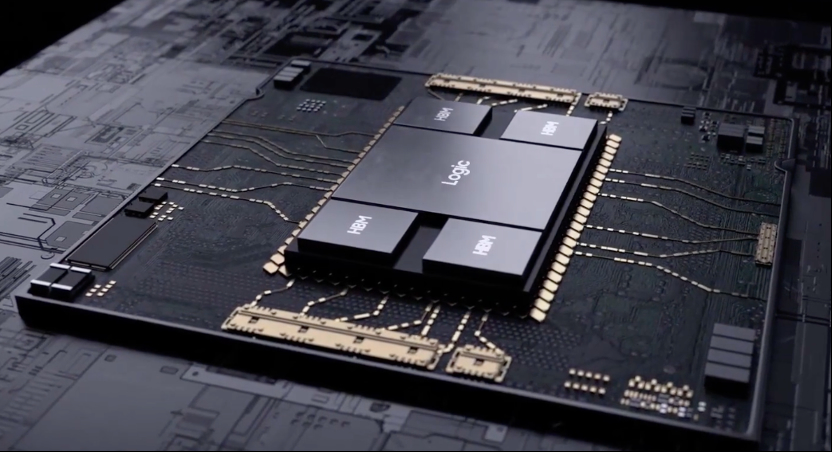

深鑒科技正式發布基于自主研發的人工智能處理器核心DPU 的“聽濤”系列 SoC。該DPU屬于完全卷積神經網絡IP,支持傳統的1X1和3X3卷積層,能夠實現高效的目標識別和加速。在該架構基礎之上,深鑒科技做出了第一代5X5 FPGA產品,并在攝像頭市場實現了批量出貨。

DPU計算核心采用全流水設計結構設計,內部集成了大量的卷積運算器、加法器、非線性Pulling/ReLu之類的運算算子,在確保每一個運算單元都能夠被充分的調動起來的前提下,可同時支持不同動態精度的量化方法。像VGG16比較重的應用中,深鑒科技DPU的運算器利用率可以達到85%,對主流算法可以達到50%以上,功耗方面則低出競爭對手一個數量級。

相比Zynq 7020每瓦230 GOPS的算力、ZU9 2.7 TOPS的峰值算力,將于年中交付的“聽濤”SoC產品的預期功耗約為3 W,峰值算力4 TOPS,考慮到網絡壓縮部分,這個數字應該再擴大5~10倍。

評論