采用FPGA的以太網應用

作者/Ted Marena 美高森美公司SoC/FPGA產品總監

本文引用地址:http://www.j9360.com/article/201802/375421.htm以太網連接的日益普及和不斷增加的降成本壓力,是不可阻擋的兩大網絡趨勢。由于網絡和物聯網(IoT)不斷擴張,使得以太網端口的性能持續增加,并且應用于更廣泛的各種產品。網絡運營商面臨兩個巨大壓力,首先是要大幅降低資本支出(CAPEX/OPEX),同時要提供更快性能以支持消費者應用,如4 K視頻和無處不在的云連接。為了幫助架構師滿足這些市場需求,我們需要重新定義中端密度FPGA特性:低成本、低功耗,并且可以滿足通訊應用中以太網互聯的性能要求。

這些新市場向設計以太網通信設備的供應商提出了重大的挑戰。以太網的重大優勢在于1 Gbps至10 Gbps線速率,而人們正在設計豐富的接入和網關設備,從而在網絡邊緣提供額外的計算能力。為了以更低成本提供這些解決方案,我們需要從整體系統的角度來考慮這個應用。為了降低成本,可以采用功耗更低的解決方案,從而取消風扇或散熱片;或者不采用專用橋接產品,轉而在SFP外形尺寸中實施這種功能,從而縮減PCB規格和總體外形尺寸。這些解決方案需要具備合適的以太網連接性、更低功耗,以及采用成本優化的小封裝產品。現在,系統架構師擁有的解決方案能夠幫助他們在更小外形尺寸中提供更節能的以太網接口,所有這些都需要成本優化、靈活的FPGA。

1低成本要求奸商通信模塊占用空間

更低綜合成本的需求正引領開發人員大幅減少通信產品占用的空間,而FPGA通常是以太網應用的關鍵設計部件。今天,市場上出現了一種優化的中密度FPGA產品,可以提供合適的接口性能,并保持了最低功耗和最小尺寸。許多現有的低密度FPGA擁有小封裝,但接口性能不足(如不支持10 Gbps收發器),而大多數中密度FPGA的封裝尺寸又偏大,且功耗頗高。而新的需求是更小物理封裝中必須包含的關鍵特征包括10 Gbps收發器、大量嵌入式存儲器、眾多3.3 V I/O管腳,以及支持更新的存儲器標準。具有這些能力、擁有功耗優化架構的中階密度FPGA是即將到來的小型化解決方案的關鍵實現因素。

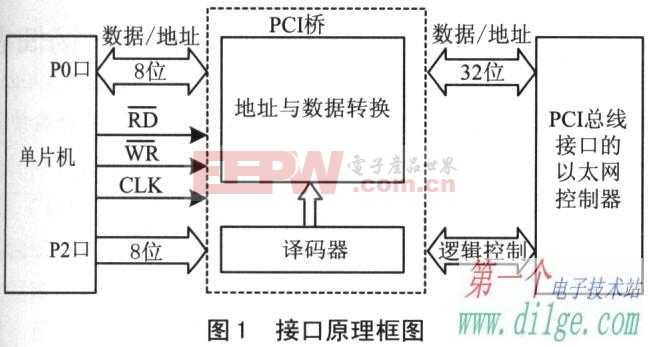

圖1 小尺寸、低功耗、中階密度且支持10 Gbps以太網的FPGA

顯然光模塊或SFP類模塊有明確的小尺寸要求。許多以太網通信產品都有SFP或類似的槽位以提供收發器接口,通常以1 Gbps至10 Gbps速率運行。能夠在這些模塊中實施各種功能的產品具有系統級的靈活性,并將提供更低成本的解決方案。例如,支持10 Gbps以太網的網關不一定需要同步網絡定時,如SyncE或IEEE 1588。如果這類產品提供了SFP槽位,則可以使用特別設計并且支持SyncE的SFP來實現同步網絡定時,此舉使得整個網關產品設計時不再需要考慮SyncE功能,為不需要此功能的客戶降低了總成本,而需要SyncE網絡定時的用戶,只需簡單地插入支持SyncE功能的SFP模塊。雖然許多小封裝的低端FPGA可滿足這種應用的尺寸要求,但是,低端FPGA無法提供必要的邏輯資源和性能。而典型的中階FPGA支持10 Gbps以太網,但其高功耗和大尺寸卻又不適用于SFP模塊。PolarFire FPGA系列在僅11 mm寬的封裝中可提供兩種密度。這些器件針對成本和低功耗進行了優化,并且擁有高達10 Gbps以太網接口能力。

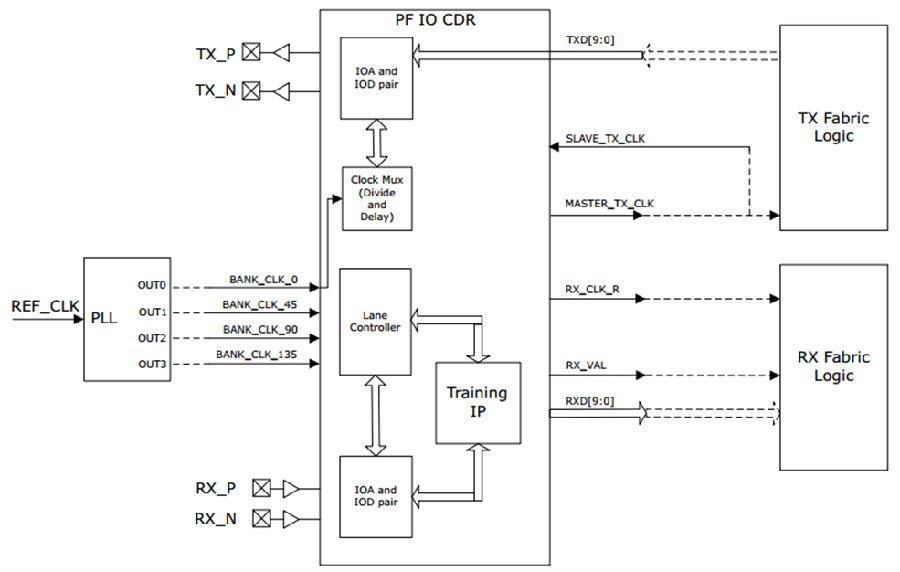

高效能千兆以太網接口正推動系統架構發生變化。許多通信產品開發商正在日益增多連接中采用的千兆位以太網。這些連接不再僅僅用于傳輸數據負載,而是普遍用于傳輸控制、管理、狀態信號等。通常這些增長的千兆以太網接口將通過匯聚或復用成10 G以太網。傳統的中階FPGA可以支持這些1 Gbps至10 Gbps的速率,但需要串行收發器來實施1 G SGMII接口和10 G10 BASE-R或10 BASE-KR。而更理想的器件是可以用通用的I/O管腳來支持SGMII,如圖2所示。

圖2 在GPIO中實施SGMII的FPGA

傳統中階FPGA并不擁有這種特征,因此,必須使用串行收發器。除非使用非常昂貴的更高密度FPGA,否則這些串行收發器接口通常數量較少,而顯得尤其寶貴。設計人員通常并不需要非常多的FPGA邏輯資源,但是,由于他們需要額外的串行收發器,因此被迫選擇這類昂貴大器件。此外,這些大器件要求采用更大的封裝尺寸。這些現有解決方案增加了功耗和成本,與OPEX需求相悖。

2新型PolarFire FPGA提供功耗優化的中階密度

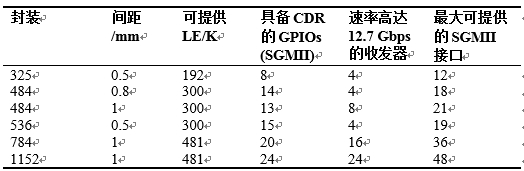

新型PolarFire FPGA提供功耗優化的中階密度,應對眾多GigE和10 GigE連接的要求。該系列從100 K LE至500 K LE,具有8至24個12.7 Gbps收發器,支持1 Gbps至10Gbps以太網。PolarFire FPGA與眾不同的優點是在1.25 Gbps的高速LVDS I/O內集成了時鐘和數據恢復(CDR)電路,使器件能夠在一些特定的GPIO引腳上支持SGMII接口。現在,在千兆和萬兆以太網混合應用中使用Polarfire,可以靈活地選擇使用收發器或具有CDR的GPIO引腳來支持這些接口,如表1所示。

表1 GPIO中帶有CDR的PolarFire FPGA系列

這樣工程師就不必再為了增加串行收發器而選擇封裝更大的器件。PolarFire FPGA使他們可以選擇更小的封裝。這些GPIO CDR的功耗也比收發器低,降低了多個GigE連接應用的總功耗,有利于降低CAPEX/OPEX。

在通信應用中降低功耗的需求日益迫切。在功耗預算中,FPGA通常占了不小的比重。FPGA功耗的兩個決定因素是靜態功耗和串行收發器功耗。PolarFire FPGA在這兩方面都非常出色。在SRAM FPGA中,靜態功耗達總功耗的一半。這是因為這些器件已經使用很高級的生產工藝,晶體管尺寸的變小也使得靜態功耗成為總功耗的主要組成。相反,PolarFire FPGA使用的是FLASH工藝,使得其靜態功耗大約僅僅相當于SRAM器件的1/10。另外功耗占比較大的是串行收發器。對于中階密度SRAM FPGA來說,通常每個10 Gbps接口功耗為160 mW至200 mW。PolarFire FPGA的同樣功能通常僅消耗90 mW。此外,PolarFire還能夠在GPIO中實現SGMII。當采用這種接口時,每個1 Gbps接口的功耗通常小于30 mW。由于靜態功耗最低,且擁有最節能的1 Gbps和10 Gbps以太網接口,因此,與類似中階密度SRAM FPGA相比,PolarFire FPGA的總功耗降低幅度高達50%。

3結論

以太網通信新需求推動工程師尋找新的解決方案。現在,中階密度FPGA可以很好地應對1 Gbps 和10 Gbps以太網應用中。不管這些應用是接入網、SFP、網關、路由器或其它設備,設計人員都不再為了應對必需的要求而被迫犧牲成本和功率效率。PolarFire中端FPGA的低功耗、小尺寸,并擁有優化的以太網接口,這個特性能夠滿足以太網通信市場的新需求。

評論