FPGA可測性設計的“大數據”原理

當下,最火的學問莫過于“大數據”,大數據的核心思想就是通過科學統計,實現對于社會、企業、個人的看似無規律可循的行為進行更深入和直觀的了解。FPGA的可測性也可以對FPGA內部“小數據”的統計查詢,來實現對FPGA內部BUG的探查。

本文引用地址:http://www.j9360.com/article/201710/367065.htm可測性設計對于FPGA設計來說,并不是什么高神莫測的學問。FPGA的可測性設計的目的在設計一開始,就考慮后續問題調試,問題定位等問題。要了解FPGA可測性設計,只不過要回答幾個問題,那就是:

(1) 設計完成如何進行測試?

(2) 設計出現問題,如何迅速定位?

(3) 如何在設計之初就能劃分故障的層次,進行問題隔離?

一般情況下,在設計的調試階段,如果出現BUG,則需要通過嵌入式邏輯分析儀(chipscope/signaltap)對可能出現問題的信號進行抓取。這種方式,對于較大型的設計調試速度較慢(其編譯時間較長,迭代速度較慢,但是也是一種很有效的手段和FPGA的必備技能)。那么對于大型工程的可測試性,有什么行之有效的手段?

(1)統計計數。

FPGA設計中的統計計數不是不是什么”大數據“,只不過是些“小數據”,例如,對于網絡接口來說,收到多少包,發送多少包,收到多少字節,發送多少字節。 對于一個模塊來說,收到多少次調用,或者發起多少次操作。對于讀取FIFO的數據流操作,從FIFO中讀取多少frame(幀),向后級FIFO寫入多少幀。

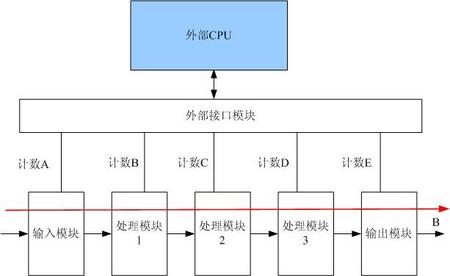

這些計數,毫無疑問都是需要占用資源的,但是占用這些資源是有價值的。通過這些計數,設計可以通過總線接口供外部處理器讀出。于是一張FPGA內部設計的“大數據”圖形就顯現出來了”。

從上圖可得,通過外部CPU可將各處理模塊中的計數,分別讀出,于是得到其內部的一張數據流圖。我們可以簡化設計為(計數A->計數B->計數C->計數D->計數E)。實際使用中可根據占用的資源和實際需要的觀測點來確定。

假設,我們在調試過程中發現,有輸入突然沒有輸出,這是不需要再去內嵌邏輯分析儀來抓取信號,通過CPU的軟件,可以打印出所有計數,在有輸入驅動的情況下,假設計數C有變化,而計數D沒有變化,則直接定位處理模塊3,此時處理有問題,簡單直接而有效。

令一種情形也可以迅速定位,輸入多,但是輸出少,比如正常輸入的碼流,但是輸出到顯示上確實缺幀少幀,完全不流暢。通過計數分析,原本幀計數C和D應該一樣多,但是D卻計數較C少很多,說明此時處理模塊3性能不夠,或者設計有缺陷。這樣就把整個設計的關鍵點定位到處理模塊3.

通過FPGA內部各模塊的關鍵計數分析,來定位分析問題,在設計上沒有任何難度。不過需要外部CPU或者FPGA嵌入式CPU的配合使用。

凡事有利就有弊,添加多的計數,會增加資源的使用量,那么如何平衡?對這種分析計數進行單獨位寬設定,在全局統一的宏定義中定位`define REG_WIDTH N 。此時N的設定可以靈活多樣,8位/16位/32位等等。可以根據項目中資源的剩余量,靈活添加所需的邏輯,畢竟這些計數的值提供分析試用。

(2)狀態輸出。

如果向上述問題一樣,我們定位到某個模塊,那么如何再定位到模塊中那個邏輯的問題?

解決這個問題的關鍵,就是狀態機,向輸出計數一樣,一般的設計中,都會以狀態機為核心進行設計,將狀態機的CS(當前狀態)信號引出,如果沒有外部輸出的情況下,當前狀態應該為IDLE。比如上文中,我們定位到模塊3此時死機,等待不再輸入外部信號時,此時模塊3中的狀態機信號如不為IDLE,假如此時正處于狀態B_CS,則說明此時模塊的錯誤出現在狀態B。而B跳轉必須由信號X起效。因此可以直接定位到信號X的問題。剩下就是要定位信號X為什么不起效。

(3)邏輯復位。

劃分FPGA的問題或者模塊問題的另一種方式就是邏輯復位,上文講復位時(架構設計漫談),邏輯復位,如果A模塊自身有邏輯復位,如果設計沒有輸出(通俗叫做“FPGA死了”),如果懷疑某個模塊,該模塊邏輯復位后,設計又正常工作,則需要定位的則是可以是該模塊、或者該模塊影響的與其連接模塊(該模塊的非正常輸出導致下一級模塊出錯)。

本文將的FPGA可測性設計,非ASIC講的通過插JTAG/BIST進行的測試。其目的還是通過關注如何測試的設計,來定位問題,提高FPGA的可測性。除此之外,邏輯探針也是可以一個解決測試問題的方向(專題另述)。可測性的提高,意味著調試手段的增加,調試速度加快,而不是一味的依賴嵌入式邏輯分析儀。能夠達到快速問題定位能力,是FPGA研發能力一個重要的體現,而可測性設計則是提升這一能力有力的助手。

評論