在數字電路設計中,時鐘信號是一種在高態與低態之間振蕩的信號,決定著電路的性能。在應用中,邏輯可能在上升沿、下降沿觸發,或同時在上升沿和下降 沿觸發。由于溢出給定時鐘域的案例極多,故有必要插入緩沖器樹來充足地驅動邏輯。時鐘樹通常帶有布線工程師必須滿足的延遲、歪曲率、最小功率及信號完整性 要求。

本文引用地址:http://www.j9360.com/article/201706/358178.htm當電路從前工序設計人員轉移到后工序

布線工程師時,可以認為時鐘概述與圖表是必須溝通的最關鍵信息。多年以來,由于溝通失誤,數以小時、天甚至是星期計的設計工作淪為白費,需要包括時鐘樹在內的全套重新合成。

在

布線之前,采用極佳的時鐘來用于合成及時序約束。約束的時鐘定義可能出現在模塊的頂層焊盤或引腳;可能出現在宏的輸出,如鎖延遲環(DLL) 或鎖相環(PLL);或者作為產生的時鐘出現在除法寄存器上。這些時鐘定義可能是也可能不是布線工程師需要定義時鐘樹根以在不同工作模式之間獲得最優延遲 及平衡歪曲率的領域。前工序及布線工程師之間圍繞這些信息的高級別信息溝通以及理解布線工程師怎樣運用這些信息,將大幅優化物理設計流程的

CTS過程。

下面的某些技巧在業界已經使用多年,但基于過去幾年的經驗,仍然值得重復運用。

為時鐘樹根使用中到大強度的驅動器。這就使時鐘樹能有恰當的起點。但不要使用庫中最大的驅動強度,如果信號完整性(SI)分析或片上變化(VOC)分析未出現問題,能夠在隨后的設計中用到。

如果時鐘除法寄存器及其同步寄存器要在單獨測試模式中工作,確保它們被復用邏輯有針對性地驅動。這就能夠在測試模式下在輸入端增加延遲,而不會影響此功能模式下所產生的時鐘驅動的其他所有寄存器。

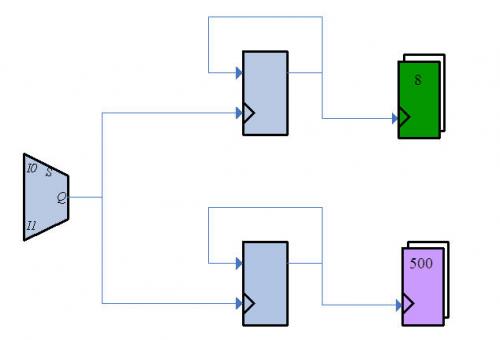

(divide-by)寄存器不會與任何下行寄存器平衡。綠色域的寄存器數量越少,越會使時鐘速度比紫色域中的時鐘速度快得多。

圖1 寄存器時鐘除法寄存器

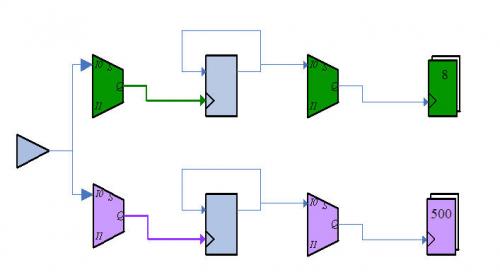

圖2顯示了可能使每簇下行寄存器及除法寄存器能夠通過復用的一種輸入擁有極小時鐘及通過復用的另一路輸入擁有平衡時鐘的復用機制。

圖2 下行寄存器及除法寄存器復用機制

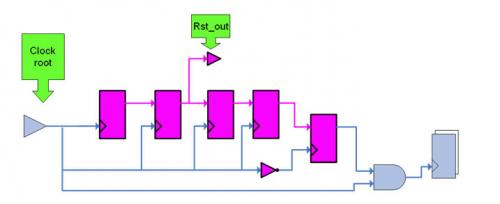

若有需要,則插入專用復位驅動器。某些情況下將使用幾個寄存器來同步復位。那些寄存器可能并不需要由相同的寄存器來平衡。在圖3中,由于未采用集中策略,軟件將嘗試平衡門控邏輯后的藍色寄存器,而每個粉紅色寄存器包含在復位同步邏輯中。

圖3 平衡門控邏輯后的寄存器

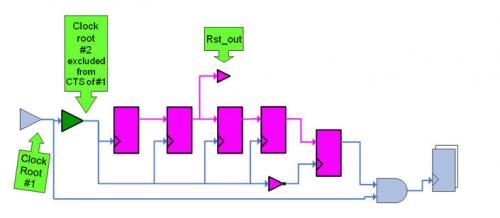

如果它們在各自專用驅動器中與其他寄存器分開了的話,在布線過程中這種情況就很容易處理。圖4顯示了可以怎樣在設計交遞(hand-off)溝通過程中插入及輕易識別占位符(place-holder)或排除緩沖器,使布線工程師知道哪里可能會出現平衡問題。

圖4 插入及輕易識別占位符或排除緩沖器

提供超出預期的時鐘圖表及大量時鐘簡介。當前工序設計準備好提供網表進行布線時,他們已經非常熟悉設計及時鐘要求。某些情況下,初始

CTS設計 會提示預布線時序約束中使用的理想值在實際物理設計中不能實現的情況。如果提供了精確的時鐘圖以及帶有時鐘原理相關信息的網表交遞,就能夠更快地弄清導致 此狀況的問題。

總體圖或是代表設計中所有時鐘(含門控邏輯)的圖非常有用。這要么是采用畫圖軟件,要么是使用電路圖捕獲工具等使用軟件產生的圖,甚至還可以是手繪并存儲為PDF文檔或發送傳真給布線工程師的圖。此圖抵得上嘗試直接獲得時鐘格式的多次通話或電子郵件溝通過程中的千言萬語。

由于圖表可能會很復雜繁瑣,就需要提供相應的簡介文檔,包括產生的時鐘、任何時鐘門控或復用圖案的詳情以及歪曲率平衡和延遲要求等方面的闡釋。 每種工作模式都需要這些詳細信息,因為在插入時鐘樹期間必須應對每種模式。寄存器可能最后會提供用于功能模式的平衡,但如果我們不仔細的話,測試模式下可 能極不平衡。

如果時鐘使用DLL或其他宏或它通過門控邏輯,這些詳細信息就在所必需了。如果有需要的話,有可能通過那些類型的宏來合成及平衡。對于門控邏輯 而言,如果存在一個引腳通過一種模式來連接、但同單元的其他引腳采用另一種模式來連接的情況,走線工具將把這種情況識別為“重匯聚時鐘”。雖然布線工具可 以解決這些問題,但更好的解決辦法可能是迫使工具在時間插入期間查看這個引腳而非其他引腳。

業界軟件工具中的CTS

業界軟件遵循設計人員的規格及指引,以強大的工具推動時鐘樹合成。源自前工序的跟時鐘樹根插入點、延遲、歪曲率及過渡目標相關的信息以及用于門 控邏輯、通過寄存器和跨域關系的詳細信息能夠直接移植到CTS工具中。然后布線工程師將自已判斷要使用的緩沖器類型、優化迭代及間距、屏幕和金屬層等布線 要求。

在插入時鐘樹之前,能夠使用走線來確保存在旨在用于平衡的端點。還能夠提示及評估門控邏輯、時鐘樹根排除的分支、IO端點以及重匯聚實例。

時鐘樹可能僅包含緩沖單元或是系列反相器。如今的大多數技術擁有特別的時鐘緩沖及時鐘反相單元,這些單元提供平衡的上升及下降時間,以幫助確保占空比不被損及。還可以整合其他要求,如時鐘樹中等級或各個時鐘單元的最大扇出。

結論

除了上文探討的所有因素,布線工程師很可能還會嘗試有時鐘門控意識的布局、時鐘布線指引及平面布局調整。CTS替代通常在極少調整歪曲率、延遲 及過渡目標的情況下運行。試錯法幫助提供極佳的協調。如果前工序理解CTS如何工作且在最開始就溝通時鐘結構,那么布線工程師將能夠更加得心應手地接手任 務。日程中原本計劃用于CTS的時間就可以用于微調及改善“你的時鐘”,而非簡單地嘗試將其插入到“我的布線”。

...........................................................

與非深度解讀系列:

半導體公司“大學計劃”的追問和真相

大環境的不景氣是就業環境惡化的元兇,但是也讓我們不禁追問半導體公司的大學計劃對于學子們的真正意義。廠商們的大學計劃都在做些什么?那么多的聯合實驗室有得到充分利用嗎?大學計劃的直接體驗者--老師和學生們是否真正從中受益…….【專欄作者:高揚】

本土IC公司調查筆記

全球經濟不景氣的大環境下一些本土IC公司的創新能力、管理能力、抗風險能力、盈利能力,甚至公司創立的動機都受到一些質疑。一方面官方的消息總是告訴我們中國的半導體產業得到了長足的進步;而街巷小道中又不絕流傳多少本土IC公司倒閉,多少公司靠欺騙,根本沒有核心競爭力….真相只有一個,也許會隨《本土IC公司調查筆記》慢慢開啟…【專欄作者:岳浩】

電子屌絲的技術人生系列

在這個系列里,每個故事都會向你展示一個普通工程師的經歷,他們的青蔥歲月和技術年華,和我們每個人的的生活都有交集。對自己、對公司、對產業、對現在、對未來、對技術、對市場、對產品、對管理的看法,以及他們的經歷或正在經歷的事情,我們可以看到自己的影子,也看清未來的樣子……【專欄作者:任亞運】

細說電子分銷江湖的那些事

對于從事電子分銷行業的同仁們來說這是一個最壞的年代,也是一個最好的年代,我們即面臨國際分銷巨頭在管理、資金、貨源等方面對我們造成的沖擊,又迎來本土集成電路的崛起,個性化服務盛行的機遇,通過這個系列,我想以“第一現場”的經歷帶大家一起了解國內集成電路分銷的那些年、那些事,以及哪些感慨…..【專欄作者:張立恒】

與非網專欄作者申請

聯系人:高揚

郵箱:gaoyang@eefocus.com

評論