高速A/D系統設計結構及電路設計問題

在現代雷達系統、激光測距以及高能物理試驗中往往產生寬帶信號或者上升沿比較陡的信號(一般10ns左右)。若對此類信號進行數字化處理,要求A/D部分的采樣率至少應該在200M/s以上。本文介紹的系統正是針對這樣的要求而開發出來的。

本文引用地址:http://www.j9360.com/article/201706/353099.htm1 系統結構

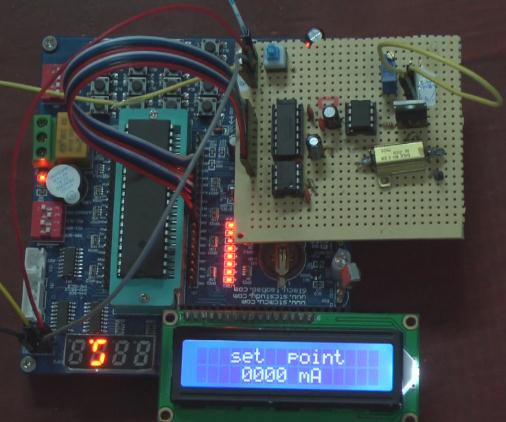

系統分為A/D轉換和數據傳輸控制兩大部分(圖1)。數據傳輸控制部分作成PC機的插卡在計算機的PCI擴展插槽內,它的主要功能是將A/D采樣得到的數據傳遞給計算機,同時產生相關的控制信號去控制整個系統;A/D轉換部分由于受到電源和體積的影響單獨作成一個模塊置于計算機外部,其中關鍵的核心器件ADC采用的是MAXIM公司推出的MAX101A,它的最高采樣率可達500兆/秒,采樣精度為8bit。兩部分之間的數據傳遞通過扁平電纜來完成。

2 A/D轉換

2.1信號調理

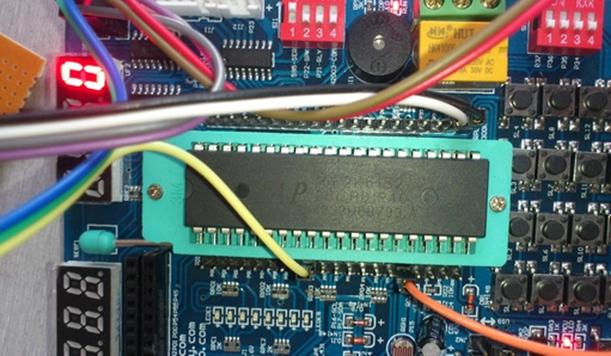

對于高速A/D采樣電路來講,前端調理電路顯得尤為重要,不僅要有足夠的帶寬,而且還要將單端的輸入信號變成差分信號提供給ADC,以減少偶次諧波的產生,同時本身的噪聲也要很小,這樣才不會對ADC的精度產生影響。考慮到上述因素,在前端部分采用了AD公司的AD8138作為緩沖放大器,它的性能指標為:-3dB帶寬320MHz,輸入噪聲5nV/(根號Hz)。AD8138為表面封裝器件,本身的體積非常小巧,使得ADC與信號輸入點的距離可以很近,大大減少了外界噪聲的影響。經測試,器件的模擬帶寬為230MHz(圖2)。

2.2 系統時鐘的選擇

ADC芯片MAX101A要求的采樣時鐘為500MHz的ECL差分時鐘。對于如此高速的時鐘電路,孔徑晃動(jitter)是選擇時鐘源的一個非常重要指標。Jitter是指時鐘沿本身不穩定,在一定范圍內晃動,時鐘沿的晃動會帶來采樣點的不確定性,被采樣信號的頻率越高造成的誤差就越大(圖3)。經過調研,市場上有兩種比較成熟的芯片可供選擇。一是Motorola公司MC12439,另一個是Synergy公司的SY89424。MC12439可輸出的頻率是50~800MHz(Peak-to-Peak jitter 25ps 8δ),/TRK1 SY89424的最高輸出頻率為1GHz(Peak-to-Peak jitter 3δ)且兩者的輸出電平都為差分的PECL。雖然兩種芯片給出的jitter相差不大,但實際上以上參數都是在輸出時鐘頻率小于其最大輸出頻率一半的條件下給出的,也就是說此時的輸出時鐘是內部VCO的輸出經過分頻后得到的。如果輸出時鐘不經分頻而直接輸出,輸出時鐘的頻率實際上是內部鎖相環VCO頻率的兩倍,輸出時鐘的穩定性與VCO時鐘的占空比有直接的關系。而VCO很難保證它的占空比總是50%,后以在這種情況輸出時鐘jitter將大大增加。鑒于上述原因,最終選擇了Synergy公司的輸出頻率可達1GHz的SY89424。

2.3 特殊電平時鐘的產生

MAX101A芯片內部是由采樣率為250兆/秒的完全獨立的兩個ADC拼在一起而得到的,從模擬信號輸入、參考電壓到數字信號輸出都是完全分開的兩部分。這樣做給與用戶很大的自由度,但同時也帶來一個問題,那就是很難確定在每一次上電后究竟是哪一個ADC先輸出,從而無法正確地進行數據鎖存。MAX101A要求用戶提供一個外加的控制信號TRK1和TRK1來確定兩個ADC的先后順序。它規定在系統采樣時鐘的下降沿到來時,如果TRK1為“1”,/TRK1為“0”則第一個ADC輸出有效,反之則第二個ADC輸出有效(圖4)。這樣的控制信號實現起來并不難,但MAX101A對TRK1和/TRK1的邏輯電平范圍的規定是一個非常規的值,它規定輸入電平在±50mV之間為邏輯“1”,在-350mV到-500mV之間為邏輯“0”。對于這樣一種非標準的時鐘電路,不可能用現成的芯片直接產生,為此在模擬偽真結果的基礎上,采用了圖5所示的電路來產生這樣的時鐘信號。D觸發器將時鐘信號二分頻后經隔直電容送到電阻分壓網絡進行衰減,同時提供新的基準電平,這樣原來的ECL信號(-900mV~-1800mV)就被轉換成在0~-450mV之間的時鐘信號,滿足了MAX101A的要求。電容隔直方法在高速數字電路中應用十分廣泛,應用這種方法可以很方便地將不同電平范圍的信號(如ECL和PECL)進行相互轉換而不需要額外的電路,使用起來相當方便。

2.4 高速數據的鎖存

高速ADC的數據鎖存在A/D系統里的設計一直都是一個難點,ADC的速度越高數據鎖存的難度就越大。盡管MAX101A的數字輸出已經分成了A、B兩個端口,使每個數據通道的速率降為250Mbyte/s,但要將如此速度的數據準確無誤的鎖存下來還是相當困難的,必須進一步降低數據端口的輸出速率。降低端口速率唯一的辦法就是將輸出端口的數據分成多路交替輸出,使每一路的數據產生率降到可以接受的速度。但是分的路數越多,電路就越龐大,各種時鐘與數據之間的關系也就越復雜。綜合兩者考慮,采取了將ADC的輸出分成八路的方案,這樣每一路的數據產生率為62.5Mbyte/s,完全可以用普通的鎖存器來完成。數據鎖存部分的結構如圖6所示。

MAX101A輸出的鎖存時鐘(250MHz)經四分頻后送入一個六位的移位寄存器產生6個相差4ns的時鐘,其中的ABCD用于鎖存各個端口的數據,CDEF經電平轉換后作為EPLD鎖存數據的時鐘,之所以推遲兩個時鐘是為了補償數據的傳輸延時和EPLD內部FIFO的建立時間。數據進入到EPLF后,后端的處理就方便得多了,可以用EPLD作DRAM控制接口將FIFO的數據存儲到大容量的DRAM中去,也可將數據分組打包通過傳輸介質傳遞給計算機進行處理。在本系統中,采取第二種方法將數據通過電纜傳遞給位于計算機內的一塊PCI卡上,計算機再通過它把數據存放到硬盤上。

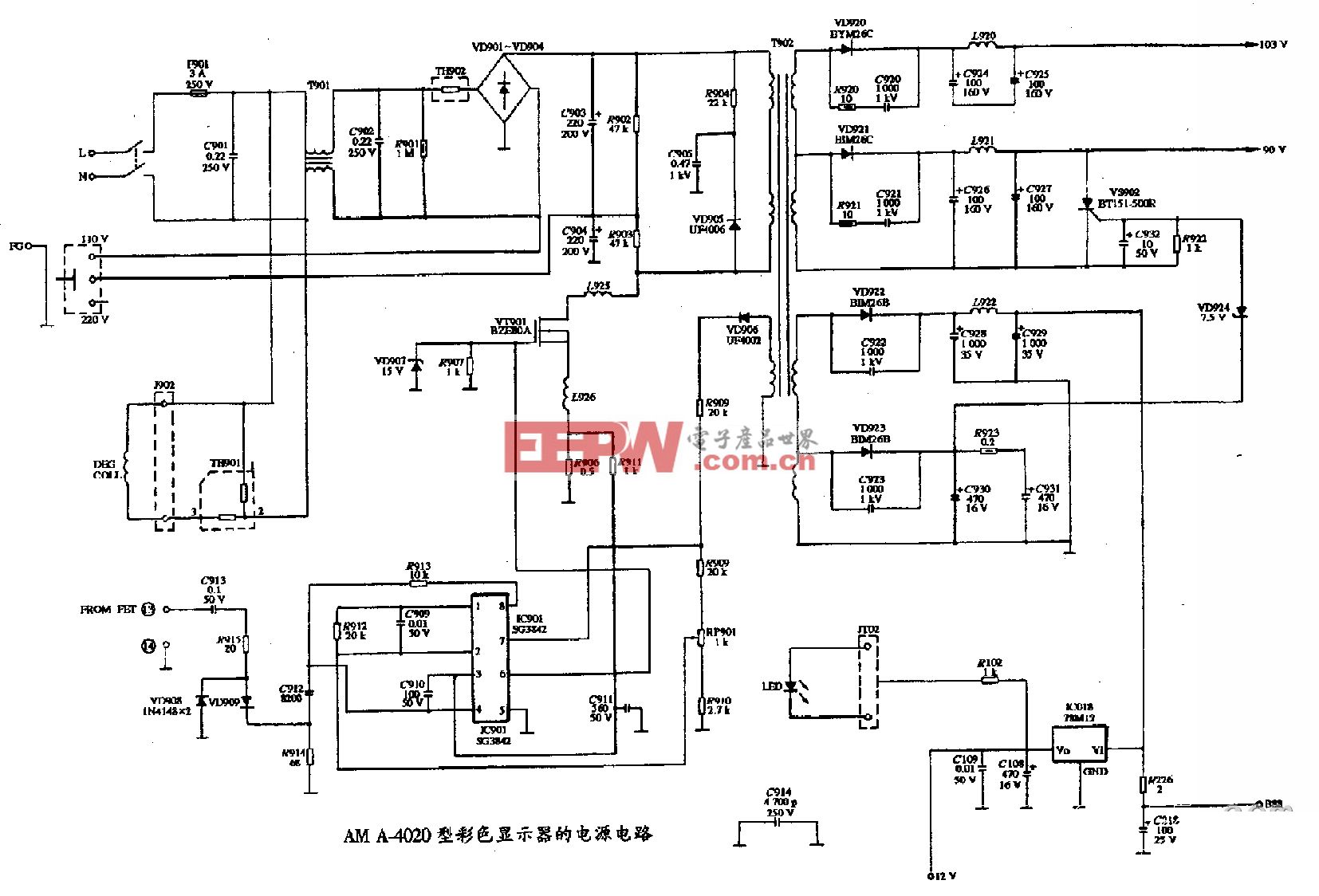

3 高速電路的設計

在高速電路中如何避免各個信號之間的串擾(crosstalk),以及如何保證信號的完整性(integrality)是整個系統正常工作的保障。首先,對于高速電路電路板(PCB)應至少采用四層以上的多層板技術,本系統采用了六層板(表1).采有多層板的目的并不僅僅是為了走線的方便,更重要的是使用了大面積的電源或地層之后可以使各信號線與地或電源平面之間形成一個緊耦合從減少信號線之間的串擾。通常所用的在走線層大面積網格鋪地的方法,雖然也可起到一定的屏蔽作用,但其面積和與信號線距離的關系遠不如地平面產生的效果好。其次,系統的整體布局要合理,應該綜合考慮地平面和電源層的分割。使用相同電源和地的芯片,布局盡量放在一起以避免地平面被瑣碎的分割。當同一塊電路板上既有模擬電路也有數字電路時,更應該仔細地考慮這兩部分的布局。模擬部分和數字部分應該隔離,不僅是空間的隔離,而且電源也應該隔離,兩部分最好單獨供電。最后,模擬地和數字地通過磁珠(ferrite bead)在一點相連。地平面上的電流一般比較大,大電流流過時會對表面上的器件產生一公平的影響,尤其是對模擬器件產生的影響將直接反映在輸出信號質量的好壞。為了減少地電流的影響,在設計地平面時應該在比較敏感的模擬器件下方加一道隔離溝阻斷大電流的通路(如圖7所示),以減小地電流對它的影響。

表1

名 稱 用途說明

頂層 布線、元件

中間層1 模擬地、VTT

中間層2 數字地、ECL的VCC

中間層3 模擬+5V、數字+5V、數字+3.3V

中間層4 模擬-5V、數字-5V、數字+2.5V

底層 布線

高速電路的PCB設計是整個系統成敗的關鍵,PCB的設計在很大程序上與所選用的EDA工具有關。在本系統的PCB設計上選用的是PADS公司出品的PowerPCB,它和傳統的設計工具Protel相比有如下優點:

(1)支持圓弧拐角布線,減少信號線的輻射,降低串優;

(2)支持淚滴焊盤,使走線阻抗變化均勻,減少反射;

(3)可以方便地在PCB的內部層進行分割和走線;

(4)支持多種布線規則,如布線長度、走線阻抗等規則;

(5)與自動布線器Specctra接口方便;

(6)直接支持信號完整性分析軟件HyperLynx。

鑒于以上種種優越性能,它非常適合于高速電路板的PCB設計。

4 Windows95下軟件設計的實時性考慮

本系統的軟件運行于Window 95平臺之上的。設計的指標要求每秒能計時200次的操作,每次采集512點,既要求系統在5毫秒內將A/D部分采到的512Bytes傳到計算機并存儲在硬盤上。這個要求對于PCI接口來說是非常低的,實測結果顯示系統的平均反應時間遠小于這個時間。但是結果顯示系統的平均反應時間遠小于這個時間。但是我們發現系統每處理10 000次響應總會有一到兩次的反應時間特別慢,超過5毫秒有時甚至達到40毫秒。而我們的系統要處理的是一個連續有序的事件,要求對每一個事件都必須做反應,否則后面的事件就會被誤處理。經過分析表明,這種現象完全是由于Windows95操作系統本身的原因造成的。Windows95是一種多任務的平臺,它的核心運行在優先級較高的Ring0上,普通的應用程序則運行在優先級低的Ring3上,應用程序靠內核的調度分時運行。Windows95是專門為PC機設計的,主要的用途是處理人們的娛樂以及辦公自動化等事務,考慮的是使用起來如何方便,并沒有對工業控制方面的實時性加以考慮,所以外層的應用程序有可能會隨時被內核打斷,根本沒有什么時間的保障。

要想準確無誤地處理對時間要求比較荷刻的事件,必須把處理程序放在運行于內核級的中斷服務程序中去執行,這樣除非有更高級的中斷否則程序就不會被打斷。在編寫中斷服務程序處理函數時我們采用了Windriver提供的Kernal PlugIn功能,將自己編寫的中斷服務程序掛接在系統內核上。用此種方法可以實現每秒10 000次的斷處理而不丟失。我們在編寫中斷服務程序時借用了硬件設計中FIFO的思想,先在內存中開辟一塊共域作緩沖區分別設置讀指針和寫指針,硬件觸發中斷后服務程序先從A/D讀取數據進行處理,然后發了指令控制A/D等待下一次事件,接著向上層應用軟件發出消息請求上層應用程序從緩沖區讀取數據存盤和顯示。中斷服務程序發出的消息有可能不會馬上被上層應用程序響應,但只要緩沖區足夠大,每一次事件產生的數據就不會丟失。整個程序的流程圖如圖8所示。

本數據采集系統成成功地在上海某科研單位得到應用。雖然設計初衷是為了滿足某用戶的需求,但它容易擴展成通用的A/D采樣系統應用于相關的各個領域。

評論