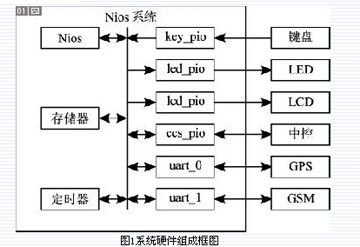

基于SOPC的JPEG2000編碼器設計

為了滿足網(wǎng)絡及多媒體領域的應用,JPEG2000的硬件實現(xiàn)具有重要意義。本文提出了一種改進的行式二維小波變換器結構,設計了位平面并行的位平面編碼器和四級流水線結構的算術編碼器,并將其整合于一個SOPC中,實現(xiàn)了JPEG2000編碼系統(tǒng)。整個設計通過Altera公司Stratix II系列的EP2S60F1020C5平臺驗證,在最高時鐘頻率98MHz下能達到編碼分辨率512*512 灰度圖像52frame/s的速度,滿足了實時編碼的要求。

基于SOPC的JPEG2000編碼器設計.pdf

評論