JPEG 2000標準中MQ編碼器的VLSI結構設計

引 言

JPEG 2000是為了彌補JPEG的不足而提出的新一代靜止圖像壓縮國際標準。其目標是對多種類型的靜止圖像實現高效壓縮,并要求壓縮碼流具有較好的抗誤碼性能,用戶可對圖像進行多種形式的累進傳輸,還可以對壓縮碼流進行隨機訪問和處理。

JPEG 2000用基于上下文的自適應算術編碼取代JPEG系統中的赫夫曼編碼,對量化后小波變換系數的二進制位平面進行算術編碼。算術編碼對每一小波子帶分塊獨立進行位平面編碼,并將每個位平面分在3個子位平面通道內進行編碼。雖然現有算術編碼在算法上做了很多改進,但算法的復雜性和大量的編碼數據導致MQ編碼器的實際工作效率仍然很低。為了提高MQ編碼器的編碼速度,對編碼流程進行優化,提出一種基于三級流水線的MQ編碼器的VLSI結構。

1 MQ編碼器原理

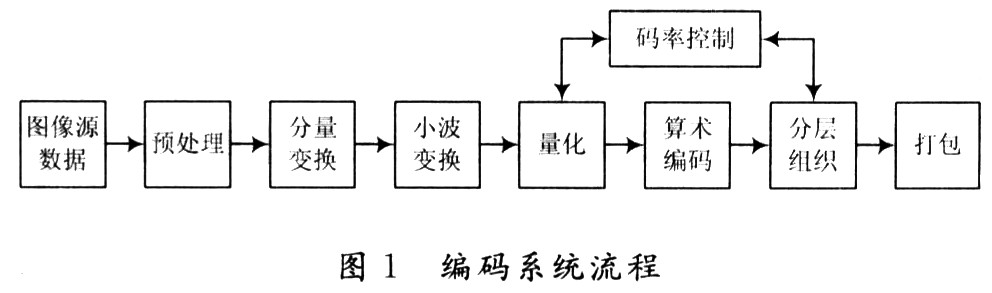

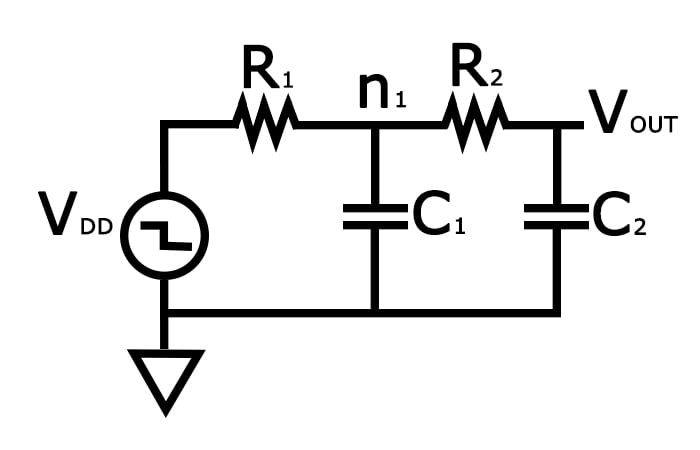

JPEG 2000的編碼系統流程如圖1所示。

在JPEG中,作為無損壓縮DCT系數的熵編碼方法,采用了霍夫曼編碼(算術編碼為選項)。霍夫曼編碼因按DCT系數大小來分配可變碼長,所以查表處理形成主體,能夠簡單實現霍夫曼編碼。但是,由于預先調查了解符號系列的統計性質后制表,所以此后一旦有與其性質相違背的符號輸入進來,就難免使壓縮特性惡化,這個不足限制了其應用范圍。

補救霍夫曼編碼這一缺點的就是JPEG 2000中被采用的自適應算術編碼。算術編碼的構思是作為Elias編碼,依據為人們所熟悉的劃分遞歸概率區間的設想,在Elias編碼中,對于具有 “0”或“1”值的二進制符號系列,以各自概率值比率將當前概率區間劃分成兩個子區間,被分配給實際產生符號的概率值區間下限值構成代碼串。即代碼串按二進制符號系列的輸入逐次被遞歸地修正下去。

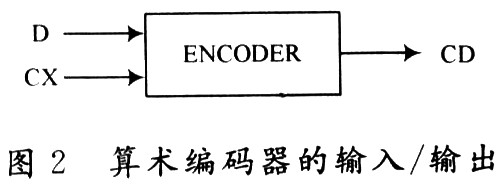

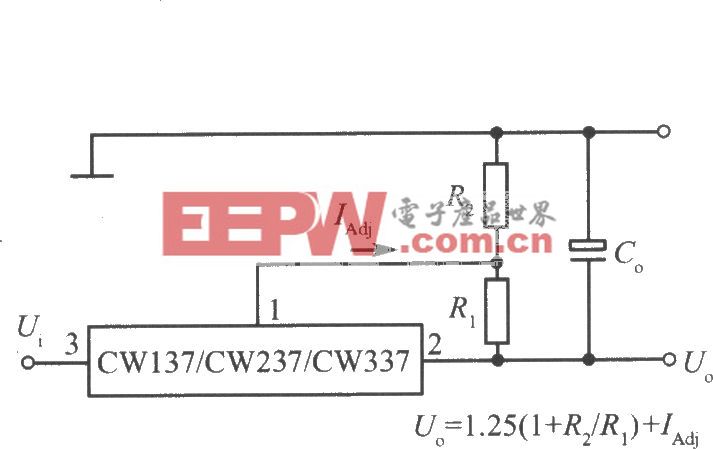

JPEG 2000中采用算術編碼,其基本規則像Elias編碼那樣,不是以符號“0”和“1”的實際值來區別,而是分別作為MPS(大概率符號)或LPS(小概率符號)中一個子區間來區別的。而且,將當前概率區間劃分成兩個子區間時的順序是MPS子區間可配置到LPS子區間的上面。因此,若符號是MPS,就在給代碼串附加LPS子區間的同時,設概率區間寬度為MPS子區間;若符號是LPS,就不改變代碼串,設概率區間寬度為LPS子區間。按判決輸入將此處理遞歸地重復下去。MQ編碼器的輸入/輸出框圖如圖2所示。其中,D是二進制判決;CX是上下文索引;D和CX二者均事先由算術編碼之前進行的系數位建模確定。 CD是輸出的壓縮數據。

在MQ算術編碼器中,用寄存器A表示當前子區間的寬度,寄存器C表示子區間的起始位置。它們均具有16 b有效長度,在發生重新歸一化時,為了避免16 b的C寄存器溢出,而采用28 b表示。通過采用重新歸一化方案,使A的取值范圍保持在[0.75,1.5]。當編碼器接收到一個新的待壓縮碼,編碼器從概率估值表查找相應的概率Qe。根據接受的待壓縮碼類型,寄存器A的值和寄存器C的值被進行更新,從而區間更新可近似為:當編碼MPS時,A=A-Qe,C=C+Qe;當編碼LPS時, A=Qe,C=C,避免了乘法運算。

同時,由于MQ算法在進行區間計算時省略了乘法的近似,使得可能發生LPS子區間大于MPS子區間的情況。為了避免這種情況,采用區間條件交換,即將 MPS與LPS互換。MQ編碼器通過重歸一化方法解決計算的有限精度問題:當AO.75時,對A進行左移直至不小于0.75為止,同時C也左移同樣位數,并按一定間隔將不再變化的高位移入存儲區。

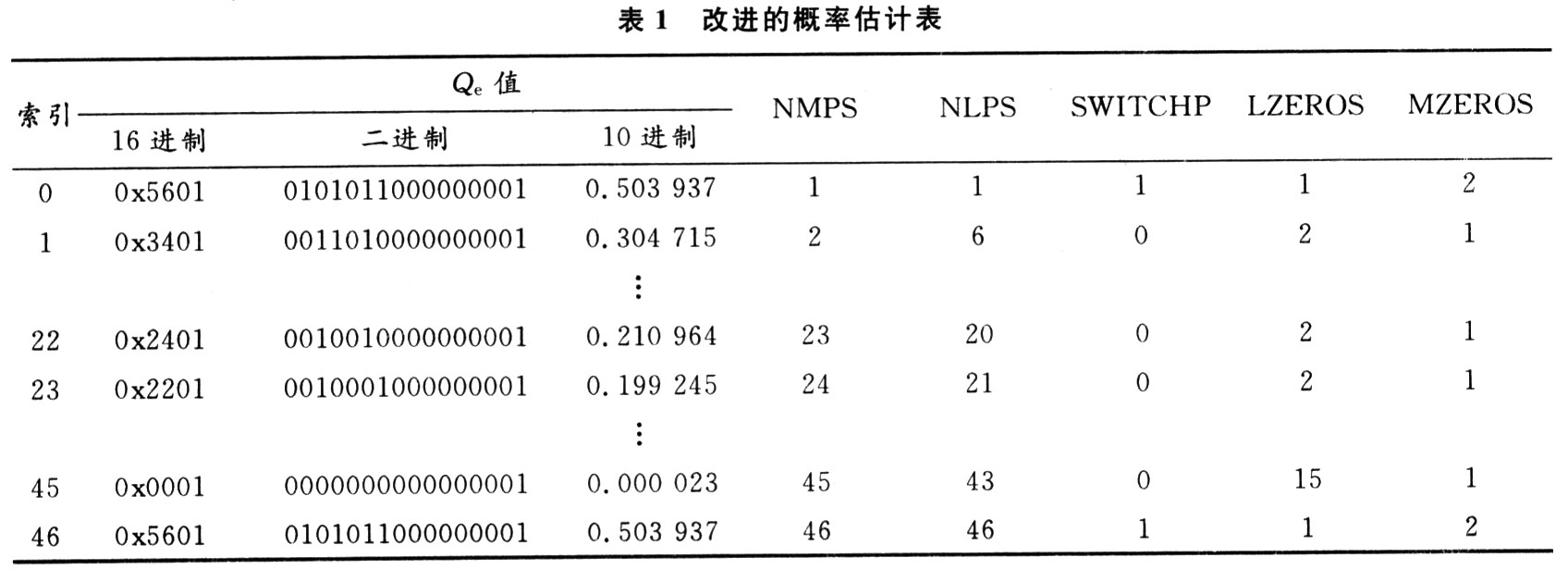

MQ編碼器所使用的概率估值表是一個可以對原始數據快速適應的復雜概率自動估計模型。該模型是一個具有47個狀態的有限狀態機。每個狀態包含小概率符號 LPS的概率Qe、下一個狀態的索引NMPS和NLPS。是否需要交換MPS和LPS所代表符號的標志SWITCH。

MQ編碼器中設置了一個專用計數器CT作為已壓縮字節輸出控制。當A左移1位時,CT也同時減1;當CT=0時,輸出1個字節。為避免區間更新過程中產生的進位向前傳播,在MQ編碼器中,采用位填充技術來處理進位問題。根據字節緩沖B及C進位位的值,編碼器選擇是否進行位填充。

2 MQ編碼器的優化

MQ編碼器采用串行執行方式,且編碼算法復雜、耗時,從而導致編碼器執行速度慢,效率低下。為了提高MQ編碼器的運行速度,利用FPGA的大容量和并發執行等特性,對MQ編碼器進行設計,在不改變原算法理論的條件下,對整個流程進行改進和優化。

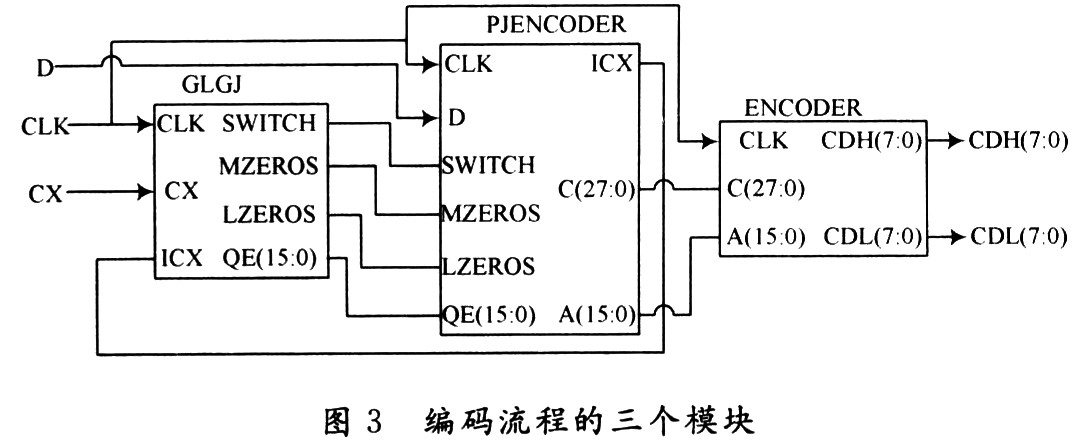

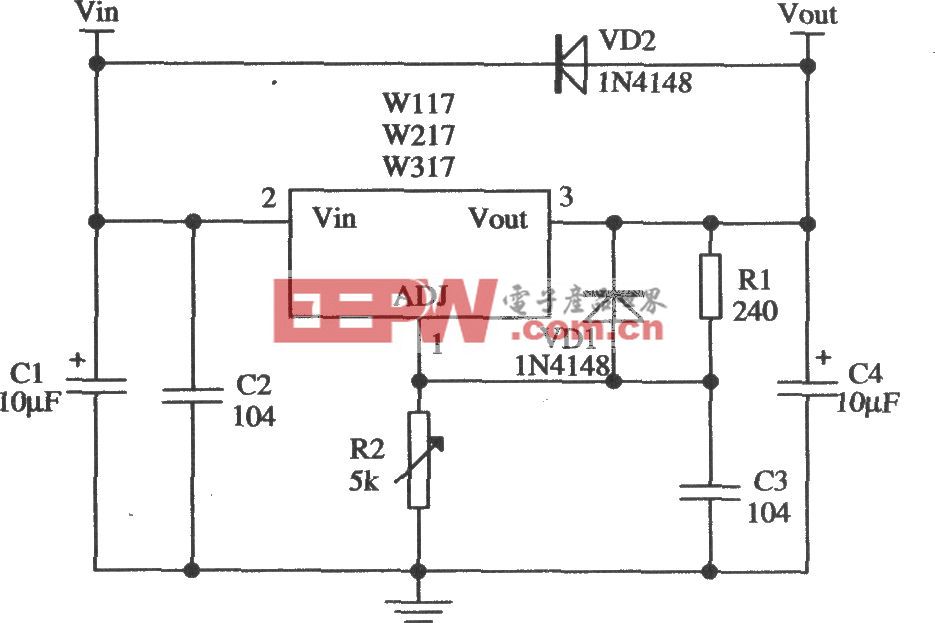

只有當前一輸入的結果被輸出后才能讀人下一輸入的串行執行方式,極大地限制了編碼速度的提高。為解決這個問題,將整個編碼流程分成三個大的模塊(如圖3所示)串接起來,采用流水線的方式進行工作。

其中,GLGJ模塊為概率估計模塊,其功能是根據上下文索引CX選擇,判決D編碼所必需的概率估值和相關數值,在各個上下文自適應更新數值; PJENCODER模塊為判決編碼模塊,其功能主要是進行MPS編碼或LPS編碼、重新歸一化等主要數據處理進程;ENCODER模塊為編碼輸出模塊,主要完成壓縮數據的輸出及編碼終結等功能;由這三個模塊組成三級流水線。

2.1 判決編碼的化簡

判決編碼中先判斷D的取值是“0”還是“1”,如果D=0,就進行0的編碼;如果D=1,那就進行1的編碼。在“0”或“1”的編碼中,又要根據MPS (CX)的取值,判斷是進行MPS編碼,還是進行LPS編碼;在MPS和LPS編碼中,先更新區間寬度A的值,即A=A-Qe[I(CX)],再判斷A是大于還是小于Qe[I(CX)],由此與其他的一些條件決定最后的賦值方式。

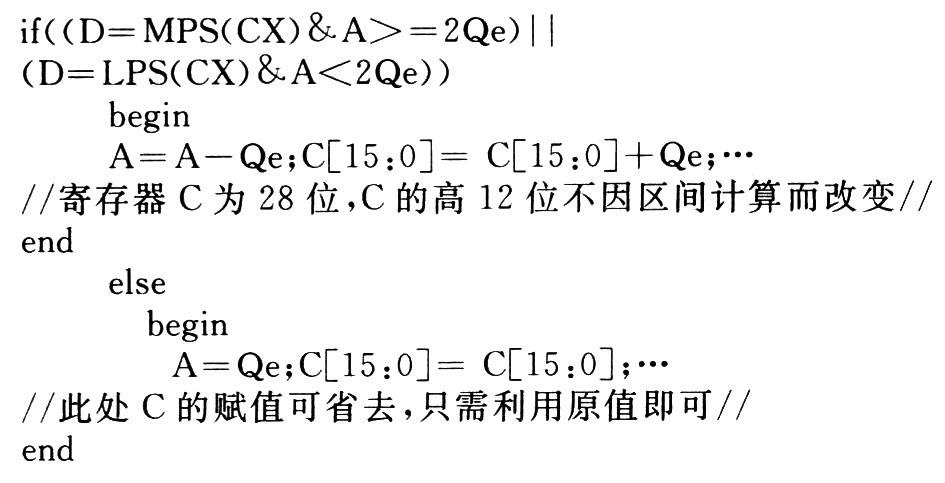

上述過程包括ENCODE,CCOE0/CODE1,CO-DELPS/CODEMPS五個子流程,6個條件判斷,多次賦值,降低了編碼速度。對編碼的判決條件進行整理,減少不必要的賦值,其Verilog代碼如下:

由此可有效地減少不必要的寄存器和位數賦值,加快模塊的工作效率,從而提高整個系統的工作頻率。

2.2 重新歸一化的加速

MQ編碼器一方面在編碼MPS時,給代碼C加上Qe值,將概率區間A減為A-Qe;另一方面,在編碼LPS時,代碼C不變,將概率區間A置換成Qe。如果將這樣的區間劃分運算進行下去,在某一時間點上,概率區間A就會比必要精度范圍(O.75≤A1.5)小,這時就要通過重新歸一化A與C維持精度范圍。

重新歸一化過程是根據條件(A0.75):當條件成立時,將區間寄存器A和代碼寄存器C再左移1次,使其大小加倍,直到概率區間A的大小超過0. 75。由此可見,如果A的值很小,則左移操作將會反復進行,大大降低了編碼速率。同時因編碼中有MPS編碼和LPS編碼兩種,根據D的不同以及編碼方式的不同,重新歸一化時移位的次數也不同。

因此為了提高速度,并充分利用硬件的優勢,將Qe的移位次數作為寄存器數,加入到概率估計表中(表1所示)。無論輸入數據D為何值,編碼的判決都是以 LPS或MPS為標準,所以當判決為LPS編碼時,LZE-ROS中的數據就決定了左移位的次數;當判決為MPS編碼時,MZEROS中的數據就決定了左移位的次數。通過編程將擴展后的概率估計表,以寄存器的方式固化在芯片內部,雖然這樣增加了硬件電路中寄存器的數量,但可以通過一次性的直接查表得到判決編碼和重歸一化所需的數據,提高了查找效率。由于每次編碼都要用到該表,訪問效率很高,這樣大大加快了編碼的速率,同時便于流水線結構的實現。

2.3 編碼輸出模塊的改進

標準MQ編碼器中當輸出計數器CT=0時,MQ編碼器輸出1個字節。標準中字節輸出流程是串行執行的,造成效率低下。又由于重新歸一化過程采用了一次性的移位方式,最大的移位次數可達15次,且過程中伴隨著字節輸出。有三種可能情況:不需要進行字節輸出,需要進行1個字節或2個字節的字節輸出。因此需要對字節輸出機制作改進。這里將減法記數器CT改為5位的加法記數器,并使用一個16位的數據緩存器。根據CT的取值,判別輸出的是0字節還是1字節或者2字節,由此達到加速字節輸出的目的。

3 實驗結果及分析

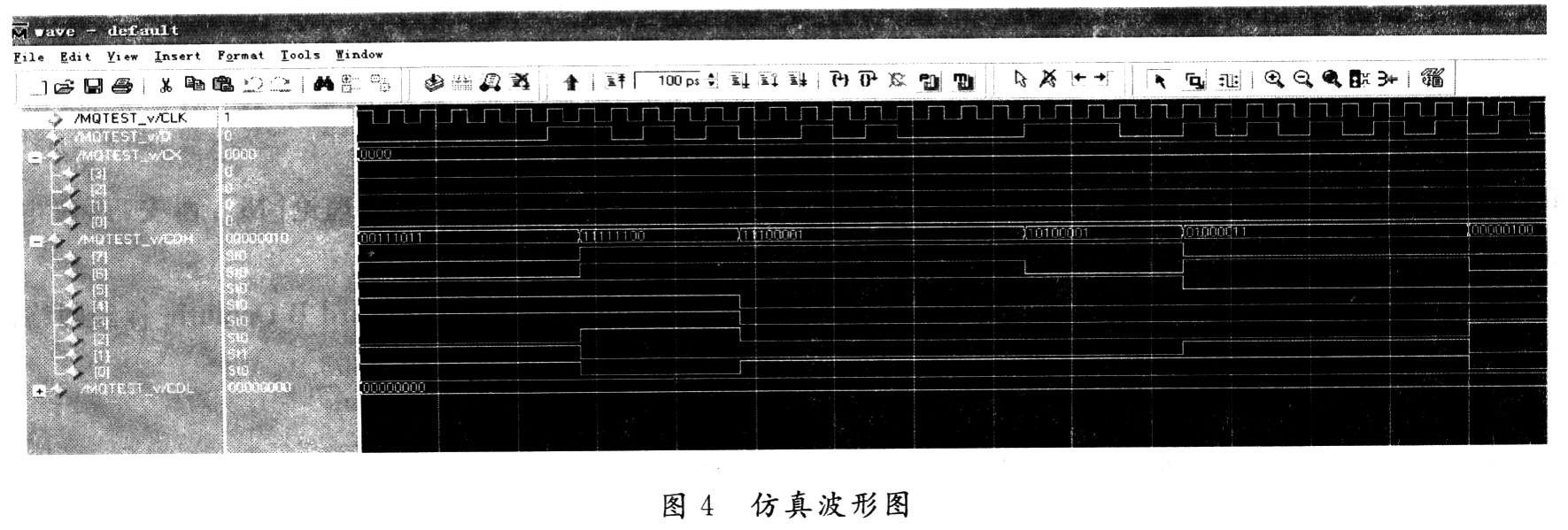

對所實現的MQ編碼模塊用Verilog HDL硬件描述語言進行RTL級描述,在Xilinx ISE 7.1和:Model-sim 6.1平臺下進行功能驗證和時序仿真。按字節輸入測試碼流:00 02 00 51 00 00 00 C0 03 52 87 2A AAAA AA AA 82 C0 20 00 FC D7 9E F6 BF 7F ED 90 4F46 A3 BF,得到結果碼流為:84 C7 3B FC E1 A1 43 0402 20 00 00 41 0D BB 86 F4 31 7F FF 88 FF 37 47 1ADB 6A DF FF AC。得到的結果與理論結果一致,仿真波形如圖4所示。

圖4中D為輸入的測試碼流,CDH為輸出碼流。該設計在Xilinx的XA2C32A-6VP44器件上進行驗證,結果表明,最高工作頻率可達95.47 MHz,較大地提高了編碼速度,能夠滿足JPEG 2000對高速編碼的要求。

4 結 語

綜上所述,為了滿足現在對JPEG 2000高速編碼的需求。在對MQ編碼器的流程及相關算法進行分析后,利用現有FPGA的優勢,在采用三級流水線結構的同時,對編碼進行了優化;經 Xilinx的FPGA器件實現,不僅驗證了該設計在功能上的正確性,同時表明在編碼速度上得到了很大的提高,且最高工作頻率可達95.47 MHz。

評論