基于Verilog HDL的SDX總線與Wishbone總線接口轉化的設計與實現

隨著微電子設計技術與工藝的迅速發展,數字集成電路逐步發展到專用集成電路(ASIC),其中超大規模、高速、低功耗的新型FPGA的出現,降低了產品的成本,提高了系統的可靠性。同時,各種電子產品的復雜度和現代化程度的要求也逐步提高,文中針對機載信息采集系統的可靠性、數據管理的高效性以及硬件成本的需求。設計實現了與Wishbone總線SDX總線的接口轉化,完成了數據采集功能模塊與SDX總線協議之間的數據傳輸。

該設計主要采用硬件描述語言Verilog HDL在可編程邏輯器件FPGA上實現,由于數據采集功能模塊繁多,而Wishbone總線可以與任何類型的ROM或RAM相連,因此需在SDX總線與數據采集模塊中嵌入Wishbone總線,使得整體設計簡單、靈活,且數據能夠高效、快速的傳輸。

1 SDX總線協議

1.1 SDX總線結構

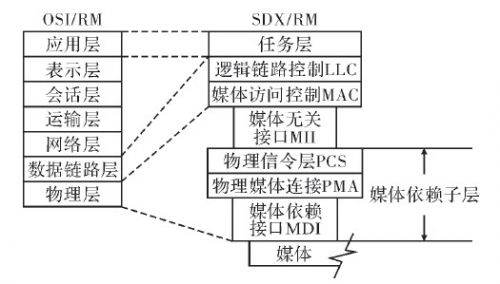

SDX總線屬于非平衡配置的點對點和多點鏈路,站點類型分為主站和從站,其數據傳輸方式為非平衡配置的指令/響應方式。與國際標準化組織ISO制定的開放系統互聯模型OSI/RM相比,參考模型只分為3層:物理層、數據鏈路層和應用層,如圖1所示。

圖1 SDX參考模型與OSI/RM的對應關系

1.2 字格式及其各位場的含義

SDX總線采用面向消息的傳輸控制規程作為通信協議,選用曼徹斯特Ⅱ雙相電平編碼,總線最大傳輸速率20 Mbit·s-1,字長為20位。總線傳輸速率20 Mbit·s-1時,每字占1μs.規定每次傳輸一個消息的過程應包括指令字、數據字和狀態字幾個部分。每種字的字長為20位,有效信息位為16位,每個字的前3位為單字的同步字頭,而最后一位是奇偶校驗位。同步字頭的作用是標識每個字的開始,起字同步作用。奇偶校驗采用奇校驗,在發送端對16位有效位補齊,而在接收端進行奇校,用于檢驗字傳輸中有無錯誤。需要指明的是:無論是何種字類型,各場的數據總是高位(MSB)傳輸在先。

(1)指令字結構。

指令字只能由主站發送,它的內容指明主站要與哪個從站對話,規定了該次數據傳輸的地址方向和服務類型。其格式如圖2所示。

圖2 數據傳輸的地址方向和服務類型格式

方向和服務類型

1~3位:同步字頭(SYN),前1.5位為101,后1.5位為000時標識指令字或狀態字。

4~13位:10 bit遠程模塊地址(RA[9:0]),全0時為廣播地址,其余為各遠程模塊地址。

14位:讀寫控制位R.該位為1時,表明主站要從被尋址的從站中讀取數據;為0時,表明主站要從被尋址的從站中寫入數據。

15~18位:當RA[9:0]為非全0時,EP[3:0]有效。需要強調的是:當RA[9:0]為非全0,端點地址為全0時,該地址為從站的系統管理訪問地址。

19位:狀態字指示位S,當該位為0時,表明有效字為指令字;當該位為1時,表明有效字為狀態字。

20位:奇偶校驗位(P),該字的奇偶校驗位,奇校驗有效。

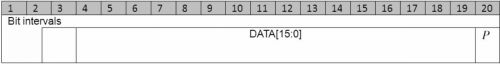

(2)數據字結構。

數據字既可以由主站傳送到從站,也可以由從站傳送到主站。數據字的格式如圖3所示。

圖3 數據字格式

1~3位:前1.5位為101,后1.5位為111時標識數據字。

4~19位:16 bit長數據(DATA[15:0]),高位(MSB)傳輸在先。

20位:奇偶校驗位(P),該字的奇偶校驗位,奇校驗有效。

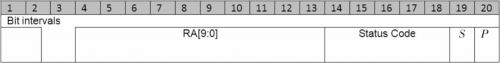

(3)狀態字結構。

狀態字只能由從站發出,是對主站發出的有效命令的應證性信號,是通信中進行差錯控制和流量控制的重要手段。狀態字格式如圖4所示。

圖4 狀態字格式

1~3位:同步字頭(SYN),前1.5位為101,后1.5位為000時標識指令字或狀態字。

4~13位:10 bit從站的地址(RA[9:0])。

14~18位:狀態代碼,表示響應模塊的通信狀態。

19位:狀態字識別位(S),當有效字為狀態字時,該位為1.

20位:奇偶校驗位(P),該字的奇偶校驗位,奇校驗有效。

表1 狀態代碼描述

注釋1,只有滿足下列判據才認為傳輸中不存在錯誤:(1)字有效,這是指都以有效的同步字頭開始,并且除去同步字頭之外其余的都是有效的雙相碼,有效信息是16位,奇偶校驗位一位,且奇校驗。(2)消息有效,這是指在一次傳輸中,如果存在一個數據塊,那么在指令字與數據字之間,在數據字與數據字之間,消息是連續的,不存在任何斷裂的情況。(3)指令有效,這是指在指令字和數據字各場中不存在非法數據,同時發出的數據塊長度應與設置長度相等。如果以上3個判據中有任何一個得不到滿足,則消息錯誤位置位。

注釋2,由于廣播消息格式要求禁止從站發回狀態字,為了解上一個廣播指令是否已被從站有效接收,可使用專門的命令類型讓某個從站發回狀態字,如此位置成1,而且忙位置成0,即說明上一個指令的確是廣播指令,已被該從站有效接收。

2 Wishbone總線協議

Wishbone總線是一種內部總線協議。它可以將片內的各部分以及IP核等連接在一起,用來標準化各個獨立部分的接口,以更加方便地架構SOC(Syctem-on-Chip)系統。其特點是結構簡單、靈活,只需要少量的邏輯門即可實現,同時完全免費、公開。

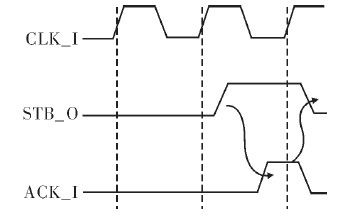

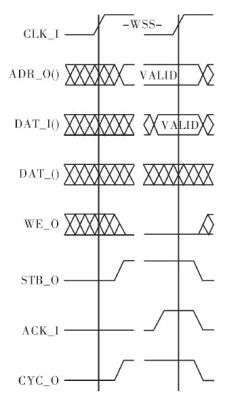

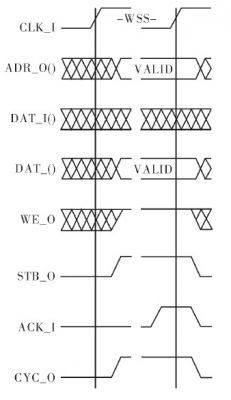

Wishbone總線規范中,使用Master/Slave結構實現靈活的系統設計,MaSTer/Slave有4種互連方式,分別為點對點、數據流、共享總線和交叉互連。且Master和Slave之間使用握手協議,當準備好數據傳輸時,Master使STB_O有效,且一直保持到Slave的響應信號ACK_O,ERR_O,或RTY_O之一有效。Master在每個時鐘的上升沿對響應信號采樣,若該信號有效,則置低STB_O,如圖5所示。

圖5 握手時序

2.1 Wishbone總線基本傳輸周期

Wishbone總線支持完整的普通數據傳輸協議,包括單個讀寫周期、塊讀寫周期等。數據總線寬度為8~64位,地址總線寬度最高可達64位。Wishbone數據總線和地址總線分離,在傳輸上,保持一個地址、一個數據的傳輸結構。以下為Wishbone總線單次讀、寫時序圖。圖6為單次讀周期時序,圖7為單次寫周期時序。

圖6 單次讀周期時序

圖7 單次寫周期時序

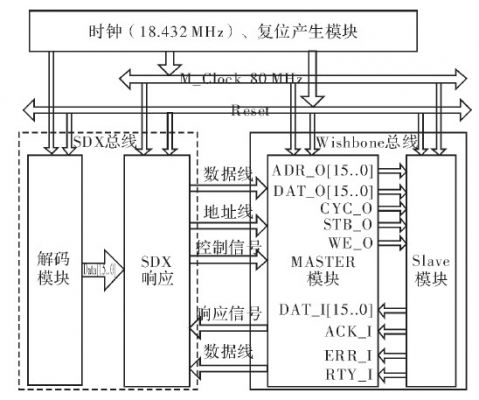

3 系統設計與實現

系統所有控制邏輯均在Altera的CycloneⅢ系列FPGA(EP3C40F)上實現。FPGA的信號線只有系統時鐘、串行輸入數據,由于SDX總線中傳輸數據為曼徹斯特碼型,因此需將曼徹斯特碼解碼為BCD碼同時將串行輸入數據轉化為并行數據,將轉化后標準的16位并行BCD碼輸入SDX模塊對SDX協議響應,將需要數據讀、寫的消息響應同時產生數據讀、寫以及地址信號并發起Wishbone總線操作,實現在Wishbone總線上高效的數據傳輸。Wishbone總線主要使用點對點的互聯方式,將Wishbone總線中Master模塊中的輸出信號直接連接到Slave模塊,其優點是多個數據可以并行處理,從而提高系統的整體數據處理能力。系統的整體設計框圖如圖8所示。

圖8 系統的整體設計框圖

4 仿真結果分析

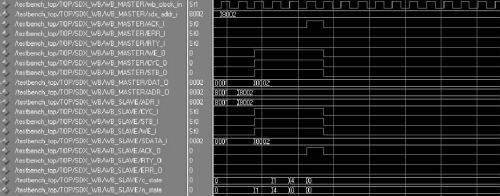

為驗證設計系統的性能,使用Modelsim6.2仿真軟件對系統功能進行了仿真測試。

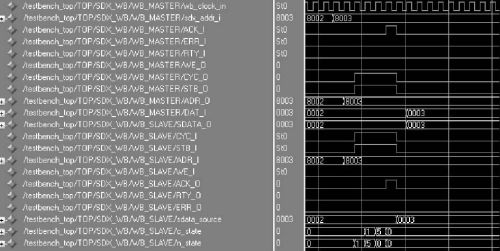

圖9為Wishbone總線寫操作,且為單字寫傳輸,在時鐘上升沿,Master將DAT_O、ADR_O信號放到數據、地址總線上,將CYC_O、STB_O、WE_O置高表示寫傳輸開始,在下一個時鐘沿到達之前,Slave檢測到Master發起的操作,將ACK_O、ERR_O、RTY_O之一置高并傳輸到Master中,若Master檢測到ACK_I為高時,在下一個時鐘的上升沿將CYC_O、STB_O置低表示操作完成,若ERR_I為高,則表示該操作錯誤,取消此操作,進行下一步操作,若RTY_I表示Slave總線忙,則重試。

圖9 Wishbone寫操作仿真圖

圖10為Wishbone總線讀操作,且為單字讀傳輸,在時鐘上升沿,Master將ADR_O信號放到地址總線上,WE_O保持為低,同時將CYC_O、STB_O置高表示讀傳輸開始,在下一時鐘沿到達之前,Slave檢測到Master發起的操作,將ACK_O、ERR_O、RTY_O之一置高并傳輸到Master中,同時將適當的數據傳輸到Master的DAT_I中,若Master檢測到ACK_I為高時,在下一個時鐘的上升沿將CYC_O、STB_O置低表示該次讀操作完成,若ERR_I為高,則表示該操作錯誤,則取消此操作,進行下一操作,若RTY_I表示Slave總線忙,則重試。

圖10 Wishbone讀操作時序圖

5 結束語

討論了基于FPGA的SDX總線與Wishbone總線的接口轉換,并介紹了不同總線的接口標準與時序,通過在Modelsim下的仿真,Quartus中綜合,可下載到FPGA中進行調試,實現了系統的整體性能,從而保證了系統快速、高效的傳輸。

評論