基于CPLD的SDRAM控制器的設計

數據采集處理技術是現代信號處理的基礎,廣泛應用于雷達、聲納、軟件無線電、瞬態信號測試等領域。隨著信息科學的飛速發展,人們面臨的信號處理任務越來越繁重,對數據采集處理系統的要求也越來越高。近年來復雜可編程邏輯器件(Complex Programable Logic Dev ice,CPLD)由于其設計靈活性、更強的適應性及可重構性,結合同步動態隨機訪問存儲器(Synchronous Dynamic Random Access Memory,SDRAM)的高速、大容量、價格優勢,在設計高速實時數據采集系統時受到了廣泛的關注。SDRAM(同步動態隨機訪問存儲器)具有價格低廉、密度高、數據讀寫速度快的優點,從而成為數據緩存的首選存儲介質。

本文引用地址:http://www.j9360.com/article/201706/349072.htm1 SDRAM的基本操作

SDRAM稱為同步動態隨機存儲器,同步是指其時鐘頻率與CPU前端總線的系統時鐘頻率相同,SDRAM可以使所有的輸入輸出信號保持與系統時鐘同步,并且內部的命令的發送與數據的傳輸都以它為基準;動態是指存儲陣列需要不斷刷新來保證數據不丟失;隨機是指數據不是線性依次存儲,而是自由指定地址進行數據的讀寫。由于SDRAM為了提高存儲容量,采用硅片電容來存儲信息,隨著時間的推移,必須給電容重新充電和刷新來保持電容里的數據信息。

在對SDRAM進行存取數據操作之前,首先要對其初始化,即設置SDRAM的普通模式寄存器和擴展模式寄存器,確定SDRAM的工作方式,這些設置包括突發長度、突發類型、CAS潛伏期和工作模式的設置。在SDRAM芯片內部有一個邏輯控制單元,并且有一個模式寄存器為其提供控制參數。因此,每次開機時SDRAM都要先對這個控制邏輯核心進行初始化。初始化過程如圖1所示。

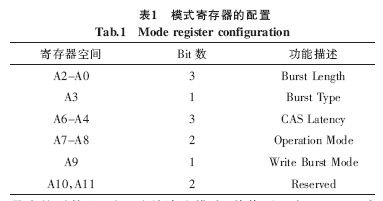

1.1 模式寄存器的設置

Mode Register Set:模式寄存器設置,是指對SDRAM的工作方式做一定義,對寄存器的設置,可以在每次系統啟動時,也可以在每次存取之間進行,當SDRAM掉電時,系統重新啟動后必須重寫模式寄存器。其空間安排如下表1所示:

Burst Length:決定當接受到一個讀寫信號時可以讀取的最大的列數目,對于連續讀取模式,其值可以為1,2,4,8或整頁(full page),當為隔行讀取模式是,其值為1,2,4,8。

Burst Type:決定讀取模式為連續方式還是隔行方式。

CAS Latency:決定當一個讀信號有效到第一個數值在數據線上有效時之間的間隔延遲時間,延遲時間可以設定為1,2或3個時鐘周期。例如:如果延遲時間為m,讀信號在n時刻有效,那么數據將在第m+n個時鐘信號有效,如果相應的讀取時間適合的話,而在m+n-1時刻數據線傳送數據。

Operation Mode:A7-A8表示操作的模式。

Write Burst Mode:當A9=0時,有A0-A2決定的Burst Length適合于讀和寫兩種操作。而當A9=1時,Write只能讀取單一的單元,而不能支持塊操作。

Reserved:A10,A11是保留位,為以后的擴展使用。

1.2 預充電

由于SDRAM的尋址具有獨占性,所以在進行完讀寫操作后,如果要對同一L-Bank的另一行進行尋址,就要將原來有效(工作)的行關閉,重新發送行/列地址。L-Bank關閉現有工作行,準備打開新行的操作就是預充電(Precharge)。預充電可以通過命令控制,也可以通過輔助設定讓芯片在每次讀寫操作之后自動進行預充電。實際上,預充電是一種對工作行中所有存儲體進行數據重寫,并對行地址進行復位,同時釋放S-AMP(重新加入比較電壓,一般是電容電壓的1/2,以幫助判斷讀取數據的邏輯電平,因為S-AMP是通過一個參考電壓與存儲體位線電壓的比較來判斷邏輯值的),以準備新行的工作。具體而言,就是將S-AMP中的數據回寫,即使是沒有工作過的存儲體也會因行選通而使存儲電容受到干擾,所以也需要S-AMP進行讀后重寫。此時,電容的電量(或者說其產生的電壓)將是判斷邏輯狀態的依據(讀取時也需要),為此要設定一個臨界值,一般為電容電量的1/2,超過它的為邏輯1,進行重寫,否則為邏輯0,不進行重寫(等于放電)。為此,現在基本都將電容的另一端接入一個指定的電壓(即1/2電容電壓),而不是接地,以幫助重寫時的比較與判斷。

1.3 刷新

SDRAM之所以稱為同步動態隨機存儲器,就是因為它要不斷進行刷新(Refresh)才能保留住數據,因此它是SDRAM最重要的操作。刷新操作與預充電中重寫的操作一樣,都是用S-AMP先讀再寫。進行預充電操作還要進行刷新的原因:因為預充電是對一個或所有L-Bank中的工作行操作,并且是不定期的,而刷新則是有固定的周期,依次對所有行進行操作,以保留那些久久沒經歷重寫的存儲體中的數據。但與所有L-Bank預充電不同的是,這里的行是指所有L-Bank中地址相同的行,而預充電中各L-Bank中的工作行地址并不是一定是相同的。

目前公認的標準是,存儲體中電容的數據有效保存期上限是64 ms,也就是說每一行刷新的循環周期是64 ms,這樣刷新速度就是:行數量/64 ms。內存規格有4096Refresh Cyeles/64 ms或8192 Refresh Cycles/64 ms的標識,這里的4096與8192就代表這個芯片中每個L-Bank的行數。刷新命令一次對一行有效,發送間隔也是隨總行數而變化,4096行時為0.625 ps,8192行時就為7.812 5 ps。刷新操作分為兩種:自動刷新(Auto Refresh,簡稱AR)與自刷新(Self Refresh,簡稱SR)。不論是何種刷新方式,都不需要外部提供行地址信息,因為這是一個內部的自動操作。

2 系統硬件設計

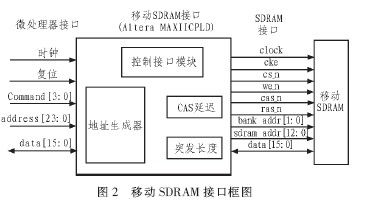

移動SDRAM接口設計包括四個主要模塊,如圖2所示,即控制接口模塊、CAS延遲、突發長度以及地址生成器。下面對這些模塊進行簡要介紹。

2.1 控制接口模塊

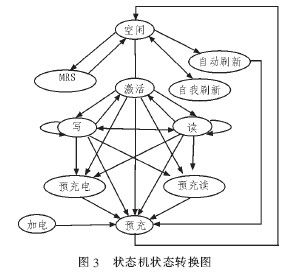

控制接口模塊內部是有限狀態機(Finite-State Machine,FSM),有限狀態機解釋來自微處理器的輸入,把相應的命令和符合時序要求的地址發送給移動SDRAM設備,然后,移動SDRAM設備進入相應的狀態,執行命令。

有限狀態機會綜合考慮存儲器的時序要求,以正確的順序產生各種操作指令,在發出操作指令之前,控制器首先會給出一個讀取使能信號,從數據輸入輸出緩存模塊的地址指令中讀取地址指令。控制接口模塊解碼并寄存主機發送的命令,把解碼后的空閑、寫、讀、刷新、充電和模式設置命令和地址信號送給命令模塊。狀態機的狀態轉換如圖3所示。

2.2 CAS延遲模塊

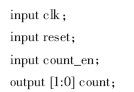

CAS延遲通過模式寄存器配置,CAS延遲模塊的實質是2位遞增計數器,這一計數器監視CAS延時時鐘周期數。它表示讀命令和第一個輸出數據之間延遲的時鐘周期數,延時時鐘周期數可以是二或三個時鐘周期。圖4分別給出CAS=3時的數據輸出時序。

2位遞增計數器的輸入輸出如下:

clk是輸入的時鐘信號來自微控制器,reset輸入的異步復位信號,count_en輸入的計數使能信號,count輸出的CAS延遲數。系統不復位的情況下在計數使能有效時當時鐘上升沿到來CAS延遲增加。

2.3 突發長度模塊

突發長度也使在模式寄存器中設置的,它的內部實質是4位遞增計數器,這一計數器監視讀寫突發工作時的時鐘周期數,原理與2位遞增計數器相同。

突發長度可以是1、2、4或者8,突發(Burst)是指在同一行中相鄰的存儲單元連續進行數據傳輸的方式,連續傳輸所涉及到存儲單元(列)的數量就是突發長度。

2.4 地址轉換模塊

地址發生器將微處理器提供的地址按照要求的格式映射到移動SDRAM設備上。命令模塊接收控制接口模塊輸入的解碼后的命令和刷新控制單元發出的刷新請求命令,產生合適的SDRAM操作命令。

該模塊包含一個簡單的仲裁邏輯單元,仲裁主接口和刷新單元發出的命令,刷新請求的優先級最高。當刷新單元和主接口同時發出命令時,仲裁單元掛起主接口的命令直到刷新操作執行完畢;若主接口發出的命令正在執行時,仲裁單元掛起刷新命令直至正在處理的操作執行結束。仲裁單元接收控制接口模塊發出的命令后,命令產生單元根據接收到的命令產生合適的SDRAM控制信號。命令產生單元基于三個移位寄存器產生正確的時序:第一個寄存器控制SDRAM激活命令的時序;第二個寄存器控制SDRAM讀寫時的時序;第3個用于產生命令延時,以便決定所請求的命令是否執行完畢。它根據狀態分別產生塊和行列地址,并傳送到移動SDRAM設備上。

地址發生器的輸入輸出如下:

clk是系統的主時鐘輸入,addr是輸入的地址信號,pr_state是輸入的當前狀態,這3個信號均由微控制器提供。地址發生器接收來自微控制器的命令,把命令轉換成SDRAM能夠理解的狀態信號,地址發生器根據狀態信號產生相應的地址選擇SDRAM的行或列進行操作。

3 系統的設計與實現

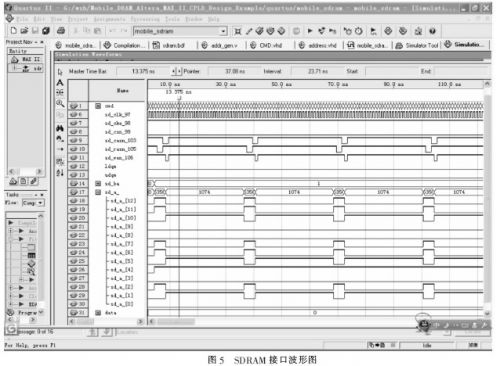

選擇ALTERA公司MAXⅡ系列的EPM1240芯片,用CPLD方式實現SDRAM接口。接口仿真時序圖如圖5所示。

SDRAM接口仿真波形圖如圖5所示,其中sd_clk_97為操作SDRAM的時鐘,sd_cke_98,sd_csn_99,sd_casn_103,sd_rasn_105,sd_wen_106分別為時鐘使能信號,片選信號,列選通信號,行選通信號和讀寫使能信號。sd_ba是SDRAM的2位Bank地址線,sd_a_是SDRAM的13根地址線。data為SDRAM的16位輸入/輸出雙向數據線。

4 結論

在SDRAM的接口設計中,刷新的實現一直是一個關鍵問題。選用CPLD產生控制SDRAM的時序,實現對SDRAM的各種操作。應用Verilog語言和QuartusⅡ軟件實現了SDRAM的接口設計,在QuartusⅡ軟件環境下模擬了STM32系列單片機對SDRAM的讀寫操作時序,讀寫速度達到100MHz,可以在STM32系列單片機擴展64 MBit的SDRAM,其中SDRAM的地址線為13根(行地址線13根,列地址線9根),Bank地址線2根,數據線16根。

評論