FPGA與DSP協同處理系統設計之:典型實例-FPGA片上硬件乘法器的使用

11.5典型實例20:FPGA片上硬件乘法器的使用

11.5.1實例的內容及目標

1.實例的主要內容

在FPGA+DSP系統設計系統中,FPGA經常作為DSP的協處理器來輔助完成一些計算任務。而這些計算工作中最消耗時間的就是乘法運算,因此本實例的主要內容就是幫助讀者學會調用硬件乘法IP核。

2.實例目標

通過本實例,讀者應達到以下目標。

·了解硬件乘法器對算法的加速作用。

·掌握FPGA片上硬件乘法器IP的調用方法。

11.5.2硬件乘法IP的使用方法

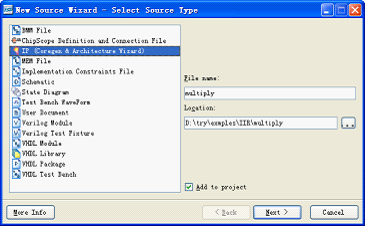

1.生成硬件乘法器

如圖11.12所示,在“NewSource”里面選擇“IP(CoreGenArchitectureWizard)”,在右邊的文件名里面輸入“multiply”,單擊“Next”按鈕,打開如圖11.13所示的IP核類型選擇對話框。

圖11.12新建IP核文件

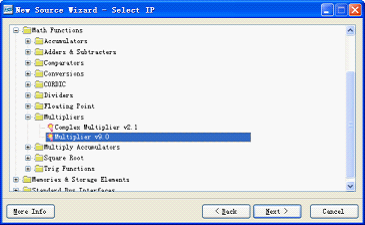

圖11.13新建乘法器IP核

在IP核類型選擇界面里面選擇MathFunctions→Multipliers→Multiplierv7.0,單擊“Next”按鈕,打開乘法器IP核生成向導,如圖11.14所示。

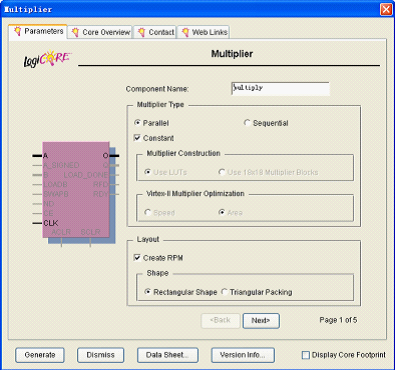

圖11.14乘法器生成向導

在上面對話框里,“ComponentName”是要生成的模塊的名稱。“Parallel”和“Sequential”兩個選項是用來選擇乘法器模式的,選擇并行結構可以加快乘法器的速度,但是同時要多占用一些資源。選擇“Constant”選項我們會發現乘法器的B輸入端口被屏蔽掉了,這時B將作為一個固定輸入。

如果不選擇“Constant”選項,可以在下面的乘法器結構框里面選擇乘法器使用的資源種類,選擇“UseLUTs”將使用片上存儲器資源,選擇“Use18*18MultiplierBlocks”將使用FPGA自帶的DSP模塊。“Virtex-IIMultiplierOptimization”框里面的選項只有在使用Virtex-II族器件的時候才能使用。

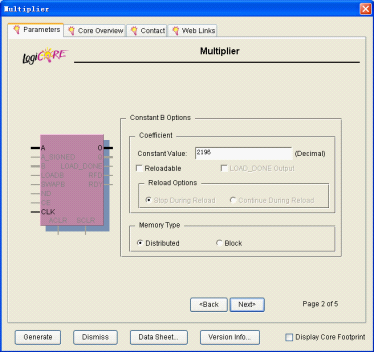

前面選擇了Constant選項,在這個對話框里面就要對乘法器的B輸入進行設置,在ConstantValue后面輸入B端口輸入的數值(十進制),如圖11.15所示。

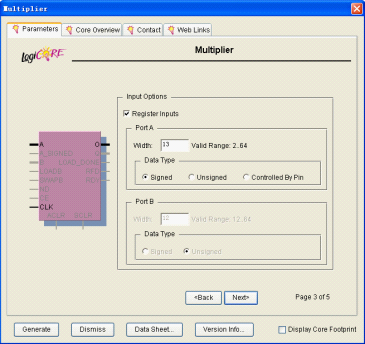

在如圖11.16所示的對話框里面設置輸入口A的位寬和形式。

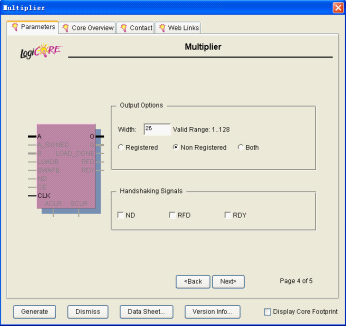

在如圖11.17所示的對話框里面設置輸出口的位寬和是否使用寄存器(使用輸出寄存器的時候由Q口輸出,不使用輸出寄存器的時候由O口輸出)。

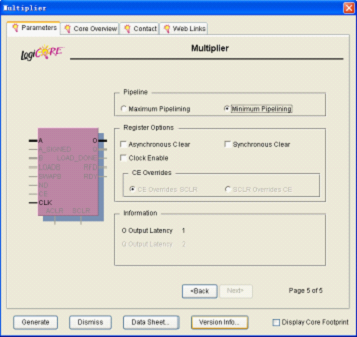

在如圖11.18所示的對話框里面選擇“MinimumPipelining”可以看見在最下面的“Information”框里面的輸出延遲達到最小為1。在“RegisterOption”欄里面可以設置同步復位,異步復位和時鐘使能。

圖11.15設置端口B參數

圖11.16設置端口A參數

圖11.17設置輸出端口

圖11.18其他參數設置

配置完成以后單擊“Generate”按鈕就可以生成乘法器了。

2.使用硬件乘法器

本實例以一個IIR數字濾波的設計為例來演示硬件乘法器的使用方法。直接打開實例的工程文件,如圖11.19所示。其中IIR.v是IIR濾波器的設計文件,test.tbw為測試文件。

圖11.19IIR數字濾波器工程目錄

在IIR.v的文件中,可以看到硬件乘法器的調用方法。

reg[12:0]x1,x2,x3;//定義乘數a

reg[12:0]y1,y2,y3;

reg[12:0]q1,q2,q3;

wire[25:0]mul[10:1];//定義乘法的輸出結果

multiplym0(.clk(clk),.a(x1),.o(mul[1]));//乘法器的調用,輸入為a,輸出為o

multiplym1(.clk(clk),.a(x2),.o(mul[2]));

multiplym2(.clk(clk),.a(x3),.o(mul[3]));

multiplym3(.clk(clk),.a(y1),.o(mul[4]));

multiplym4(.clk(clk),.a(y2),.o(mul[5]));

multiplym5(.clk(clk),.a(y1),.o(mul[6]));

multiplym6(.clk(clk),.a(y2),.o(mul[7]));

multiplym7(.clk(clk),.a(y3),.o(mul[8]));

multiplym8(.clk(clk),.a(q1),.o(mul[9]));

multiplym9(.clk(clk),.a(q2),.o(mul[10]));

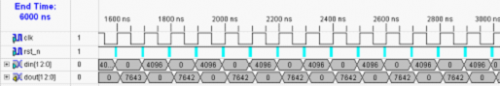

運行仿真后,可以得到輸出結果如圖11.20所示。

圖11.20IIR數字濾波器仿真結果

11.5.3小結

本節對生成和使用FPGA的片上硬件乘法器IP核的方法做了介紹,并通過編譯下載在紅色颶風的開發板上實現了預定功能。

評論