基于FPGA的以太網音頻廣播系統,軟硬件協同

1、課題背景:

課題來源:傳統的廣播系統從傳送音頻信號到廣播點,都須鋪設專門的線路且傳送的事模擬音頻信號,模擬音頻信號抗干擾能力弱,長距離的信號傳輸勢必造成信號的衰減,很難保證聲音質量。同時為了對廣播的方式進行控制,控制信號必須通過另外的控制線來傳送,布線復雜,成本高,施工及維修困難。采用互聯網技術和音頻流技術實現在以太網上以數字化方式傳輸多路音頻信號,使廣播點可以連續、實時地收聽高品質聲音,實現零布線設計。以太網數字音頻廣播系統定位于公用廣播系統,主要應用于車站、機場、碼頭等廣場和學校、大型商場等場合的廣播。主要采用以太網絡技術,將音頻信號以TCP/IP協議形式在以太網上進行傳送和接收,解決了傳統廣播系統存在的音質不佳、易受干擾、維護管理復雜、互動性能差等問題。

需求分析:以太網數字音頻廣播系統可廣泛應用于車站、機場、學校、大廈等場合,具有低失真度、傳輸距離遠、高可靠性、易于安裝布線等優點,可實現實時廣播、自由點播、多路分區播音,具有廣闊的應用前景。以太網作為一種比較成熟的網絡已經廣泛應用于各個領域,其TCP/IP協議也成為事實上的標準網絡協議。傳統以PC機為中心的互聯網應用現已開始轉向以嵌入式為中心。利用FPGA來實現嵌入式系統設計,可以克服定制電路的不足,系統設計更加靈活,易于依不同的需要進行修改。引入軟處理器和嵌入式操作系統,并結合使用LwIP協議棧,能夠降低系統平臺的設計復雜度,可縮短開發周期,提高系統的穩定性和可靠性,軟硬件系部分可分離的設計架構,使得對系統進行修改和重構非常方便。

國內外研究現狀:以太網數字音頻廣播系統定位于公用廣播系統,主要應用于車站、機場、碼頭等廣場和大廈等場合的廣播。主要特點采用當今世界最廣泛使用的以太網絡技術,將音頻信號以TCP/IP協議形式在以太網上進行傳送和接收,徹底解決了傳統廣播系統存在的音質不佳容易受到干擾,維護管理復雜,互動性能差等問題。現有的廣播系統可采用多路定向尋址等技術實現對廣播節目播出、接收的智能化管理,安裝在不同區域的廣播終端可以實時接收廣播數據,突破了傳統廣播系統只能對全部區域進行公共廣播的局限,并且廣播終端可以是移動的(在局域網范圍內),并涵蓋了傳統廣播系統的所有功能,包括音樂播放、實時講話、播送通知和轉播電臺節目等。以太網廣播系統具有良好的可靠性、穩定性、低失真度、易于安裝布線等優點,有著廣闊的發展及應用前景,目前已廣泛應用于校園廣播、大型商場及公司內部廣播。以太網數字音頻廣播系統可實現的功能有:多路分區播音、自由點播、實時插播、移動播音,并可實現遠程管理及監控。

2、功能描述:

功能:本系統將實時錄制的音頻文件利用以太網,以UDP傳輸方式實現實時的信號的發送、接收與播放。

- 實況音頻流服務器:完成模擬語音信號的采集,將模擬信號轉換為數字信號,通過以太網上,發送到終端進行接收和播放,滿足用戶播放實時聲音的需求;

- 基于FPGA的廣播終端:實時接收以太網傳送的數字音頻信號,存儲并轉發至音頻D/A轉換器,將所接收到的數字信號解碼轉換成模擬信號,并輸出到音響設備進行播放。

- 擴展功能:實現多個廣播終端的同時工作;廣播先前已存儲的音頻文件數據。

技術指標:實時傳輸并播放語音信號,可用于遠程管理,具有低失真度,高可靠性的特征。

3、總體設計:

以太網數字音頻廣播系統分為兩個部分:音頻數據采集發送端和音頻數據接收播放端,通過以太網發送實時語音信號實現遠端實時接收和播放功能。

系統硬件結構框架:

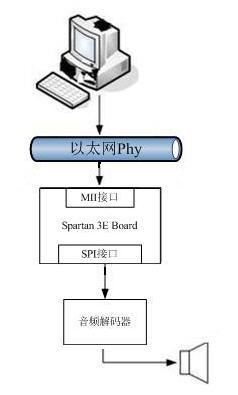

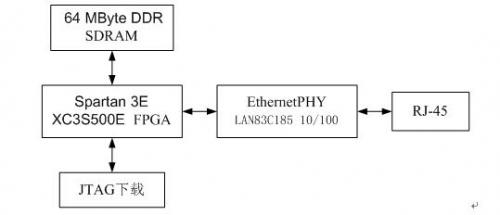

圖1以太網音頻廣播系統框圖

數據流程:

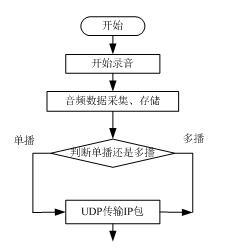

圖2音頻數據采集與發送模塊數據流程圖

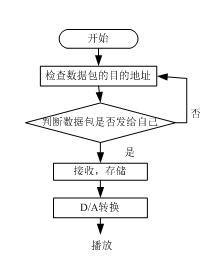

圖3音頻數據接收與播放模塊流程圖

各模塊功能:

①音頻數據采集與發送模塊:通過編程實現語音信號的采集、存儲,根據接收端的IP地址,將語音信號壓縮成廣播包以UDP傳輸方式發送出去。

②音頻數據接收與播放模塊:由Spartan3E FPGA開發板接收以太網傳來的IP包,進行存儲,轉發到音頻D/A轉換器進行解碼,送交音響設備播放。

4、方案論證:

設計思想:采用FGPA模塊接收以太網傳來的數字語音信號,并進行存儲,再通過音頻D/A轉換器將數字信號轉換為模擬信號在音響設備上進行播放。分為兩個部分實現:語音信號采集與發送部分和信號接收與播放部分。①語音信號采集模塊(編程實現)在PC機上進行,然后采用UDP傳輸方式以IP廣播包方式通過以太網發送出去。②接收端是在FPGA開發板上實現語音數據包的接收,并將數據處理后送給音頻解碼芯片進行解碼,轉換成模擬信號進行播放。

方案論證:本系統采用服務器端和廣播終端的架構,由音頻流服務器采集、處理語音信號,通過以太網進行傳輸,然后由Spartan 3E作為廣播終端來接收以太網傳輸的數據,并進行D/A轉換處理后輸送到播放設備。

服務器端的設計:服務器端在PC機上實現,主要完成語音數據的采集、存儲和發送。其中,語音數據的采集和存儲采用WAVE音頻函數來實現。使用WAVE低級音頻函數,可直接與音頻驅動程序交互,通過窗口消息或回調函數來管理音頻數據塊的錄入和存儲,并提供了一個設備無關接口。在使用音頻設備之前,必須打開設備驅動程序,確定系統音頻設備的能力,用完之后必須關閉音頻設備。具體流程如下:

①查詢設備數目。使用waveInGetNumDevs函數來獲取波形輸入設備的個數。只有確定設備存在,才能打開、使用設備。

②打開波形輸入設備。使用waveInOpen函數,該函數打開與指定設備ID相關聯的設備,并以給出指定內存句柄的方法放回打開波形設備的句柄。需要在waveInOpen中指定的一個回調函數或者線程,其作用是在一個數據緩沖區被錄滿后被調用,以對這些數據進行處理,和其他一些相關的操作。

③準備音頻數據塊。在音頻數據錄入之前,必須準備好音頻數據塊。將數據塊傳送給設備驅動程序就可以開始錄音了。使用waveInPerpareHeader函數為輸入緩沖區準備頭部,使用waveInAddBuffer函數添加一個輸入用的數據緩沖區。在用完數據塊后,必須用waveInUnprepareHeader函數來清除對音頻數據塊的準備。

④開始錄音。使用waveInStart函數。

⑤停止錄音,關閉設備。調用waveInReset和waveInClose函數。結束錄音時,在waveInClose之前先調用waveInReset,以清除尚在等待錄音的緩沖區。

錄音過程中,若緩沖區已滿,但錄音還在繼續,為防止語音數據丟失,就需要再加入一個緩沖區進去。考慮到添加緩沖區的處理是有時間延遲的,而音頻對時間很敏感,所以要預先設置好至少兩個數據緩沖區。當一個緩沖區滿時,就調用另外一個,即可保證所錄得的音頻數據不會有斷開的間隔。錄制波形音頻時如果緩沖區已滿,系統將發送MM_WIM_DATA消息給應用程序,程序接收到這個消息后,就可以從消息帶回的參數中得到緩沖區的指針,從而讀出緩沖區的數據,或對數據進行處理,并且該緩沖區的數據讀完后要用waveInAddBuffer函數將緩沖區重新送入設備,循環利用。在本設計中采用兩個緩沖區來存放語音數據。

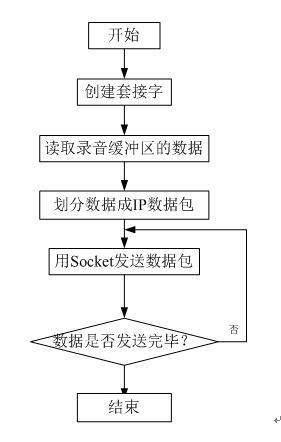

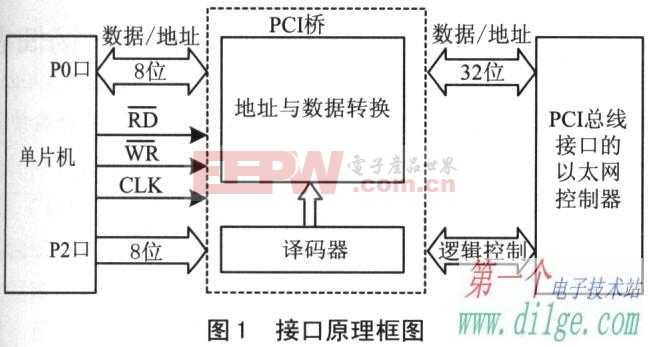

音頻數據的發送:數據發送采用MFC的CSocket類來實現。CSocket類是由CAsyncSocket類繼承而來,與CSocketFile類和CArchive類一起工作來發送和接收數據。軟件實現:當數據緩沖區滿時,需要將已采集到的語音數據通過以太網發送出去,這就要用到Socket網絡傳輸。利用CSocket類創建一個套接字,然后將錄音緩沖區中采集到的語音數據依次封裝成IP包進行發送。語音數據發送流程圖如圖4所示:

圖4 數據發送流程圖

要實現語音信號的實時播放,必須對語音信號進行實時傳輸,所以在以太網上傳輸數據采用UDP傳輸方式。雖然TCP提供一種面向連接的、可靠的字節流服務,可以實現數據的可靠傳輸與出錯重傳,但是這也導致了TCP協議對資源的占用更多。TCP主要適用于對數據的完整性要求很高的網絡傳輸的應用。UDP不一定提供可靠的數據傳輸,它只是把應用程序傳給IP層的數據報發送出去,并不保證它們能到達目的地。由于UDP在傳輸數據報之前不用在客戶和服務器之間建立連接,沒有超時重發機制,所以傳輸速度很快。當某個程序的目標是盡快地傳輸盡可能多的信息,強調傳輸性能而不是傳輸的完整性時,如音頻和多媒體應用,UDP是最好的選擇。

錄音緩沖區的大小為1024個字節,這樣才能避免語音信號丟失,但是在系統終端對語音數據包進行處理的時候,如果數據包過大,則產生嚴重的噪音,因此系統終端要求接收到的語音數據IP包不能過大,設計中終端處理IP包的大小為128個字節,這樣當服務器端錄音緩沖區滿時,需要對數據進行分割,封裝成IP數據包,然后再發送。這里要采用廣播地址。在局域網內實現廣播,只需將IP地址中主機部分設為全1,本設計中IP廣播地址設為192.168.1.255。

廣播系統可以有多個廣播終端,既可實現全區域的廣播,還可以實現局域廣播,即對指定的終端進行廣播。要實現對指定的終端的廣播,服務器端必須知道各個終端的IP地址,然后才能實施對應的廣播。考慮到終端數量不多而且是在相對固定的局域網中,采用靜態IP地址分配,其特點是IP地址對每一臺計算機都是固定的。可以將各個終端的IP地址寫入一個配置文檔,如:“IPADDR.txt”。服務器首先讀取配置文檔中的IP地址,將終端IP地址與服務器端的終端號進行綁定,然后每次選定廣播終端時也得到了對應終端的IP地址,即可實現區域廣播了。另一方面,也必須使終端能夠判斷出所接收到的IP包是不是發給自己的。是則存儲并轉發給音頻解碼器;不是則丟棄。可以在IP包頭進行設置,廣播終端根據IP數據包包頭來判斷數據是否發給自己。IP數據包采用廣播包的形式進行數據傳輸。

可以將廣播的內容保存下來以便在以后可以使用。本設計對每次廣播的內容進行了存儲,存儲文件設置為Record.wav。每次錄音緩沖區滿時,即將IP廣播包發送出去,同時對其進行存儲,在文件末尾將數據寫入文件,并改變文件的長度。

廣播終端的設計:要實現FPGA與以太網的通信,可以將FPGA終端設計為一個嵌入式系統,即采用基于FPGA的嵌入式系統實現以太網的互聯。可以利用Xilinx的MicroBlaze微處理器軟核和相應的外設,通過Xilinx EDK搭建系統所需的軟硬件平臺,完成嵌入式系統的設計。FPGA控制著以太網物理層的操作,內置一個符合MII標準的以太網控制器MAC,FPGA通過MII連接到開發板上的LAN83C185 Ethernet PHY,以便和以太網進行通信,接收以太網發送給本終端的IP數據包,進行存儲,并轉發給音頻解碼芯片進行播放。

硬件部分:

硬件電路結構分為兩個部分,基于Spartan 3E開發板的音頻數據接收模塊和音頻解碼模塊。

Xilinx Spartan 3E開發板上的XC3S500E FPGA作為控制芯片,在EDK中配置MicroBlaze微處理軟核作為CPU,配置FPGA內置Ethernet MAC IP核(MAC是EDK開發平臺的一部分),外部存儲器采用DDR SDRAM,采用Xilkernel嵌入式操作系統和LwIP協議棧,構建一個完整的嵌入式系統實現以太網互聯。

硬件結構圖如圖5所示:

圖5 硬件結構圖

MicroBlaze微處理器軟核是可嵌入在FPGA中的RISC處理器軟核,采用哈佛結構的32位指令和數據總線,具有運行速度快、占用資源少、可配置性強等優點,支持CoreConnect總線,和其他外設一起可以完成可編程片上系統的設計。特征:32個32位通用寄存器和2個專用寄存器;32位指令系統,支持3個操作數和2種尋址方式;分離的32位指令與數據總線,符合IBM的OPB總線規范;通過本地存儲器總線(LMB)直接訪問片內塊存儲器;具有高速的指令和數據緩存(cache),三級流水線結構;具有硬件調試模塊;帶8個輸入輸出快速鏈路接口。

EDK開發流程:

EDK:所有的系統設計包括后面的應用程序開發設計均在嵌入式開發套件軟件EDK內完成。EDK(Embedded Development Kit)是針對FPGA內部32位嵌入式處理器開發而推出的開發套件,EDK工具包中集成了硬件平臺產生器、軟件平臺產生器、仿真模型生成器、軟件編譯器和軟件調試等工具,利用其集成開發環境XPS(Xilinx Platform Studio)可以很方便、快速地完成嵌入式系統開發的整個流程。EDK以IP核的形式提供LMB、OPB總線接口、外部存儲控制器、SDRAM控制器、UART中斷控制器、定時器及其他一些外圍設備接口等資源,利用這些資源可以構建一個完善的嵌入式處理器系統。這些IP核都有相應的設備驅動和應用接口,使用者只需利用相應的函數庫,就可以編寫自己的應用軟件和算法程序。

首先完成系統硬件平臺的搭建和相應的驅動配置。在EDK的XPS中先使用基本的系統生成向導BSB,自動生成MicroBlaze系統的基本構架,設置處理器時鐘頻率為50MHz,總線時鐘頻率為50MHz,設置片上讀寫調試模塊為調試接口。生成結束時XPS可以自動地生成對硬件進行例化的微處理器硬件規范文件MHS和描述軟件系統結構的微處理器軟件規范文件MSS以及一些相關的文件,對這兩個文件進行修改,以便完成對系統的優化。生成的系統經過綜合、布局布線無誤后生成bit文件下載到目標開發板上。

系統軟件平臺:

在硬件系統建立后,利用XPS的集成工具,完成網標的生成核軟件的配置,存儲器地址映射默認由系統自動生成,自動分配地址。

為了能夠更好地管理系統資源,選擇Xilinx 精簡嵌入式操作系統Xilkernel,它是一種可定制的簡單高效系統,能夠與用EDK形成的硬件系統緊密結合,并支持可移植操作系統界面POSIX開放結構。Xilkernel系統的設置可以在開發環境EDK中手動設置,需要配置調度原則為SCHED_RR(simple round-robin scheduling),并設置一個靜態線程用于初始化要使用的LwIP協議棧。Xilkernel操作系統通過移植LwIP協議棧就可以實現基于Socket的網絡通信。LwIP協議棧支持服務器模式和客戶機模式,提供RAW和Socket兩種API,是目前使用最為廣泛的TCP/IP協議棧。本設計中采用Socket API模式,利用Libgen工具對LwIP庫進行鏈接和編譯。

在Xilkernel中設置一個靜態線程serverThread來初始化LwIP協議棧,即可以使用協議棧提供的功能函數。調用LwIP的線程生成函數sys_thread_new()生成并啟動一個線程。在這個線程中設置開發板硬件的MAC地址、網關、IP地址和子網掩碼等參數。分配內存空間開發板的網絡接口,再將MAC地址、網關、IP地址等信息添加到內存空間,初始化網絡接口。

在設置好系統的軟件平臺后就可以編寫各種關于網絡傳輸控制的應用程序了。使用標準C語言進行應用程序開發,編寫相應的算法軟件,將編寫的程序代碼利用mb-gcc編譯工具,根據系統軟件環境,生成.ELF文件,完成系統功能的實現,通過JTAG接口連到目標開發板上,將軟件程序下載到系統中進行調試。

程序設計思路:

終端同樣需要Socket編程,以接收從以太網傳送來的音頻數據。為了實現數據的順序存儲與轉發,定義一個循環隊列來存儲接收到的數據。

struct Queue

{ int front; //隊首

int rear; //隊尾

int count;

char DATA[QueueSize][SIZE];

};

初始化一個Socket,將它與IP地址和端口號綁定,然后開始監聽網絡,一旦監聽到網絡上有數據到來,就生成一個線程去處理。先定義一個結構體struct CSTRING,包含目的終端的IP地址,終端通過判斷其成員變量,與自己的IP地址進行比較。若有成員變量與自己的IP地址相同,則存儲數據包中數據到循環隊列中。還需要定義一個接收數據結構體struct RECVBUFFER,來存放所接收到的音頻數據,并且struct CSTRING IP作為它的一個成員用于判斷目的IP包地址。

struct RECVBUFFER

{ INT32 count;

struct CSTRING IP; //用來判斷IP包是不是發給自己的

INT8 recvbuffer[SIZE]; //接收數據緩沖區

}RecvBuffer; //接收數據的結構體

Socket接收函數接收數據到一個數據緩沖區,然后對數據包進行判斷,根據IP數據包頭判斷該包是不是發給自己的,若是,將數據放入循環隊列以待轉發,否則丟棄。在以太網范圍內實現音頻廣播,終端以太網控制器IP地址要和服務器處在同一個網段內,設置本地IP地址和端口號,并綁定到服務器地址。

廣播終端的實現還需要連接一個音頻D/A轉換器,將開發板上輸出的數字音頻信號轉換為模擬音頻信號。在本設計中采用VS1003音頻解碼器。VS1003是一個單片MP3/WMA/MIDI音頻解碼器和ADPCM編碼器,包含一個高性能、自主產權的低功耗DSP處理器核VS_DSP,工作數據存儲器,串行的控制和數據接口,4個常規用途的I/O口,一個UART,一個高品質可變采樣率的ADC和立體聲DAC,還有一個耳機放大器和地線緩沖器。VS1003通過一個串行口來接收輸入的比特流 。數據流程:首先音頻數據從SDI接收并解碼,若其SCI_AIADDR非零則應用代碼從寄存器所指向的地址開始執行;然后數據流是否經過低音/高音增強器,取決于SCI_BASS寄存器;之后數據流向音量控制單元,同時拷貝數據進音頻FIFO,鎖存住數據,通過音頻中斷將數據送進采樣率變換器和DAC;采樣率變換器將所有不同的采樣率變為XTALI/2或128次最高可用采樣率;過采樣的輸出被片上的模擬濾波器進行低通濾波;濾波后的信號前往耳機放大器。

VS1003通過一個串行接口來接收輸入的比特流,所以要實現VS1003與FPGA的互連,還需要在開發板上模擬實現SPI總線接口。SPI——串行外設接口總線系統是一種同步串行外設接口,允許MCU與各種外設以串行方式進行通信、數據交換。在內部硬件實際上是兩個簡單的移位寄存器,傳輸的數據為8位。一般使用4條線:串行時鐘線(SCK)、主機輸入從機輸出數據線(MISO)、主機輸出從機輸入數據線(MOSI)和低電平有效的從機選擇線/SS,即可實現與具有SPI總線接口功能的各種I/O器件進行通信,而擴展并行總線則需要8根數據線、8~16位地址線、2~3位控制線,因此采用SPI總線接口可以簡化電路設計,提高設計的可靠性。在本設計中,從器件是vs1003音頻解碼器,在主器件產生的從器件時能和移位脈沖作用下,才能接收主機傳送的數據,其數據傳輸格式是高位(MSB)在前,低位(LSB)在后。

FGPA為主控芯片,vs1003為從芯片,選擇開發板上與FPGA連接的Hirose FX2擴展連接器模擬實現SPI接口,實際上是對SPI時序的模擬。FPGA的I/O口與Hirose FX2擴展連接器相連,雙向I/O口都可以驅動或接收信號。選擇FX2連接器上的FX2_CLKOUT模擬實現SPI接口的時鐘輸出線,一個I/O(如FX2_IO1)口模擬實現MOSI數據線,一個I/O(如FX2_IO2)口模擬實現/SS選擇線。SPI數據傳輸模式采用模式0(CPOL=0,CPHA=0)。數據傳輸流程:首先主控芯片FPGA要使能相應的/SS信號(FX2_IO2,直到數據發送完畢),通知從芯片即VS1003數據傳輸要開始了;主控芯片產生SPI時鐘脈沖,將數據從每個時鐘下降沿發送出去,每次發送1bit,從高位開始發送;待數據發送完畢,主控芯片復位/SS信號,SPI傳輸結束。

系統設計中的難點與重點:

(1)音頻信號的采集;

(2)IP廣播包的UDP傳輸;

(3)廣播終端對音頻信號的接收;

(4)FPGA控制芯片與VS1003解碼芯片之間的數據傳輸。

5、項目預期成果:

實現音頻數據的以太網上實時UDP傳輸,同步播放,支持多個廣播終端同時工作,實現網絡廣播功能。

評論