基于 DSP 的電子負載----功率電路設計和采樣電路設計

3.2.1功率電路

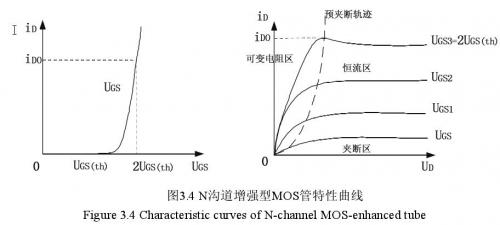

電子負載的功率耗散部分是一個N溝道的功率場效應管MOSFET.當一個電壓施加在MOSFET的兩端時,N溝道里面的正負電離子分布也會跟著改變,正離子的濃度會減少,電子的濃度會增加。當電壓夠強時,接近柵極端的電子濃度會超過電洞。這個在P型半導體中,電子濃度(帶負電荷)超過正離子(帶正電荷)

濃度的區域,形成所謂的導電溝道。如果在其柵極(G)和源極(S)之間加上一個正向電壓(稱為門極電壓),在正向電場作用下,稱耗盡區變薄,溝道變窄,漏極電流變大。場效應管為電壓型控制元件,開關頻率高,具有正的溫度系數,工作在轉移特性曲線區時,門極與漏源極之間的伏安特性可以看作是一個受柵極電壓控制的可變電阻。

電子負載系統設計要求的電流工作范圍是:0~16A(高檔位),0~3A(低檔位);電壓工作范圍是:0~60V(高檔位),0~5V(低檔位)。電阻工作范圍是:0.1-100Ω。設計時要根據系統的設計參數,留取一定裕量,并考慮實驗過程中的不確定因素。

圖3.4(a)、(b)所示分別為N溝道增強型MOS管的轉移特性和輸出特性曲線,它有三個工作區域:可變電阻區、恒流區及夾斷區,如圖中所標注。

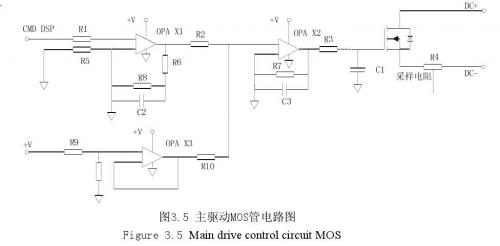

電子負載的主電路中功率耗散元器件為N-MOS,MOSFET管上需要加上散熱片,采用空氣冷卻方式解決大電流經過MOS管導致的溫升。主電路采用OPA運算放大器和MOSFET串連,運算放大器上加+V的供電電平,X2的輸出端為功率管MOSFET提供一個門觸發電壓,R3是一個門電阻,它的作用是門限流和避免噪聲導致的MOSFET的自激振蕩,C1為控制環提供補償。X3輸出電壓經X2將輸出電壓鉗位在MOSFET開啟電平(大約在3.6V)以下,以防止其工作。當連接測試電源并且超過3.6伏的鉗位電壓時,運算放大器輸出的調節幅度比可以設定的調節范圍小得多,這樣響應可以更快并且開啟可控。被測的輸出電源的連線在上圖中用DC+和DC-標示出來。驅動電路如圖3.5所示。

3.2.2電流和電壓采樣電路

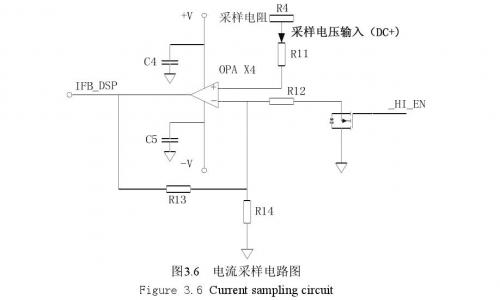

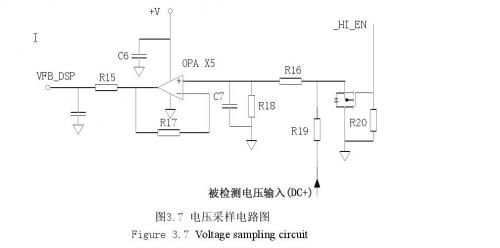

A/D是檢測和測量負載電流和電壓的重要器件,為了讓負載準確工作在不同方式下,設計中對被測電源的輸出電壓和MOS管的電流進行實時采樣。采樣AD選用TMS320LF2812自帶的具有12位精度的逐次逼近型A/D,采樣精度可達5V/4096≈0.0025V.A/D的輸入口為高阻態,輸入阻抗極大,容易被干擾,為提高抗噪聲能力并且保護A/D不被高于3.3V的電壓輸入所損壞,增加了RC濾波器,可以將大部分紋波和高頻噪聲有效的濾除。根據TI的數據手冊,2812的AD采樣電路精度不是很高,一般只有2%.需要對AD采樣進行軟件校正,軟件校正后的精度可以達到0.5%,這在第五章里將有詳細的論述。此外,根據TI的應用手冊,A/D的線性度在0.3V~2.7V時轉換效果最好,因此設計AD采樣電路時,盡量將所要采樣的信號變換到AD采樣線性度較好的區間。

根據設計的需要,采樣電路包括電壓采樣電路和電流采樣電路,從功率電路采集實際工作電壓和電流,反饋到DSP的AD口,實現自動調節。

電流采樣電路中,負載電流經過采樣感應電阻R4,由具有差分放大器作用的R11、R12、R13、R14組成的運算放大器X4檢測,差分放大器由這個電流產生一個電壓,由X4的負相端檢測,其中_HI_EN信號由DSP給出的場效應管開啟電壓,高低檔位選擇信號,低檔位時_HI_EN是高電平,Y1導通R12和R14處于并聯狀態,R13和并聯的R14、R12分壓。高檔位時_HI_EN是低電平,Y1處于截止無窮大電阻狀態,R13和R14串聯分壓。這個信號X4的正相檢測,與0~5V的參考電平進行比較,相應成比例的的電流就是0~16A(高檔位)、0~3A(低檔位)。圖3.6所示為電流采樣電路原理圖。

電壓采樣電路中,電壓信號經過R19和R16進入X5的正相檢測端,由具有差分放大器作用的R16、R17、R18、R19組成的運算放大器X5檢測,差分放大器產生一個電壓信號,由X4的負相端檢測,其中_HI_EN信號由DSP給出的場效應管開啟電壓,高低檔位選擇信號,高檔位時_HI_EN是高電平,Y2導通R16和R19處于串聯狀態,R16和R19串聯分壓。低檔位時_HI_EN是低電平,Y2處于截止無窮大電阻狀態,R19和R20并聯,R16和并聯的R19和R20組成串聯電路,進行串聯分壓。這個信號X5的正相檢測,與0~5V的參考電平進行比較,相應成比例的的電流就是0~5V(低檔位)、0~60V(高檔位)。圖3.7所示為電壓采樣電路原理圖

3.3電源電路設計

電子負載電源設計包含兩個方面的內容,供電電源電壓和電源管理。

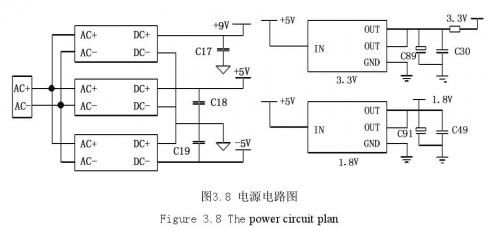

電源電壓設計是根據電子負載系統需求來進行電壓分配,電子負載系統中,DSP芯片工作電壓是3.3V,內核電壓1.8V,信號板上高低檔位選擇電壓信號、恒壓恒流使能信號均為3.3V,輸入電壓范圍在5~12V之間,輸出線性誤差在0.2%以內,可以在120度下的溫度穩定的工作。C89,C91采用穩定耐用的貼片鉭電容,鉭電容使用溫度范圍寬,耐高溫,絕緣電阻高,漏電流小,容量誤差小,等效串聯電阻小,高頻性能好,和發熱量巨大的負載板長時間在一起也可以保持良好的性能。

DSP控制板采用用5V直流電源供電,負載板直接連接市電220V電源,測試電源連接市電。在調試時為了減少信號板的模擬電路對DSP控制板的數字電路造成不必要的噪聲影響,首先DSP控制板上電,其次功率板上電,最后測試電源再上電。電源電路如圖3.8所示,左側是給電子負載信號板供電的電壓(+9V,+5V,-5V),右側是給控制板供電電壓(3.3V,1.8V)。

3.4信號板設計

(1)地線的設計

電子負載系統中有兩種地線:模擬地和數字地。接地有兩方面好處,增強系統的抗干擾能力和保障測試人員的安全。模擬信號和數字信號最終都要回流到地,數字信號變化速度快,從而在數字地上的噪聲就會很大,如果模擬信號是需要一個無噪聲的地參考,就不能把模擬地和數字地混在一起,數字地的噪聲會影響到模擬信號。電子負載電路板上既有高速邏輯電路,又有線性模擬電路,屬于數模混合電路,應使它們盡量分開。大檔位時的負載電流流過地線上的回路時,信號板上電阻可能會有幾百毫伏的電壓降而引起的測量誤差,所以采用加大引出端的接地面積之外,對于MOS管主電路與控制電路之間通過RC電路濾波去除噪聲。

(2)元器件的布局

在元器件的布局方面,進行電路板合理分區,把相關的元器件盡量放得靠近一些。如:晶振、時鐘發生器、CPU的時鐘,輸入時都容易產生噪聲,放置的時候放在一起。大功率器件MOSFET管遠離密集的電路,放在了電路板邊緣。模擬電壓輸入、參考電壓端盡量遠離數字電路信號線,布線時切忌90度折線造成的高頻噪聲發射。所有平行信號線之間留有一定的間隔,以減少串擾。有相距較近的信號線時,在線與線之間走一條接地線,這樣可以起到屏蔽的作用。

(3)閑置端口的設置

TMS320LF2812有56個數字量輸入輸出口,一部分為專用的IO口,大部分為通用口,可以通過配置相應的寄存器來設置IO口的方向,對于設計中剩余的閑置的IO端口都定義為輸出口。

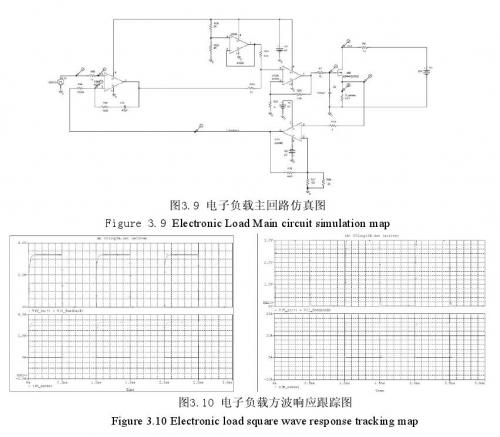

(4)信號板主回路仿真測試

為對主回路進行測試,在PSspic環境下搭建了電子負載主回路,如圖3.9所示,并對負載電流進行階躍響應仿真測試,為了測試準確性,分別對3.3A和16A的負載電流進行方波跟蹤,仿真測試結果為3.10圖,可以看出主電路良好的方波跟蹤性比較讓人滿意。較讓人滿意。

評論