100MHz 數字存儲示波表樣機的研究與試制----DSP 芯片的連接與配置(一)

第四章DSP芯片的連接與配置

本文引用地址:http://www.j9360.com/article/201706/348241.htmDSP(Digital Signal Processor)作為可編程數字信號處理專用芯片是微型計算機發展的一個重要分支,也是數字信號處理理論實用化過程的重要技術工具。隨著微電子技術和數字信號處理技術的飛速發展,DSP的性能價格比不斷提高,并由于其體積小、成本低、易于產品化、可靠性高、易擴展及方便地實現多機分布式并行處理等性能,在產品開發和科學研究的各個領域獲得了越來越多的廣泛應用。

DSP的特點主要有以下幾個方面:

◇高速、高精度的運算能力

DSP的實際應用所面臨的最突出的問題就是算法的實時實現問題。無論模擬硬件功能的實時數字化軟件實現,還是特殊算法的實時處理等,都要求高速、高精度的運算能力。因此,通常DSP都具有較快的指令執行周期、并行的內部指令執行流水線,以及內部集成的硬件乘法器,使運算速度更快、運算精度更高。

◇強大的數據通信能力

數字信號處理往往涉及較大的數據吞吐量,因此,DSP都具有DMA、串行/并行以及多CPU之間的通訊方式。

◇靈活的可編程性

通用DSP完全是通過編程來實現數字信號處理功能,因此,DSP配置片內RAM和ROM,也可方便地擴展程序、數據及I/O空間。同時,允許ROM與RAM之間的直接數據傳送。時鐘頻率可通過內部鎖相環電路調節。系統各種特性的器件軟硬件控制為編程的方便靈活提供了充分的空間。

◇低功耗設計

DSP可以工作于省電狀態,節省了能源。

目前,DSP的發展非常迅速。硬件結構方面主要是向多處理器的并行處理結構、便于外部數據交換的串行總線傳輸、大容量片上RAM和ROM、程序加密、增加I/O驅動能力、外圍電路內裝化、低功耗等方面發展。軟件方面主要是綜合開發平臺的完善、使DSP的應用開發更加靈活方便。以下我們將對本項目中所選用的DSP芯片和某些所用到的芯片重要引腳的具體連接方式以及DSP地址空間的分配作詳細的介紹。4.1 TMS320VC5416介紹

本項目中,我們選用了TI公司型號為TMS320VC5416的數字信號處理芯片。該芯片是16位定點DSP.它采用修正的哈佛結構,程序與數據分開存放,內部具有8條高度并行的總線。片上集成有在片的存儲器和在片的外設以及專門用途的硬件邏輯,并配備有強大的指令系統,使得該芯片具有很高的處理速度和廣泛的應用適應性。再加上采用的模塊化設計以及先進的集成電路技術,芯片功耗小,成本低,自推出以來已廣泛應用于各種專門用途的實時嵌入式系統和儀器中。下面對該芯片的結構體系與關鍵特性予以簡單的介紹。

它的硬件結構基本上分為3大塊:

1. CPU

●先進的多總線結構,具有1條程序存儲器總線、3條數據存儲器總線和4條地址總線。

●40位的算術邏輯單元(ALU),包括2個獨立的40位累加器、40位移位寄存器

●2個地址生成器

●17×17Bit的并行乘法器

2.存儲器系統:

●16K×16Bit的片內程序ROM

● 128K×16Bit的片內RAM,包括8塊8K×16Bit的片內雙訪問DARAM和8塊8K×16Bit的片內單訪問SARAM. 3.在片的外設與專用硬件電路:

●16位可編程定時器

●3個多通道緩沖串口(McBSP)

●8/16Bit并行主機接口

●在片的鎖相環時鐘發生器

另外,還具有符合IEEE1149.1標準的在片仿真接口,可與主機連接,用于開發應用系統芯片的仿真。

4.2芯片引腳連接方式

本節將結合實際項目中引腳的具體連接方式對TMS320VC5416某些重要的引腳作詳細的介紹。

4.2.1數據信號引腳

1.地址信號線A[22..0]

地址信號線的A15~A0可以尋址外部程序、數據空間和I/O空間。而地址線的高7位A22~A16是專門用來尋址外部程序空間。

2.數據線D[15..0]

數據線是CPU核與外部程序、數據空間和I/O空間之間數據傳送的通道。

4.2.2初始化、中斷、復位操作引腳

1.用戶輸入中斷引腳INT[3..0]

該引腳為輸入引腳,低電平有效,是專門為用戶設置的外部中斷輸入。這些中斷可以通過對中斷屏蔽寄存器IMR的設置來調整它們的優先級和決定是否屏蔽該中斷。項目中我們選用了INT0、INT1、INT2這三個中斷通道。

2.不可屏蔽中斷引腳NMI

該引腳也是專門為用戶設置的外部中斷輸入,低電平有效。但它與INT[3..0]的區別是:NMI是不受IMR屏蔽寄存器影響的,它是不可屏蔽中斷。項目中,我們直接把它接為高電平。

3.復位引腳RS

該引腳為輸入引腳,低電平有效。當復位引腳有效時,DSP中斷執行程序,強制程序指針指向0FF80h.項目中,該復位信號由FPGA2提供。

4.工作方式選擇信號引腳MP/MC

DSP有兩種工作模式:微型處理器模式和微型計算機模式。當MP/MC置為高電平時,微處理器模式被選擇;低電平時,微型計算機模式被選擇。當工作在微型計算機模式下時,DSP片內ROM映射到程序空間的高16K字地址;工作在微處理器模式時,片內ROM不映射到程序空間。項目中,我們在DSP上電復位時,將MP/MC設置為高電平,讓它處在微處理器工作模式,直接從外部FLASH的0FF80h地址開始執行程序。該程序模擬DSP內部的Bootloader功能:首先重新設置PMST、ST0、ST1等DSP配置寄存器,并將自己復制到內部RAM中繼續運行;然后再將用戶的主程序、用戶設定的中斷向量表從外部FLASH復制到內部RAM中,第三步將DSP的工作模式設置為微型計算機工作模式,并且在程序最后遠跳轉到地址1FF80h處,而該地址正是內部RAM保存的用戶設定的中斷向量表起始地址,在該處又有一條跳轉指令使得程序最終跳轉至用戶主程序的起始地址。

4.2.3通用I/O端口引腳

1.外部標志輸出引腳XF

該引腳為輸出引腳。項目中,我們主要用此引腳來實現DSP,FPGA2分時占用SRAM3地址和數據總線的控制信號。

4.2.4存儲器控制信號引腳

1.數據、程序、I/O空間選擇信號引腳DS、PS、IS

DSP的數據空間、程序空間、I/0空間是分開的。當DS為低電平時,數據空間被選擇;PS為低電平時,程序空間被選擇;IS為低電平時,I/O空間被選擇。項目中,這三個選擇信號主要與DSP輸出的地址信號配合,產生相應空間外部擴展的選擇信號。

2. DSP讀寫信號引腳R/W

此信號主要表示當DSP與外部器件進行數據交換過程中數據的傳送方向。

3.外部數據存儲器選通信號引腳MSTRB

當有外部總線訪問數據和程序空間時,該信號為低。項目中,該信號與DSP的讀寫信號配合產生外部擴展數據和程序空間的讀寫信號。

4. I/O設備選通信號引腳IOSTRB

當外部總線訪問DSP的I/O空間時,IOSTRB為低電平。項目中,該信號與DSP的讀寫信號配合產生外部I/O空間的讀寫信號。

5.時鐘輸入引腳X2/CLKIN

當不選用DSP內部時鐘信號時,此引腳作為外部時鐘的輸入引腳。項目中,我們在此引腳加上了10MHz的標準頻率信號。

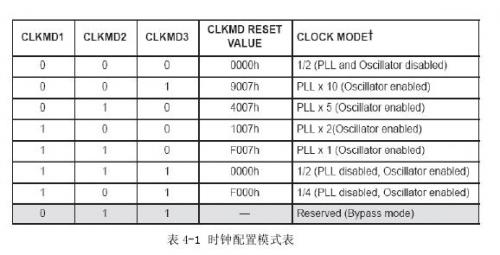

6.時鐘模式選擇引腳CLKMD1、CLKMD2、CLKMD3

DSP有內部時鐘、外部時鐘、PLL三種時鐘模式。這三個引腳主要用來在DSP復位時初始化時鐘模式選擇寄存器。寄存器中的內容定義了時鐘的配置模式。具體的配置模式如表4-1.

項目中,我們選則第三種配置方式,即CLKMD1、CLKMD3接為低電平,CLKMD2接為高電平。

4.2.5多通道緩沖串行接口(McBSP)

TMS320VC5416中共有3個多通道緩沖串行接口,它主要完成DSP與配套外設之間的串行通信。它包括的引腳有:

1.接收串行數據時鐘信號BCLKR

它主要為DSP接收外部串行數據時提供數據轉移時鐘。

2.接收串行數據線BDR

它是外部串行數據輸入端。

3.接收串行數據幀同步信號BFSR

它主要的作用是保證接收串行數據的同步。

4.輸出串行數據時鐘信號BCLKX

它主要為DSP向外輸出串行數據提供數據轉移時鐘。

5.輸出串行數據線BDX

它是串行數據輸出端。

6.輸出串行數據幀同步信號BFSX

它主要保證輸出串行數據的同步。

(有關串行通信的內容我們將在第六章《串行接口通信》做詳細的介紹。)

除了上述的引腳外,DSP還有測試引腳、主機接口引腳等。測試引腳是符合IEEE1149.1標準的在片仿真接口,主要是完成DSP的試驗仿真。主機接口引腳主要是完成DSP與PC或其他主CPU間的通信。項目中,我們沒有用到主機接口引腳。

評論