100MHz 數字存儲示波表樣機的研究與試制----顯示數據傳輸電路

5.2顯示數據傳輸電路

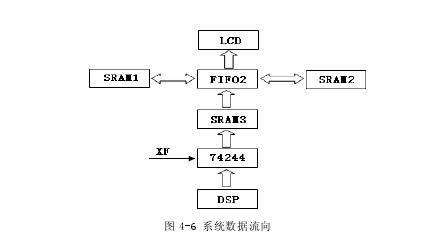

本文引用地址:http://www.j9360.com/article/201706/348239.htm顯示數據在整個系統的流向如圖4-6.模擬信號經AD采樣進來后通過FIFO進入DSP處理,處理完的數據隨后存入SRAM3.SRAM3中的數據經FIFO2送入SRAM1和SRAM2.當要顯示波形時,SRAM1、SRAM2分時復用,將顯示數據再經過FIFO2送至液晶顯示。系統中,SRAM1、SRAM2、SRAM3都為單口RAM,所以主要存在以下兩個問題:1.合理分配SRAM3的地址總線、數據總線分時被DSP和FPGA2占用的問題;2.正確協調SRAM1和SRAM2分時復用送顯示數據的問題。

5.2.1 SRAM3的總線占用

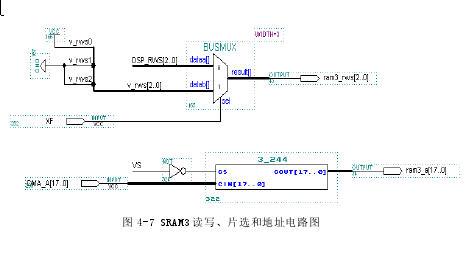

解決SRAM3總線占用問題的關鍵是由DSP發出的XF信號(如圖4-7)。當XF為低電平時,SRAM3的讀寫、片選信號ram3_rws[2..0]由DSP發出的讀寫和片選信號DSP_RWS[2..0]控制,同時DSP的數據、地址線通過74244和SRAM3的數據、地址線連接起來,并利用XF作為選通信號。當XF為高電平時,SRAM3固定為讀信號和片選信號有效,此時SRAM3中的數據通過FIFO2進入SRAM1和SRAM2.DMA_A[17..0]是FPGA里地址計數器產生的往SRAM1和SRAM2中寫數據時的地址。這樣,我們就可以通過控制XF的高低來選擇是誰占用SRAM3的總線。

5.2.2 SRAM1和SRAM2的分時復用

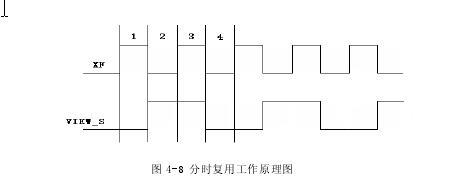

所謂分時復用就是指兩片顯示存儲器SRAM1和SRAM2依次向液晶提供顯示數據。它的工作原理如圖4-8所示。其中,View_S由XF反相后二分頻得到。

圖中各部分的工作狀態如下:

1. RAM3經FPGA2向RAM2里寫數據。同時,RAM1的數據送LCD顯示。

2. DSP向RAM3里寫數據。同時,RAM2的數據送LCD顯示。

3. RAM3經FPGA2向RAM1里寫數據。同時,RAM2的數據送LCD顯示。

4. DSP向RAM3里寫數據。同時,RAM1的數據送LCD顯示。

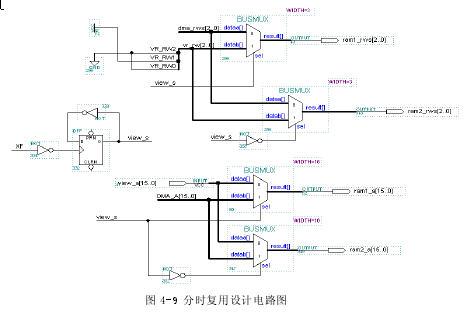

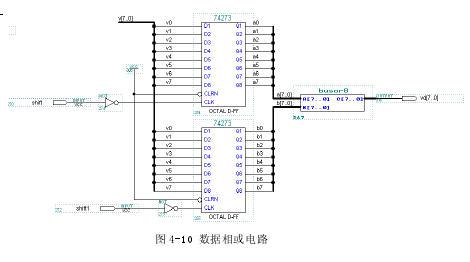

它的具體工作電路如圖4-9.

圖中,DMA_RWS[2..0]為固定的讀信號和片選信號有效。VIEW_A[15..0]為顯示時讀顯示RAM的地址。DMA_A[15..0]為寫顯示RAM時的地址。這兩個地址都由FPGA中的地址計數器產生。

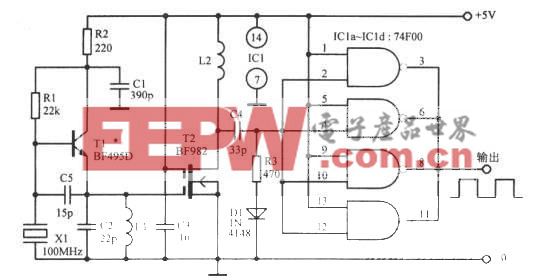

數字存儲示波器的顯示基本包括兩部分,一部分是界面顯示部分,包括菜單的顯示,光標的顯示等,另一部分是波形顯示部分,波形顯示部分是隨時在更新的,而菜單顯示部分更新的次數是很少,一般在不按鍵操作的情況下是很少改變的。所以我們采用分頁顯示,即將顯示存儲空間分成兩個區間,每個區間都是一屏顯示所需的空間即為240×320×2÷8=19200Bytes.一個區間用來顯示菜單,光標等不常刷新的界面,一個區間用來顯示波形,LCD顯示時將兩個存儲區間里的對應地址的數據通過硬件電路相或以后再送LCD顯示。這樣在軟件處理是節省了重復刷屏的時間,也簡化了軟件的編寫。圖4-10為由顯示RAM中兩個的數據區間相或后送到LCD顯示的電路。其中SHIFT和SHIT1分別兩個區間的地址計數器的計數時鐘,它們的時鐘脈沖要求在一個CP周期內完成,即兩個區間的數據讀取必須在一個CP時鐘周期內才能保證正確的數據顯示。

第六章串行接口通訊

在很多現場測試場合,工程技術人員都需要獲得某種形式的測量結果的硬拷貝,以便以后作為參考資料使用,或者設備報告發生錯誤動作時需要查看以往的資料。另外,在很多情況下我們需要把示波表中的信號傳往PC機,同時在某些情況下,我們也可能希望用PC機來對示波表進行控制,以上這些情況都要求示波表具有通訊能力。也就是說,示波表必須裝有通訊硬件以及其支持的軟件。我們稱此通訊用軟硬件為“接口”。常用的接口有兩種,RS-232接口和通用接口總線(GPIB),后者又稱為IEEE-488總線。與并行接口相比,串行接口的最大特點是減少了器件引腳數目,降低了接口設計復雜性。

串行通信是指數據按位依次傳輸,串行通信中要求發送和接受雙方必須遵守統一的規定,這樣才能保證正常進行,這些對數據傳送方式的規定就是通信協議,通信協議包括數據格式和時間限制等方面的定義和要求等,通信協議可由用戶自己制定,也可采用標準通信協議。

串行數據傳輸可分為同步和異步兩種模式。通用PC機的RS-232接口為通用異步接口UART(Universal Asynchronous Receiver and Transmitter),而MOTOROLA公司的串行外圍設備接口SPI、隊列SPI(QSPI)、PHILIPS公司的內部IC總線(I2C),National公司的微總線(MICROWIRE)均為同步串行協議。目前幾乎所有的數字信號處理器都提供了一個或多個串行接口,然而,多數DSP芯片提供的是同步串口。在實際的應用中,也需要DSP能夠與外設進行異步串行通信,如與PC機進行串行數據傳輸就要求DSP系統具UART串行接口。針對這種情況,本文研究并實現了一種簡單、可靠的異步串口擴展方法。

實際設計中,我們采用美國MAXIM公司的MAX3111串行異步收發器,與DSP的McBSP口直接連接,將同步數據變換為UART異步數據格式進行傳輸。硬件上無需任何其它外圍器件,同時由于異步數據的發送和接收由MAX3111以硬件方案實現,所以軟件編程需要考慮的也只是DSP與MAX3111之間的同步數據通信。這樣,用最簡單的硬件連接和軟件編程就能實現同步到異步的串行數據格式轉換。

6.1 McBSP的功能與特點

TMS320VC5416具有3個高速、全雙工、多通道緩沖串行接口(McBSP),其方便的數據流控制可使其與大多數同步串行外圍設備接口。McBSP是在標準串行接口的基礎上對功能進行擴展的,除具有標準串口的功能特點外,其靈活性體現在如下幾個方面:

◆雙緩沖區發送,三緩沖區接收,允許連續數據流傳輸;

◆可與SPI、IOM-2、AC97等兼容設備直接接口;

◆可編程幀同步、數據時鐘極性,支持外部移位時鐘或內部頻率可編程移位時鐘;

◆擁有相互獨立的數據發送和接收幀同步脈沖和時鐘信號;

◆多通道發送和接收,最多可達128個通道,速度可為100Mbit/s.

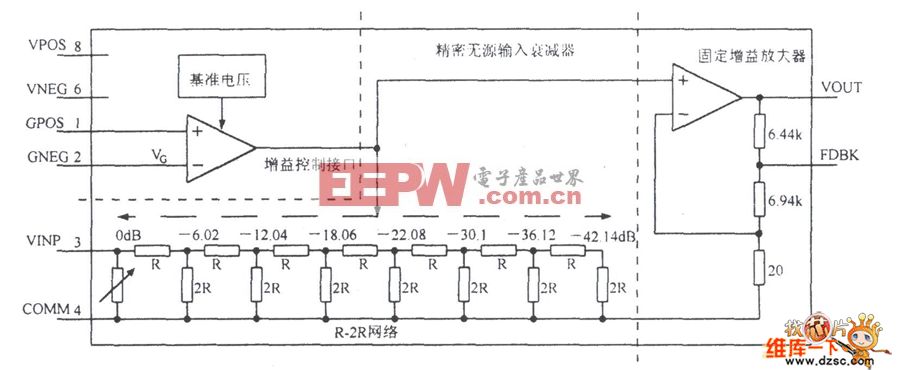

6.2 MAX3111通用異步收發器

MAX3111通用異步收發器是MAXIM公司專門為小型微處理系統進行最優化設計的UART,它包括一個振蕩器和一個可編程波特率發生器;具有一個可屏蔽的中斷源;另具有一個8字節的接收FIFO(先入先出)緩沖器。它應用SPI/MICROWIRE接口技術直接與主控制器進行通信,線路簡單、體積小,通信速率可達30kbit/s.另外其內部除具有UART之外,還包括兩個RS-232電平轉換器,這樣無需再接入普通的MAX232進行電平轉換,即可應用一個芯片實現微控器(具有PI/MICROWIRE接口)與PC機或其它設備之間的異步數據傳輸。

MAX3111通過SPI接口與主設備進行16位數據的全雙工同步通信,即主設備傳送16位數據給MAX3111的同時,也可接收到MAX3111發送的16位數據。主設備在MOSI線上向MAX3111發送的16位串行數據序列中包括傳輸格式控制字,如波特率設備、中斷屏蔽、奇偶校驗位等,同時還有發送的數據字。MAX3111在MISO線上向主設備發送的16位數據序列中除了接收到的數據外,還包括中斷標志等狀態位。所以通過16位的實時數據傳輸,主設備可獲得MAX3111工作狀態信息,同時對其具有完全控制權利。這樣,兩個設備的控制、狀態、數據信息的實時通信就保證了數據傳輸的可靠性和穩定性。

6.3 TMS320VC5416與MAX3111的接口設計

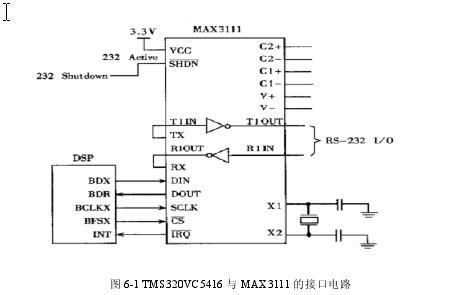

TMS320VC5416的McBSP串行接口工作于時鐘停止模式時與SPI協議兼容,可直接與MAX3111進行連接,從而實現與RS-232設備進行異步數據傳輸。此時DSP作為SPI協議中的主設備,其接口電路如圖6-1所示。

TMS320VC5416發送時鐘信號(BCLKX)作為MAX3111的串行輸入時鐘,發送幀同步脈沖信號(BFSX)作為MAX3111的片選信號(CS)。在這種方式下對接收時鐘信號(BCLKR)和接收幀同步信號(BFSR)將不進行連接,因為它們在內部與BCLKX和BFSX相連接。BDX與DIN連接作為發送數據線,BDR與DOUT連接作為接收數據線。MAX3111的TX與T1IN連接,RX與R1OUT連接,以便利用其片內的轉換器實現UART到RS-232電平的轉換。MAX3111的中斷信號(IRQ)與DSP的外部中斷相連。

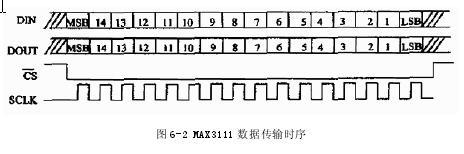

在SPI串行協議中,主設備提供時鐘信號并控制數據傳輸過程。由MAX3111接口電路時序圖6-2可知,必須設置DSP的McBSP于適當的方式才能保證與MAX3111的時序相配合。

MAX3111要求在數據傳輸過程中CS信號必須為低電平,在傳輸完畢后必須為高電平。此信號由McBSP的BFSX引腳提供,因此必須正確設置DSP的幀脈沖發生器,使之在每個數據包傳輸期間產生幀同步脈沖,即在數據包傳輸的第一位變為有效狀態,然后保持此狀態直到數據包傳輸結束。

McBSP的采樣率發生器產生適當頻率的時鐘信號,由BCLKX引腳輸出,保證主從設備間的同步數據傳輸。因此必須正確設置DSP的采樣率發生器時鐘源(CLKSM)和時鐘降頻因子(CLKGDV)。根據SPI傳輸協議,必須正確設置數據發送延遲時間(XDATDLY)。由圖6-2可知MAX3111要求在SCLK變高之間的半個周期開始傳輸數據。

所以必須為McBSP選擇合適的時鐘方案,即設置McBSP的時鐘停止模式。在本應用中采用McBSP的時鐘停止模式2(CLKSTP=11b,CLKXP=0),這樣即可保證與MAX3111的時序相配合。

結論

經過一年多的項目分析、論證、設計、制作及調試,現已完成本課題的設計任務,完成了樣機的制作。本課題是“100MHz數字存儲示波表”項目中數字系統部分。它是該項目的重要設計部分,通過本課題的研究,本文主要完成了以下幾點:

1.數據采集系統的研究與設計。數據采集系統是數字存儲示波器與模擬示波器的主要不同之處,它完成模擬信號數字化,通過實時取樣和隨機取樣兩種取樣技術將模擬信號數字化。這里主要難點在于AD在高速采樣率下怎樣避免采樣時鐘的干擾和AD數據與FIFO的時序配合問題。

2.顯示控制電路實現。主要設計精髓在于在沒有專用控制芯片下,采用FPGA設計LCD顯示時序電路,完全由硬件電路實現LCD數據顯示流程以及多頁面數據顯示控制技術。

3.DSP與外部接口電路的設計。主要是通過MAX3111完成同步到異步的串行數據格式的轉換。

同時在設計和調試過程中遇到了以下幾點問題:

1.在調試LCD顯示時,顯示屏上某些點出現閃爍現象。經研究發現是LCD的顯示控制時序配合不好的緣故。重新調整時序后,閃爍現象消失。

2.在隨機取樣時,設計的展寬脈沖電路時,發現隨著MAXPLUSⅡ每次編譯的不同,波形恢復出現效果不一樣,有時能正常恢復,有時出現飛點,后來在選用FPGA時采用了工業級,效果非常好。

通過以上工作,示波表的硬件軟件調試工作已初步完成,考慮到項目設計和調試過程中碰到的問題以及與國外同類產品的比較,特提出了以下優化建議:由于本課題采用了隨機取樣技術,它只能測出單一頻率的周期信號。對于非周期信號不能再現完整波形。故建議在經后工作中提高實時取樣時鐘。全部采用實時取樣技術。這樣也簡化了軟件的設計。

評論