基于DSP的諧波測量系統

0 引言

本文引用地址:http://www.j9360.com/article/201706/347792.htm隨著電力電子技術的發展,越來越多的非線性器件應用到電網中,給電網帶來了嚴重的諧波污染,致使供電電壓波形畸變。目前,電力系統諧波污染與功率因數降低、電磁干擾已并列為電力系統的三大公害。諧波的危害不僅影響供電質量,而且對用電設備也會造成嚴重的損耗,如增加設備的溫升,使絕緣部分老化,影響設備的工作質量,縮短設備壽命,并且會影響電能計量裝置的準確性。諧波污染使線性用戶產生不必要的費用,而非線性用戶作為諧波污染源,反而會少計量電能,這是極其不公平的[1]。因此,對電網中的諧波進行準確的測量,以此來對諧波源進行治理,是提高當今供電質量的重要措施。為此,本文以高精度的數字信號處理芯片TMS320VC5409[2]為系統核心,設計了關于諧波的實時測量與計算裝置,用來對電網信號進行實時采樣、諧波分析和計算結果顯示。

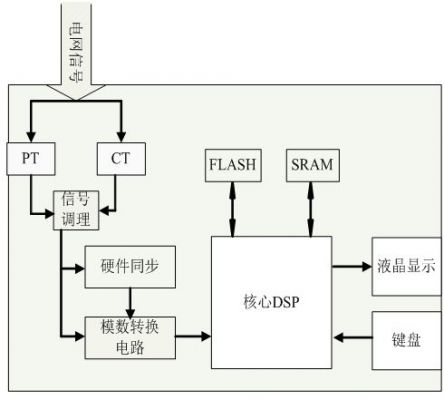

1 硬件結構和功能

本系統主要是由核心DSP、模數轉換電路、液晶顯示電路以及鍵盤電路組成。電網信號經過電壓互感器和電流互感器后,由信號調理電路變為模數轉換電路能夠處理的信號,然后送入模數轉換電路,將模擬信號變為離散的數字信號,采樣到的數據經過DSP芯片的分析計算后送入到液晶電路,對計算后的數據進行顯示,以供查看。鍵盤主要用來控制液晶對數據的顯示,控制液晶進行翻頁等功能,系統框圖如下:

圖1 系統的總體框圖

1.1 采樣同步及A/D轉換

電網系統中的電流和電壓是含有多次諧波且基頻不穩定的信號,當采樣信號的頻率和被采樣信號的頻率不同步時就會產生頻譜泄露,影響諧波測量的準確性。在諧波測量的測量過程中,采用何種方法對信號進行準確的采樣是關鍵的一步,交流信號的采樣方法包括:同步采樣法、準同步采樣法和非整周期采樣法。本文采用同步采樣法,為了達到同步采樣的目的,對每周期的信號采樣同樣的點數,本文利用鎖相倍頻電路來產生同步采樣脈沖信號,電路是由鎖相環芯片74VCH4046和CPLD構成的,被測信號經過一個方波電路,變成所需要的方波信號,然后由鎖相環芯片和CPLD對信號進行同步和512倍頻,從而在被采樣的信號的一個周期內產生512個采樣脈沖信號,控制模數轉換電路對信號進行采樣和A/D轉換。74VHC4046能使輸出信號的相位隨著輸入信號的相位做出改變,最終達到信號的同步。所以這個鎖相倍頻電路不需要軟件的干預,節省了軟件資源;又因為此電路所有功能均由硬件完成,還提升了檢測的速度。

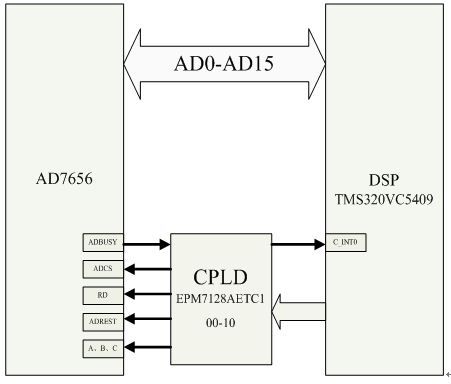

本設計采用 ADI 公司的高速高精度模數轉換芯片 AD7656,其內部擁有6個單獨的16位ADC,可以實現6路同步采樣。最高采樣速率可達250kS/S,雙極性模擬輸入,片上具有電壓參考源和參考緩沖,也可以由外部引入參考源,轉換后數據有串行和并行傳輸方式。AD7656和DSP的連接方如下:

圖2 AD7656和DSP的連接圖

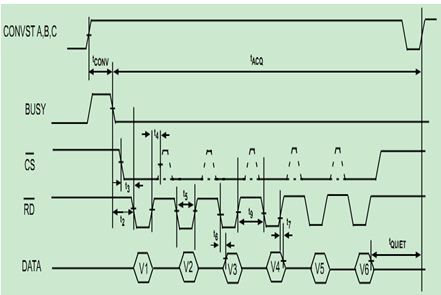

在本系統中AD7656與DSP采用并行數據傳輸方式,將CONVSTA、CONVSTB、CONVSTC并在一起,以啟動6路AD同時采樣,啟動信號由采樣信號控制,不需要DSP的干預。AD7656的片選信號ADCS、讀信號RD、復位信號ADRST由DSP通過CPLD來產生控制邏輯,下圖為AD7656的并行讀時序圖:

圖3 AD7656并行讀時序圖

在并行模式下,當ADBUSY信號變低時說明轉換結束,ADBUSY信號連接到DSP的外部中斷0,以中斷的方式通知DSP對轉換后的數據進行讀取。此時將/CS和/RD都置低使能輸出總線,轉換后的數據被輸出到并行數據總線上,DSP就可以依次進行6路輸出信號的讀操作。

1.2 DSP核心電路

本系統的處理核心采用TI公司的TMS320VC5409,它是16位的定點DSP,除了DSP通用的結構特點以外,它還具有:16K×16的片上ROM,32K×16位的片上雙尋址RAM,擁有豐富的片上外設:軟件可編程等待周期發生器(SWWSR)和可編程分區轉換邏輯電路(BSCR),片上鎖相環時鐘發生器,3個多通道緩沖串行口(McBSP),增強的8位并行主機接口(HPI),6通道的DMA控制器,本芯片也可在低功耗情況下工作。

此DSP的核心電壓是1.8V,I/O電壓是3.3V,而其他的器件大多是5V的驅動電壓,所以本系統選用ALTERA公司的CPLD——EPM7128AETC100-10進行電平轉換和邏輯控制,主要用來DSP與其他芯片之間的通信與地址譯碼。因為在本系統中需要對采樣的數據進行大量的運算,產生的數據再加上運行的程序使DSP的片上存儲資源捉襟見肘,所以為DSP外擴了FLASH和RAM存儲器[3]。

1.3 液晶顯示電路

本設計采用的是LCM128645ZK液晶進行顯示,本液晶模塊的液晶屏幕為128*64,可顯示4行,每行可顯示8個漢字。與DSP可以進行并行8位/4位和串行3線/2線的連接方式。中文液晶顯示模塊可實現漢字、ASCII碼、點陣圖形的同屏顯示,廣泛的應用于各種儀器儀表、家用電器和信心產品上作為顯示器件。本系統中液晶與DSP之間采用串行數據傳輸方式,液晶的第15引腳(并行/串行傳輸方式選擇引腳)接地時,液晶為串行工作模式。此時液晶的第5引腳為串行數據線,第6引腳為串行輸入脈沖。DSP通過這2 個引腳即可在液晶上顯示出數據或波形。液晶的6腳與DSP串口2的緩沖串行口數據發送端BDX2引腳相連,作為時鐘信號,5腳與串口2的幀同步脈沖輸出端BFSX 2引腳相連,DSP串口的這倆根引腳被設置為通用輸入輸出引腳GPIO。當DSP將數據處理完后通過這倆根引腳將計算后的數據送到液晶進行顯示。下圖是本液晶的串行傳輸時序圖:

圖4 液晶串行傳輸時序圖

當片選信號CS為高電平時,同步時鐘線(SCLK)上輸入的信號才會被接收,另一方面,當片選信號(CS)為低電平時,模塊內部的串行傳輸計數與串行資料將會被重置,也就是說在此狀態下,傳輸中的資料將被終止清除,并且將待傳輸的串行資料計數重設回第一位,因此,模塊選擇引腳(CS)可被固定接到高電平。

模塊的同步時鐘線(SCLK)具有獨立的操作,但是當有連續多個指令需要被傳輸時,必須確實等到一個指令完全執行完成后才能傳送下一筆資料,因為模塊內部沒有傳送/接收緩沖區。

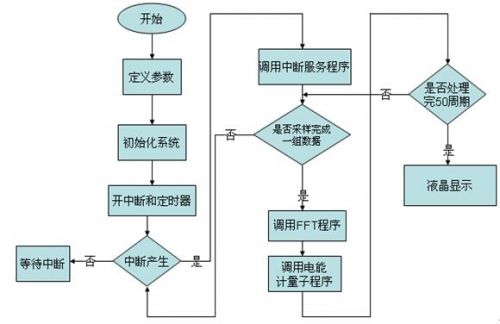

2. 系統的軟件設計

本系統的軟件主要是完成對信號的采樣、對采樣數據的FFT變換[4]、對變換后的數據進行諧波的各項參數(諧波的幅值、有功功率、視在功率、功率因數、諧波含量)等的計算以及對計算后的數據進行顯示等。軟件流程圖如下:

圖5 軟件流程圖

因為本系統使用的是定點DSP,而采樣數據經過FFT運算以后產生的數據為浮點數,直接進行浮點數運算不能滿足系統的實時性要求,通過TI自帶函數庫中關于FFT函數的調用,可以達到系統對實時性的要求。

3、設計結果測試與分析

最后利用達盛科技的NC-2100綜合設計試驗臺對本系統進行了測試,該實驗臺可以輸出倆路信號并進行混頻,一路輸出50HZ的基波信號,另一路依次輸出150、250、350、450、550HZ的信號,既3、5、7、9、11次諧波,兩路信號進行混頻后輸入到系統,分別進行1%和10%諧波含量的測試,測試結果如下:

表1 各相依次加1%的各次諧波的測試結果

表2 各相依次加10%的各次諧波的測試結果

4、結束語

本系統以數據處理能力強大的16位定點DSP芯片TMS320VC5409為數據的處理核心,充分的利用了DSP強大的數據處理能力,對采樣到的數據進行了FFT變換和諧波分析,且改系統的精度較高。

評論