基于國產龍芯GS32I的小系統的硬件設計

一. 引言

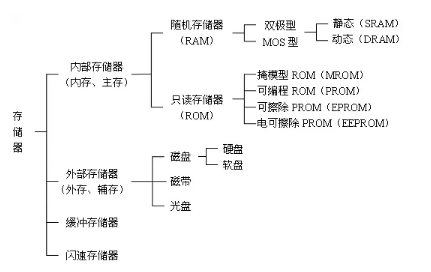

本文引用地址:http://www.j9360.com/article/201705/359677.htm目前,嵌入式系統已經滲透到各個領域:工業控制,軍事國防,消費類電子產品,網絡通信等,但大部分領域的應用都是基于國外各大廠商的嵌入式處理器。在嵌入式領域使用國產芯片,走國產化道路已經成為一個迫切需要解決的問題。目前國內的芯片主要有星光系列、漢芯系列、神威系列、青鳥嵌入式芯片、方舟系列、龍芯系列等,這些芯片各有自己的特點。

本設計采用了龍芯系列的GS32I SoC處理器,探討并設計如何構造一個小型嵌入式硬件系統,同時兼顧科研與應用兩方面的要求,在該平臺的基礎上可以連接各種外設進行嵌入式算法的實驗。該系統經簡單修改能方便地應用在軍事、工業控制、數據采集等領域。

二. 芯片簡介

目前龍芯系列微處理器有龍芯1號,龍芯2號微處理器。龍芯2號集成了橋芯片,采用分離的32位地址/數據總線,因此本設計采用基于龍芯2號的GS32I SoC處理器。

GS32I高集成系統設備,提供了高帶寬的存儲總線,一個100/125MHz SDRAM控制器和一個SRAM/Flash EPROM控制器;48個GPIO口,其中22個專用,可以多路復用,以便在需要的時候能提供額外的功能;33/66MHz、32位PCI控制器(兼容 PCI2.2);兩個10/100M以太網控制器;通用串行總線(USB)主機及裝置控制器,兩個通用異步收發器,一個AC97控制器,一個PCMCIA 控制器。GS32I處理器內部還實現了與MIPS32兼容的基于TLB的虛擬地址轉換單元、例外機制、中斷機制、指令控制、時鐘產生等功能。GS32I提供了強健的電源管理,有空閑和睡眠兩種省電模式,還提供有EJTAG接口,用于系統連續檢查。

三. 小系統的設計

GS32I總線采用系統總線(SBUS)與存儲器和外部設備通信。SBUS是GS32I處理器內部的36位物理地址和32位數據地址總線。需要高帶寬或者需要離CPU近的設備連到SBUS總線,包括存儲器控制器(SDRAM, FLASH/SRAM)、32位PCI總線接口控制器、DMA 控制器、USB1.1控制器和以太網控制器。不需要高帶寬連接的設備均連至片上外部總線PBUS,外部總線的頻率始終是系統總線(SBUS)頻率的一半。 PBUS設備包括電源控制單元、中斷控制器、時鐘定時器、通用I/O、UART、AC97控制器。

1. 系統總體設計

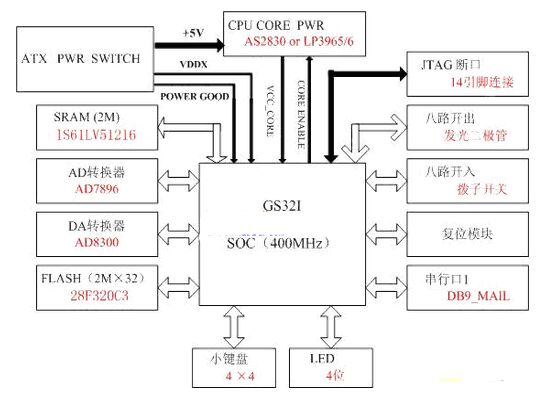

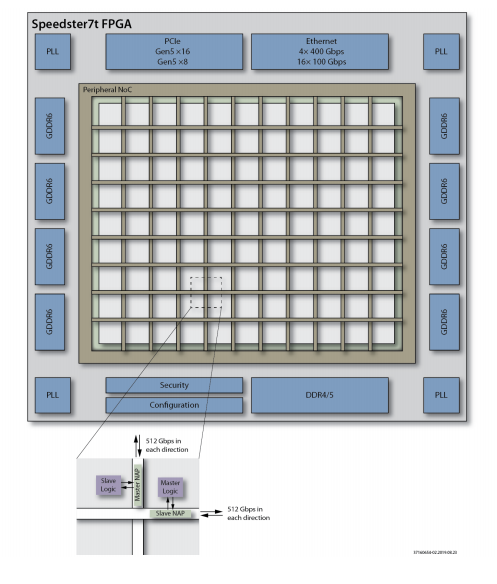

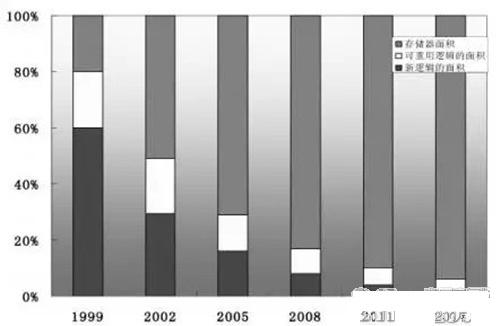

小系統硬件功能框圖如圖1所示:

圖1 總體框圖

系統設計包括CPU啟動和復位電路以及外部I/O設備的地址擴展;包括FLASH和SRAM在內的存儲系統的設計;RS232串口;用于人機交互的4×4小鍵盤和4位LED數碼管,另外還提供了八路開關量的輸入/輸出、 A/D和D/A轉換器以及用來實驗和測試的EJTAG接口等。

2. 系統的啟動與復位

龍芯GS32I支持16位和32位啟動。管腳 ROMSEL和ROMSIZE的狀態決定了CPU啟動ROM的寬度和類型,此表如下所示:

基于系統國產化的需求,使用免費開放源代碼的Linux操作系統便于實現國產化。為了方便其嵌入,本系統設置為32位FLASH啟動,即把ROMSEL和 ROMSIZE都置為低電平。啟動時,若ROMSEL為低電平,則RCSO#缺省設置為有效,并且對Ox0 1FCO 0000使能,CPU從物理地址Ox0 1FCO 0000地址開始執行程序。因此,FLASH或ROM的起始地址應該通過RCS0#映射到此處。系統復位模塊提供GS32I處理器的硬件復位和軟復位。當管腳VDDXOK和RESETP#都有正電平跳變時,硬件復位有效,這一般在系統加電時產生。

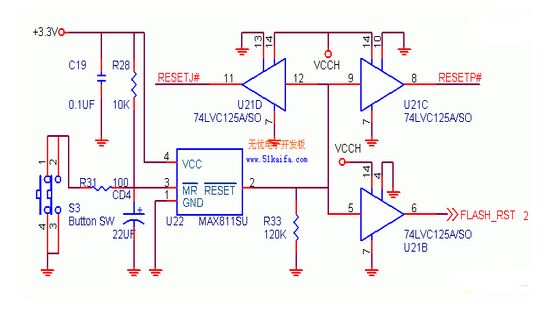

若電源供電正常,且VDDXOK保持,當RESETP#發生正電平跳變時,軟件復位有效。這種復位對一些寄存器,特別是系統控制塊寄存器沒有影響。復位芯片采用可監視供電電源的低功耗芯片MAX811SU,電路原理如下圖所示:

圖2 RESET電路

3. 存儲系統的設計

GS32I提供了高帶寬的存儲總線,一個100/125MHz SDRAM控制器和一個SRAM/Flash EPROM控制器。SRAM/Flash EPROM控制器可以支持FLASH 、SRAM、LCD 、PCMCIA和外部I/O設備等。

針對存儲容量要求比較低的小型嵌入式系統,SRAM設計為16M bit,FLASH設計為64M bit,已能夠滿足應用需求。SRAM/Flash EPROM控制器有四個可編程的片選信號RCS0#~RCS3#,本文將RCSO#,RCS1#用于FLASH和SRAM,RCS2#用做對外部I/O設備的地址擴展。

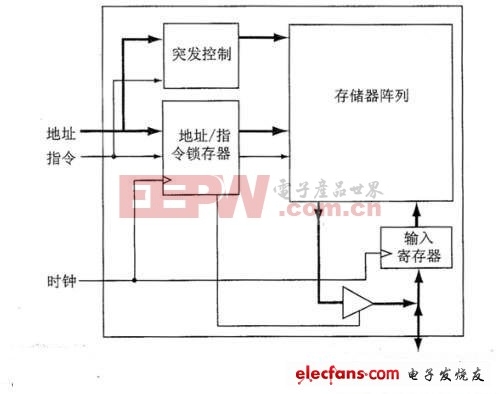

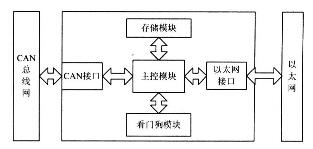

本設計采用了2片Intel公司的28F320C3 FLASH,作為系統ROM區,存放操作系統和用戶應用程序;兩片ISSI公司的IS61LV51216 SRAM,作為系統RAM區,存放系統數據和用戶數據。其中RCS0#用于FLASH的片選信號,與FLASH的CS#連接,RCS1#用于SRAM的片選信號。關于存儲器的硬件設計示意圖如圖所示:

圖3 存儲系統的硬件設計示意圖

⑴ FLASH接口設計及相關寄存器的設計

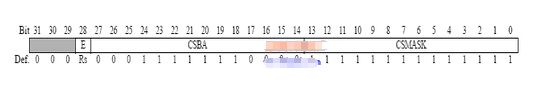

28F320C3 FLASH的存儲容量為2M×16 bit。由于SRAM/Flash EPROM控制器設置為32位總線寬度,使用兩片28F320C3 FLASH擴展為32位總線寬度,地址線連接至GS32I地址總線的RAD2~RAD22,每次讀取四個字節; GS32I復位后起始地址是 0x0 1FC0 0000,FLASH的地址被裝載到此處,每個片選信號的地址映射范圍是通過設置片選地址寄存器mem_staddr0來實現的,片選地址寄存器 mem_staddr0的格式如下所示:

當E位置為1并且滿足條件“(physical_addr&CSMASK)==CSBA”時,片選信號將變為有效。 physical_addr是內部系統總線作為輸出的實際的36位物理地址,CSBA用來指定這個片選信號的物理基地址的31:18位,CMASK用來指定CSBA的哪些位被用來譯碼片選信號。CSBA的高四位,也就是35:32位由mem_stcfg0寄存器的DTY域來決定。本系統中,mem_stcfg0寄存器的DTY域設置為3,則對應的高四位35:32位的值為0000B,CSBA設置為0x07F0,CMASK設置為 0x3FF0這樣FLASH的地址就被映射到0x0 1FC0 0000—0x0 1FFF FFFF。

FLASH最快讀取速度為70ns, CPU系統總線周期為10ns(100MHz),因此在讀取FLASH時需要插入等待狀態,通過設置靜態時序寄存器mem_sttime0來插入等待周期。靜態時序寄存器mem_sttime0的格式為:

Ta域為數據有效時片選信號要求插入的周期數,考慮到系統的穩定性,根據FLASH的讀取參數,插入7個等待周期,因此Ta域設置為7。Ta域默認值為29,在選取啟動ROM芯片時,若芯片讀取參數需要插入的等待周期超過29,則這種芯片不可用。Tcsh域用來指定在兩次訪問期間片選信號保持的時鐘周期數,這里設置為0。

⑵ SRAM接口設計及相關寄存器的設計

SRAM的存儲容量設計為512K×32位,可使用兩片IS61LV51216 SRAM(512K×16)通過位擴展實現。將RCS1#連接到SRAM的片選信號CS#上,地址線連接至GS32I地址總線的RAD2~RAD20,地址范圍是通過設置片選地址寄存器mem_staddr1來映射的,設置方法與mem_staddr0的實現相同。

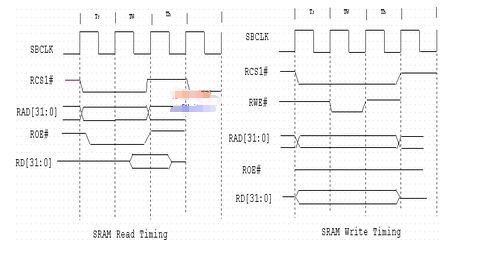

SRAM時序與CPU的配合是通過設置靜態時序寄存器mem_sttime1來完成的,mem_sttime1的格式與的mem_sttime0相同。IS61LV51216 SRAM的讀寫速度最快為10ns, 片選信號RCS1#插入一個等待周期,Ta域設置為1,Tcsh域設置為0。對于SRAM的寫入,與其相關的域有Twcs,用來指定寫脈沖RWE#后片選信號RCS1#保持的時鐘周期數, Tcsw用來指定片選信號RCS1#有效后的幾個時鐘周期插入RWE#,Twp用來指定RWE#持續的時鐘周期數。根據SRAM的參數和SRAM的讀寫時序,本設計中,Twcs,Twp都設置為0,Tcsw設置為0000b,這樣使SRAM與CPU的時序能夠配合且保證系統的穩定性。設置完成后,SRAM 的讀寫時序如下圖所示:

圖4 SRAM讀寫時序圖

4.其他外部設備的設計

GS32I處理器提供48個GPIO口,其中22個專用,48個GPIO中的32個由主GPIO塊控制,另外16個是次級GPIO口。每個GPIO 口可以被配置作為輸入或輸出,并且能夠連接到內部中斷控制器對輸入的信號產生一個中斷。本設計中采用GPIO管腳作為外設的數據信號和控制信號。

評論