專用DSP核心助陣 SoC支持AI算法非難事

雖然英特爾(Intel)、NVIDIA等芯片大廠近期在人工智能(AI)、神經網絡(NN)、深度學習(Deep Learning)等領域動作頻頻,但半導體領域的其他業者也沒閑著,而且其產品發展策略頗有以鄉村包圍城市的味道。 益華計算機(Cadence)旗下的CPU/DSP處理器核心授權公司Tensilica,近期便發表針對神經網絡算法設計的C5 DSP核心授權方案。 在16奈米制程條件下,該核心所占用的芯片面積約僅1平方公厘,卻可提供達到1TMAC的運算效能,而且功耗遠比CPU、GPU等處理器更低,適合各種嵌入式運算裝置使用。

本文引用地址:http://www.j9360.com/article/201705/359167.htmCadence Tensilica營銷資深事業群總監Steve Roddy表示,神經網絡技術正以飛快的速度演進。 根據該公司所收集的數據顯示,在2012~2015年間,每幾個月就有新的神經網絡算法問世,且復雜度均比先前的算法明顯增加。 在短短3年內,神經網絡算法的復雜度已增加16倍,遠超過摩爾定律的發展速度。

也由于神經網絡算法演進的速度比半導體技術進步的速度還快,因此神經網絡算法的開發者只能用內建更多處理器核心的硬件來執行新的算法。 但這種作法只能在云端數據中心行得通,無法適用于功耗、體積與成本均受到嚴格限制的嵌入式裝置。

另一方面,目前神經網絡算法大多在通用型CPU、GPU芯片上執行,也是一種遷就于現實的結果。 CPU、GPU是已經大量生產的芯片,取得容易且成本遠比自己打造ASIC來得低,而且對算法開發者來說,CPU跟GPU提供很好的編程環境與應用設計靈活性,這也是ASIC所比不上的。

事實上,Tensilica也認為,利用硬件加速器這類ASIC來執行神經網絡算法,絕對是一條行不通的路。 因為ASIC設計通常需要數個月到1年時間,至于芯片要大量生產,應用在終端產品上,更常已是2~3年后的事。 在神經網絡發展日新月異的情況下,除非芯片設計者擁有未卜先知的能力,精準預測出3年后神經網絡算法會發展到何種地步,否則芯片開發者的產品可能還沒上市就已經過時了。

除了產品開發時程的問題,單純從技術層面來看,用硬件加速器與通用處理器共同執行神經網絡算法,也是問題重重。 由于神經網絡會牽涉到大量數據傳輸,若要將運算工作切割開來,用兩顆芯片共同執行,則兩顆芯片間光是數據傳輸,便很可能會占用掉一大半處理器資源,并帶來可觀的功耗量。

因此,如果有一種針對神經網絡算法優化的處理器核心,既能兼顧應用設計靈活性,又比通用型CPU、GPU有更高的算法執行效率,對于神經網絡的普及應用,將是一大加分。 這也是Tensilica決定推出專為神經網絡算法設計的C5數字信號處理器(DSP)核心的原因。

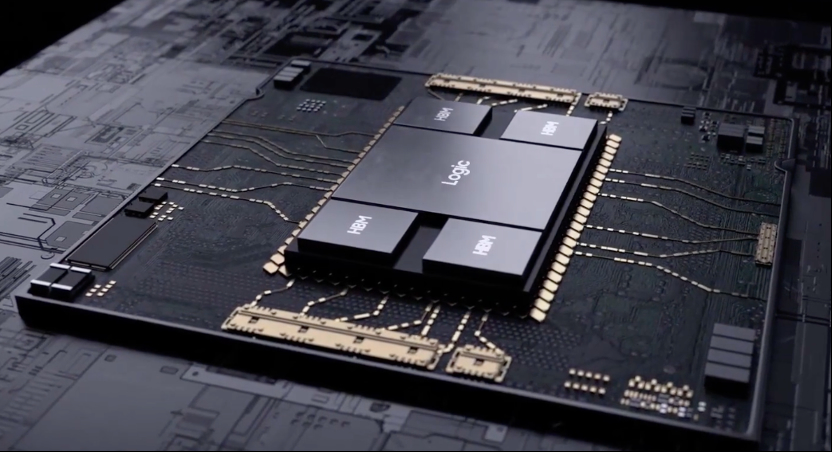

C5 DSP核心在16奈米制程條件下所占用的芯片面積為1平方公厘,能提供達1TMAC的乘法器效能給神經網絡算法使用。 若應用需要更高的乘法器效能,C5 DSP也允許SoC設計者采取多核心架構。 而且,因為C5 DSP是針對神經網絡運算優化的核心,因此功耗極低,不會像CPU或GPU,芯片功耗動輒數十瓦以上,甚至上百瓦,一般的嵌入式裝置也能輕松采用。

Roddy透露,雖然C5 DSP核心才剛正式發布不久,但早已有先導客戶正在利用C5 DSP核心開發下一代支持神經網絡算法的SoC。 據其預估,最早在2017年第3季,第一顆內建C5 DSP核心的SoC產品就會Tape Out。

評論