基于ZYNQ嵌入式小型化繼電保護平臺設計實現

作者/ 任華鋒 王晉華 孫振華 許繼電氣股份有限公司(河南 許昌 461000)

本文引用地址:http://www.j9360.com/article/201611/340863.htm摘要:本文介紹了一種應用在智能變電站中全新的嵌入式小型化繼電保護平臺的設計,該設計選用片內集成雙ARM內核和FPGA的Xilinx Zynq系列芯片,在成本、數據處理速度、功耗及可擴展性方面能夠滿足就地化安裝繼電保護設備的需求。全文從軟件和硬件方面詳細闡述了嵌入式小型化繼電保護平臺的設計方法。

引言

隨著加強智能電網建設的深入推進,網絡信息技術、電子傳感技術、數字變電技術、廣域測量技術、自動化控制技術等多種先進技術在智能繼電保護裝置中的應用日趨成熟。在此背景下,智能電網建設對繼電保護裝置的軟硬件設計也提出了更高的要求。繼電保護裝置的小型化設計和就地化安裝就是其中的一種發展趨勢。針對這些要求,本文介紹了一種基于Xilinx Zynq 7000系列片上系統(SoC)的嵌入式小型化繼電保護平臺的設計方法,就該平臺的整體框架、硬件設計、平臺搭建等方面進行了詳細的闡述。

1 平臺整體框架

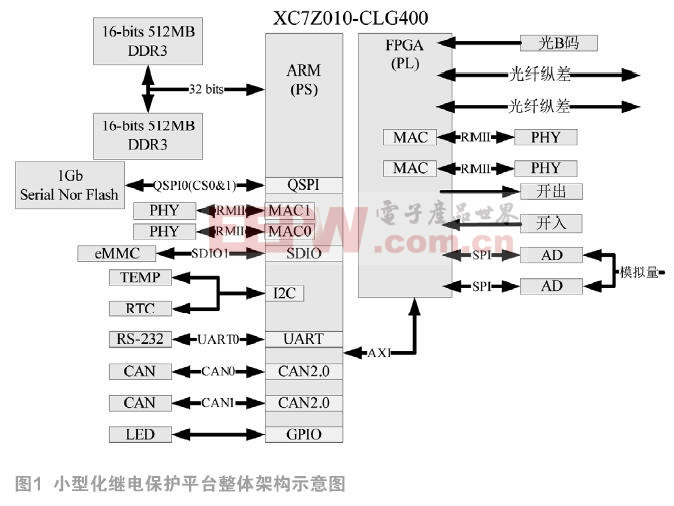

按照國家電網的規劃,小型化繼電保護裝置直接安裝在戶外一次設備旁,對裝置的電磁干擾、工作環境和結構強度等方面提出了更高的要求。本方案采用Xilinx的Zynq 7000系列芯片為主CPU,芯片片內集成了主頻800MHz的ARM雙核處理器、FPGA、PCIe、I2C、SD/MMC等常用通信接口,具有強大的數據處理和外設擴展能力,特別是功耗低,抗干擾能力強的特點,非常適合作為就地化安裝繼電保護裝置的硬件平臺。該平臺的整體框架如圖1所示。

2 平臺硬件實現

Xilinx Zynq 7000根據功能劃分為可處理系統(PS)ARM及其外設,可編程邏輯(PL)FPGA。硬件設計主要圍繞這兩部分展開。

2.1 PS側

PS側由ARM核管理、配置I/O外設、DDR控制等。ARM核的應用非常廣泛,可供參考的典型硬件設計資料非常多,限于篇幅,只對小型化繼電保護平臺應用到的部分進行介紹。

2.1.1 DDR內存控制器

大多數智能繼電保護設備運行嵌入式實時操作系統,由實時操作系統完成繼電保護算法、人機交互,以及基于IEC61850的網絡通信等功能。實時系統對DDR內存的容量和處理速度有很高的需求。在設計中使用了兩片Micron公司的DDR內存MT41K256M16HA-125-IT:E ,容量達到1G,與ARM核650MHz時鐘匹配工作在 525MHz時鐘速率。經過Nucleus實時操作系統的測試,系統運行正常。為保證繼電保護設備數據的可靠性,DDR內存控制器可增加ECC功能,位寬降為16bit,內存容量降為512M。

2.1.2 I/O外設配置

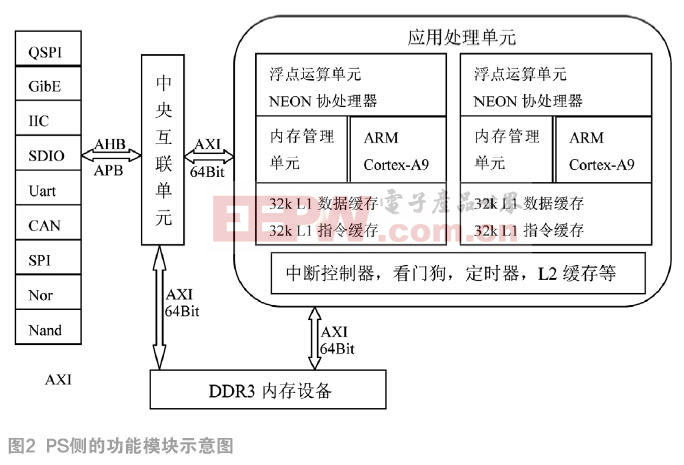

Zynq 的I/O引腳采用多路復用外設接口方式,PS側的MIO共有54路I/O,可用Xilinx 提供的硬件設計工具Vivado把I/O功能靈活定義成MAC、UART、I2C、CAN、SDIO等平臺中需要的外設接口,同時配置外設的工作時鐘。圖2為繼電保護平臺在Zynq SoC芯片PS側的功能模塊示意圖,其描述了外設和內核之間的數據通道和ARM內核的基本構成。

2.2 PL側FPGA設計

當前主流繼電保護設備廠家生產的智能保護設備硬件平臺基本采用“處理器+FPGA” 模式,由FPGA完成人機交互、網絡拓展、擴展開入開出、AD采樣等功能。這種模式下FPGA和處理器是兩個獨立運行的系統,實現數據同步和協同工作上處理復雜,在變電站電磁環境惡劣的工作地點容易出現問題。

Zynq將處理器和FPGA集成在芯片內部,ARM雙核和FPGA的數據交互通過高性能、高帶寬、低延時的AXI總線完成,消除了處理器和FPGA通過擴展總線數據傳輸速度低的瓶頸。特別是以ARM為主,FPGA為輔的片內協作工作模式,為平臺提供了豐富的外設擴展功能。

2.2.1 FPGA網絡功能設計

為了設計簡化和施工便捷,智能變電站過程層在IEC61850 標準下,SV和GOOSE網絡報文由點對點傳輸方式轉向共網方式傳輸。在Zynq平臺上由FPGA的MAC IP核通過以太網PHY擴展出的網口接收合并單元或智能終端發送的SV和GOOSE報文,通過MAC IP核實現報文類型甄別、單播、組播廣播報文的過濾,并對SV和GOOSE報文的屬性進行解析。為了抑制共網傳輸的網絡風暴,可加入風暴抑制判據,過濾掉異常報文,減輕ARM處理器的工作載荷,提高數據處理的實時性。

2.2.2 繼電保護功能模塊設計

Zynq充分考慮到在Xilinx FPGA產品上設計的移植性,可將原來“處理器+FPGA”模式下FPGA實現的功能模塊方便快捷地移植到Zynq平臺上,節省開發時間,保持產品穩定性。

2.2.2.1 人機接口功能實現

由于小型化保護裝置采用就地化安裝方式,直接暴露在風吹日曬、雨雪環境中,裝置密閉性要求達到IP67的防護等級,無法安裝液晶、鍵盤等人機交互器件。區別于通過FPGA擴展液晶和鍵盤外設的智能保護裝置,就地化保護裝置人機功能是通過安裝在主控室或保護小室的就地化保護智能管理單元來實現裝置的界面集中展示、配置管理、備份管理、在線監視和診斷功能,所有數據由就地化保護的網口通過光纖網絡上傳,抗干擾能力強。

2.2.2.2 常規互感器保護采樣功能實現

小型化保護的采樣方式有兩種:常規互感器采樣通過電纜直接連接到小型化保護裝置;電子式互感器SV和GOOSE共網通過光纖以太網接入小型化保護裝置。在常規互感器采樣方式中,小型化保護平臺使用兩片AD7606共16路采樣通道,采集電壓、電流等模擬量供保護或測控使用。

AD7606芯片通過串行SPI 和FPGA連接,由FPGA保持采樣時序和AD數據正確性,ARM核完成對FPGA采樣功能的參數,如每周波采樣點數、通道個數、預采樣時刻等進行設置,FPGA通過中斷方式通知ARM核收取采樣數據。這部分功能可由在“處理器+FPGA”模式下用Verilog HDL編寫的FPGA代碼稍作改動后移植到Vivado Zynq硬件設計工程中。

2.2.2.3 繼電保護開入開出回路實現

小型化保護裝置由于機箱尺寸受限,不能裝設太多的開入開出回路。考慮與非智能的一次開關設備接口,保留了8路遙信開入和8路出口回路來采集信息和控制一次開關設備。Zynq的PS側的復用MIO多用做外設接口,數量較少,無法實現16路I/O。開入開出設計由PL側的EMIO來實現,外部開入和PL側開出都經過總線收發器SN74LVC245,由FPGA編寫簡單的I/O硬件驅動,通過中斷或查詢方式通知ARM。

3 軟件框架和應用功能實現

嵌入式小型化繼電保護平臺的軟件框架主要包括平臺的底層硬件驅動、引導程序、嵌入式實時操作系統和應用功能模塊。

3.1 底層硬件驅動

Xilinx 的SDK開發工具提供了針對Zynq的BSP包,BSP包含ARM的外設接口驅動,并提供豐富的測試例程供開發者參考。BSP提供的ARM外設驅動代碼用C編寫,移植方便,改動量小。FPGA部分設計的網口和AD采集等模塊需要在PS側重新開發相應的驅動。

3.2 平臺引導

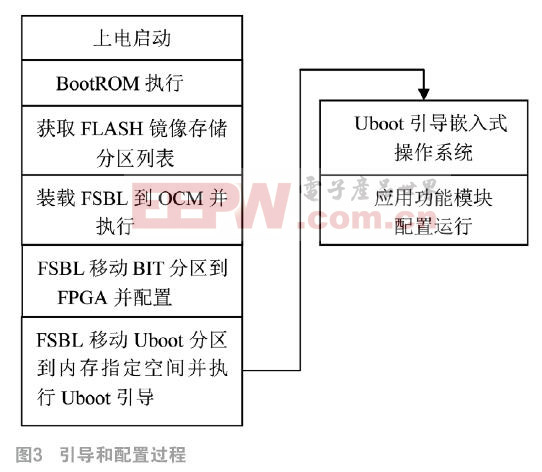

Zynq是以ARM為核心的FPGA,平臺引導時,先引導ARM核,由ARM配置引導其他部分。引導的主要內容是引導ARM的實時操作系統和FPGA的BIT配置文件。圖3是引導和配置過程的詳細列表。

在平臺的引導過程中,FSBL加載Uboot到ARM來運行,Uboot提供了ARM外設接口的驅動并完成操作系統啟動前必須的硬件初始化,之后將控制權移交給操作系統。啟動時燒寫到FLASH中的鏡像文件可由Xilinx SDK生成,鏡像文件包含FSBL的ELF格式可執行文件,FPGA代碼編譯生成的BIT文件和交叉編譯生成Uboot的ELF格式可執行文件。

3.2 平臺嵌入式實時操作系統

嵌入式操作系統采用國外引進的支持Zynq 7000系列芯片的嵌入式實時操作系統Nucleus Plus,Nucleus Plus具有實時的、搶先的、多任務的內核。95%的內核代碼由C語言編寫,移植性好,以后可以平滑移植到性能更好的平臺之上。開發人員可對Nucleus Plus操作系統進行定制修改,以適應小型化繼電保護平臺的特殊需求。

考慮到Zynq 7000 ARM雙內核的工作方式,在操作系統選型時,選擇了支持雙核SMP(對稱式)的Nucleus Plus。目前,Zynq ARM雙核在繼電保護設備應用設計中,有的采用AMP(非對稱式)方式,即核0搭建 Linux操作系統,處理實時性不高的應用,如IEC61850中的協議解析,設備屬性數據處理等;核1處理高實時性的繼電保護算法等功能,滿足繼電保護設備的實時性。相對AMP、SMP模式的操作系統具有可共享內存、較高的性能和功耗比,以及易實現負載均衡等優點,更能發揮多核處理器的硬件優勢,并且在跨處理器硬件平臺的移植開發上,更容易和快捷。

3.3 應用功能模塊

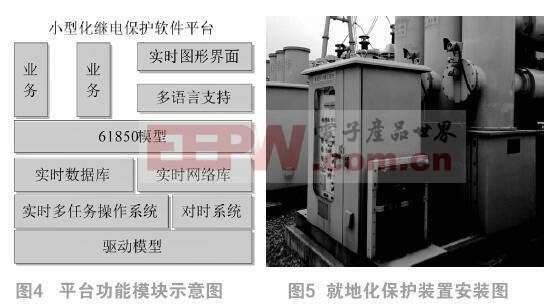

小型化繼電保護軟件平臺采用多模塊自動加載管理系統,完全實現通信管理模塊、人機接口、系統平臺、設備驅動和應用模塊的獨立編譯和下載,并在初始上電過程中,自動識別各軟件模塊,建立各模塊的初始工作環境,自動執行軟件模塊的相關操作。這樣,調試升級或系統功能變化時,只要對相關功能模塊進行升級、編譯和下載,從而將設計、調試、測試等縮小到一個有限的范圍,既縮短了開發周期,又降低了軟件開發的難度和復雜度。平臺基本功能模塊組成如圖5所示。

4 結束語

就地安裝的小型化保護裝置已經在智能變電站中有了試點應用。為了方便安裝,裝置尺寸設計大約是260mm×180mm×100mm,可以兩臺并排安裝在一次設備匯控柜側面,不需要專用屏柜。整裝置實測功耗最大不超過11W,約是常規智能保護裝置的1/4。全密閉式金屬機殼結構和免維護設計是智能變電站就地化保護設備發展趨勢。

Xilinx Zynq系列芯片已經廣泛應用在嵌入式產品的各個領域,在穩定性和可靠性上得到了多種相關產品的驗證。在此基礎上設計的小型化繼電保護平臺具有低功耗、低成本、高度集成的優點。特別是片內ARM+FPGA的架構,讓該平臺能夠靈活地拓展外設功能,使系統速度和系統資源得到充分的利用。基于該平臺的繼電保護產品能夠較好地滿足當前智能變電站保護測量設備就地化安裝的需求,降低智能變電站的建設成本。

參考文獻:

[1]劉振亞.智能電網技術[M].中國電力出版社,2010.

[2]王瑩.Xilinx可擴展處理平臺:ZYNQ嵌入式處理器與FPGA集成的獨特創舉[J].電子產品世界,2014(2):27-32.

[3]Xilinx Inc.Zynq-7000 All Programmable SoC Technical Reference Manual(v1.0),2015.

[4]何賓. Xilinx all programmable Zynq-7000 SoC[M].北京:清華大學出版社,2013.

[5]陸佳華.嵌入式系統軟硬件協同設計實戰指南[M].機械工業出版社, 2013.

本文來源于中國科技期刊《電子產品世界》2016年第11期第68頁,歡迎您寫論文時引用,并注明出處。

評論